Robustes IGBT-Modul von Mitsubishi

Feldausfälle minimieren

Fortsetzung des Artikels von Teil 1

Thermische Überlegungen

In der Regel steigt die Ausfallrate eines Halbleiterbausteins mit zunehmender Betriebstemperatur (siehe MIL-HDBK-217F). Dabei ist der Temperaturfaktor der Ausfallrate πT für einen npn-Siliziumtransistor nach der folgenden Gleichung bei einer Sperrschichttemperatur TJ von +150 °C um den Faktor 1,37 höher als bei +125 °C (siehe Tabelle 1).

Jobangebote+ passend zum Thema

TJ | πT | Relation |

|---|---|---|

+125 °C | 5,94 | 1,00 |

+150 °C | 8,14 | 1,37 |

Tabelle 1: Temperaturfaktor der Ausfallrate

Es ist also wichtig, die Einsatzgrenzen seines Designs genau zu verstehen und entsprechende Auslegungsreserven zum Schutz gegen hohe Temperaturen der Leistungshalbleitermodule vorzusehen. Insbesondere sind thermische Instabilitäten beim Einsatz von HV-IGBTs und Betrieb unter hoher Temperatur zu verhindern. Es ist darauf zu achten, dass sowohl die im Halbleitermodul verwendeten Stoffe, als auch die beim Assemblieren der Module im Umrichter gewählten Materialien unter solchen Betriebsbedingungen im späteren Einsatz stabil bleiben.

Eine wirksame Methode zum Schutz gegen thermische Instabilitäten ist die Verringerung des Sperrstroms ICES bei hohen Temperaturen. Der Sperrstrom eines Leistungshalbleiterchips lässt sich verringern, indem die folgenden Designstrategien genutzt werden:

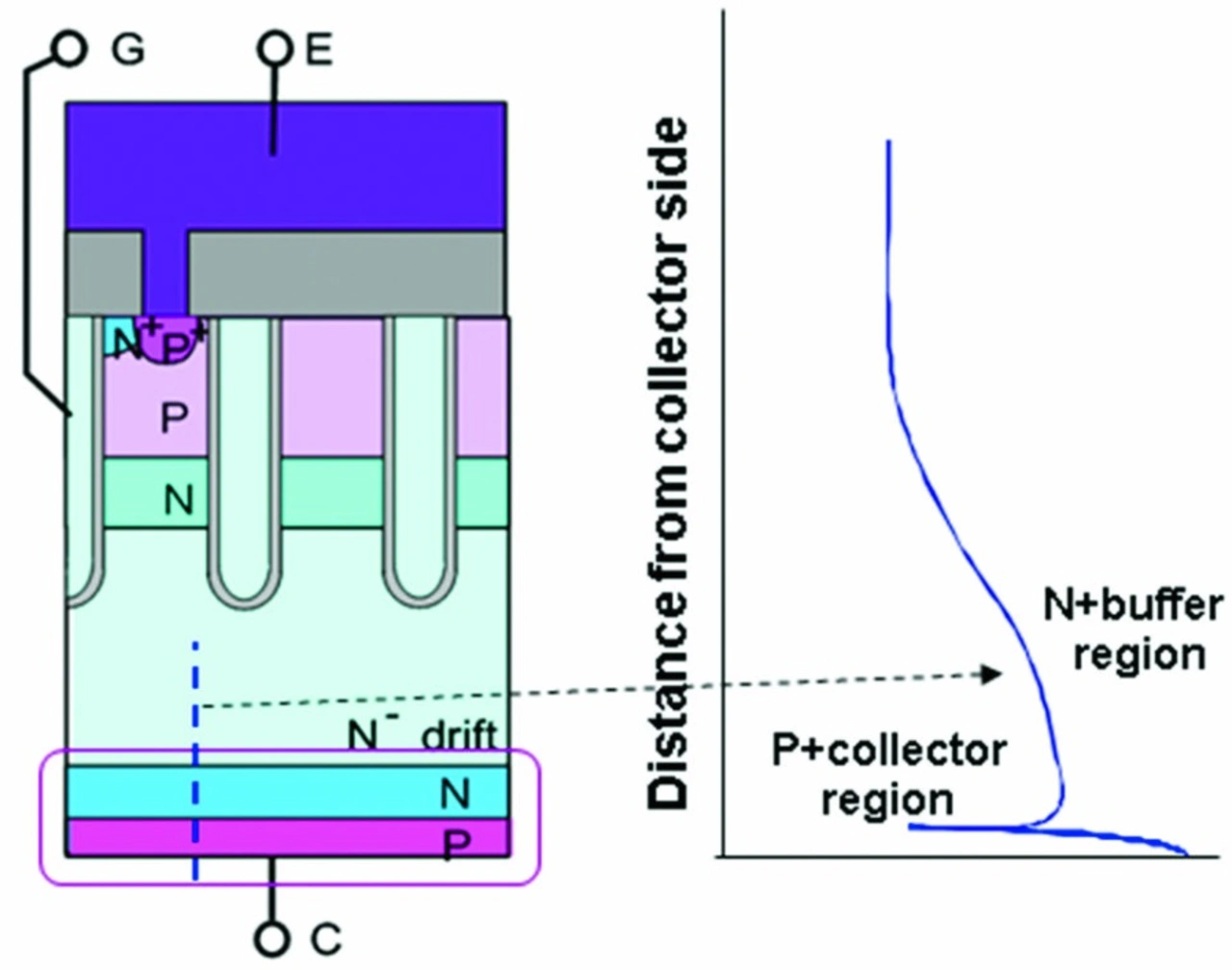

- Nutzung eines optimierten n-Buffer-Layer-Profils (Bild 4),

- Optimierung der Lebensdauerkontrolle in der n-Drift-Region,

- Schaffung einer passenden Abschlussstruktur am Rand des Chips (Bild 1, [7]) und

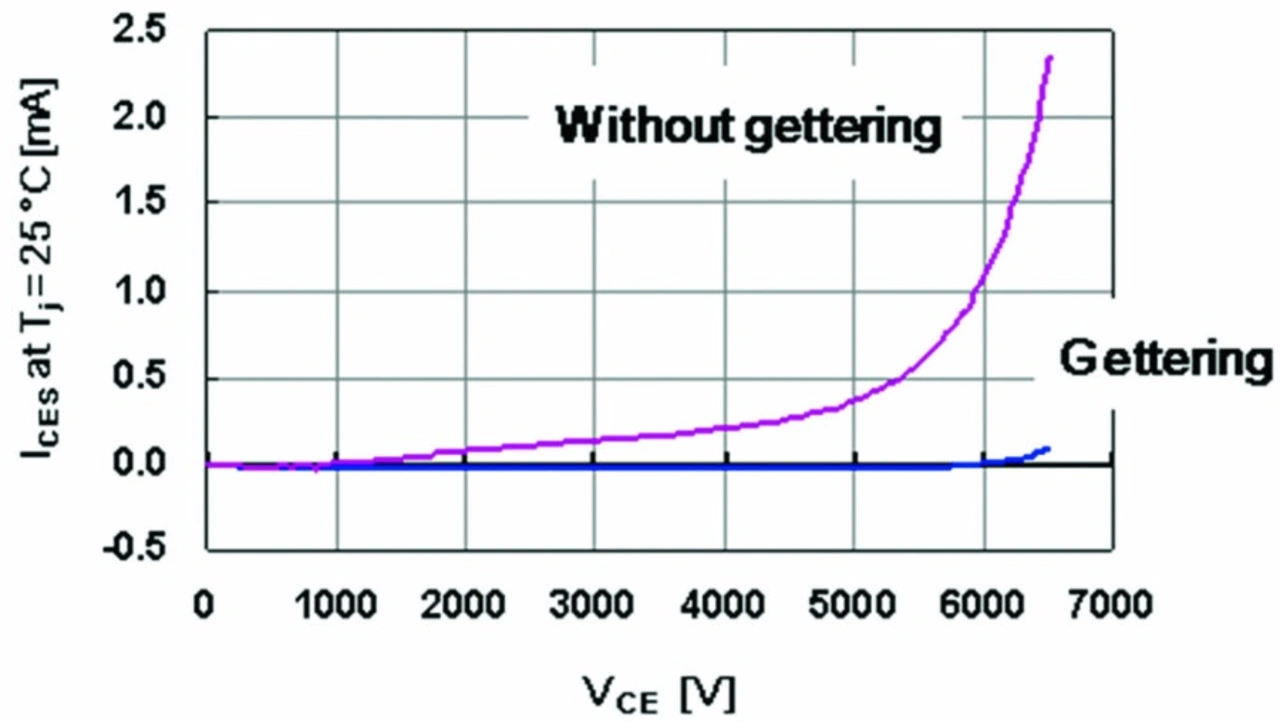

- Gettering-Wafer-Prozesses, um das Auftreten von durch Verunreinigung verursachten Kristalldefekten im Silizium zu minimieren (Bild 5).

Durch Einsatz der oben genannten Techniken lässt sich im neu entwickelten IGBT-Modul für 1000 A/6500 V der Sperrstrom ICES bei +150 °C auf den gleichen Wert wie bei einem herkömmlichen Modul bei +125 °C reduzieren.

Eine wichtige Eigenschaft isoliert aufgebauter Leistungshalbleitermodule ist der Einfluss des Teilentladungsverhaltens auf die Stabilität der Isolation. Die Sicherung eines guten Isolationsverhaltens bei hohen Spannungen über lange Zeiträume erfordert ein Designkonzept, welches das Entstehen von Teilentladungen nach Belastung mit hoher Temperatur ausschließt. Dafür verwendet Mitsubishi ein besonderes Silikongel, das über ein stabiles Isolationsvermögen über den gesamten zulässigen Betriebstemperaturbereich verfügt. Um eine gute Teilentladungsfestigkeit zu gewährleisten, wird zur Optimierung des Gels ein besonderer Injektionsprozess verwendet, um Luftblasen darin zu minimieren.

Beim Einsatz in der Bahntechnik beispielsweise ist eine Kontrolle von Umgebungstemperatur und Luftfeuchtigkeit rund um die Leistungshalbleitermodule schwierig. Robuste, gegen hohe Feuchtigkeit bei hohen Spannungen geschützte Designs sind eine effektive Maßnahme zur Sicherung der erforderlichen Qualität der IGBT-Module.

Der Schutz gegen hohe Feuchtigkeit lässt sich durch ein Design mit einer geeigneten Abschlussstruktur am Rand des Chips verbessern, welche die Wahrscheinlichkeit einer Akkumulierung von Oberflächenladungen (Qss) am Guard-Ring verringert. Solche Oberflächenladungen können auftreten, wenn eine hohe Spannung zwischen Kollektor und Emitter anliegt. Die Ladungsmenge Qss am Guard-Ring beeinflusst vor allem die Sperrspannungsfestigkeit des Chips. Durch Aufbringen halb isolierender Passivierungsfilmmaterialien durch entsprechende Prozesse haben die Entwickler die Wahrscheinlichkeit einer Akkumulierung von Qss an der Abschlussstruktur am Chiprand reduziert. Durch diese gezielten Maßnahmen konnte Mitsubishi Electric einer Zunahme des Sperrstroms ICES bei anliegender hohen Blockierspannungen unter erschwerten Einsatzbedingungen (z. B. bei Kondensatbildung) entgegenwirken.

Die DC-Langzeitstabilität (Long-Term DC Stability, LTDS) ist ein Maß für die Unempfindlichkeit eines Leistungshalbleiters gegenüber kosmischer Strahlung, ein zentraler Aspekt des HV-IGBT-Designs. Dank seiner LPT-Struktur (Light Punch Through) auf der Kollektor-Seite sowie aufgrund der bereits beschriebenen Maßnahmen zur Verringerung des Sperrstroms ICES ist eine gute DC-Langzeitstabilität gewährleistet [7].

- Feldausfälle minimieren

- Thermische Überlegungen

- Verifizierung des Designs

- Erschwerte Einsatzbedingungen