IMEC Technology Forum 2015:

Europäische Spitzenforschung in der Mikroelektronik für die Welt

Fortsetzung des Artikels von Teil 2

Kleinere Transistoren mit EUV-Lithografie

Mit anschwellenden Datenströmen steigen freilich auch die Ansprüche an die Chips, die immer mehr Rechenleistung und Datenübertragungsleistung bringen müssen. Das geht nur mit immer mehr und kleineren Transistoren. Lip Bu Tan von Cadence schilderte in seinem Vortrag die Problematik der mit zunehmender Miniaturisierung ansteigenden Komplexität beim IC-Entwurf, die auch EDA-Tools vor immer größere Herausforderungen stellt. Die Entwurfsregeln nehmen zu und erfordern zur Einhaltung immer mehr Rechenoperationen. Cadence begegnet dem mit massiv parallel arbeitenden Design Tools, sodass sich die Synthesegeschwindigkeit bis um den Faktor 5 steigern und die Zahl der Iterationen auf Unit- und Blockebene um 50 Prozent reduzieren lässt. Dabei gibt es drei Ebenen der Parallelverarbeitung mit einem adaptivem Scheduling, das die Hardware optimal nutzen soll. Zusammen mit IMEC hat Cadence einen 7-nm-Chipentwurf mit Mehrfachstrukturierung (Multiple Patterning) bereits 2014 bis zum Tape-out gebracht und für EUV-Lithografie im laufenden Jahr. Derzeit arbeiten beide bei EDA-Werkzeugen für 5-nm-Strukturen zusammen.

Jobangebote+ passend zum Thema

Peter Wennink, President und CEO von ASML (Bild 5), stellte fest, dass Moore’s Law kein Naturgesetz sei, und fragte ketzerisch, ob es überhaupt sinnvoll ist, weiter zu skalieren? „Ist es ökonomisch sinnvoll und schaffen wir es, robuste Lösungen zu realisieren?“ Tatsächlich explodiert der Lithografie- und der anschließende Metrologie-Aufwand überproportional mit klassischer UV-Lithografie (193 nm) von typisch acht Maskenschritten bei 20 nm über 23 bei 10 nm auf 34 bei 7 nm. Multi-Patterning-Ansätze stoßen hier an ihre Grenzen. Wennink hat allerdings einen Lösungsvorschlag parat. Wenn man bei 7 nm auf Extrem-UV umsteigt, dann wird die Zahl der Maskenschritte mit neun wieder überschaubar. Bei der Produktivität habe ASML ein Etappenziel erreicht, die Belichtung von 1022 Wafern in 24 Stunden mit einer 80-W-EUV-Lichtquelle. Eine 110-W-Lichtquelle konnte auch bereits demonstriert werden. EUV eröffne die Möglichkeit, wieder auf den historischen Pfad der sinkenden Kosten pro Funktion zurückzukehren, den man mit der hohen Prozesskomplexität beim Multi-Patterning verlassen hatte.

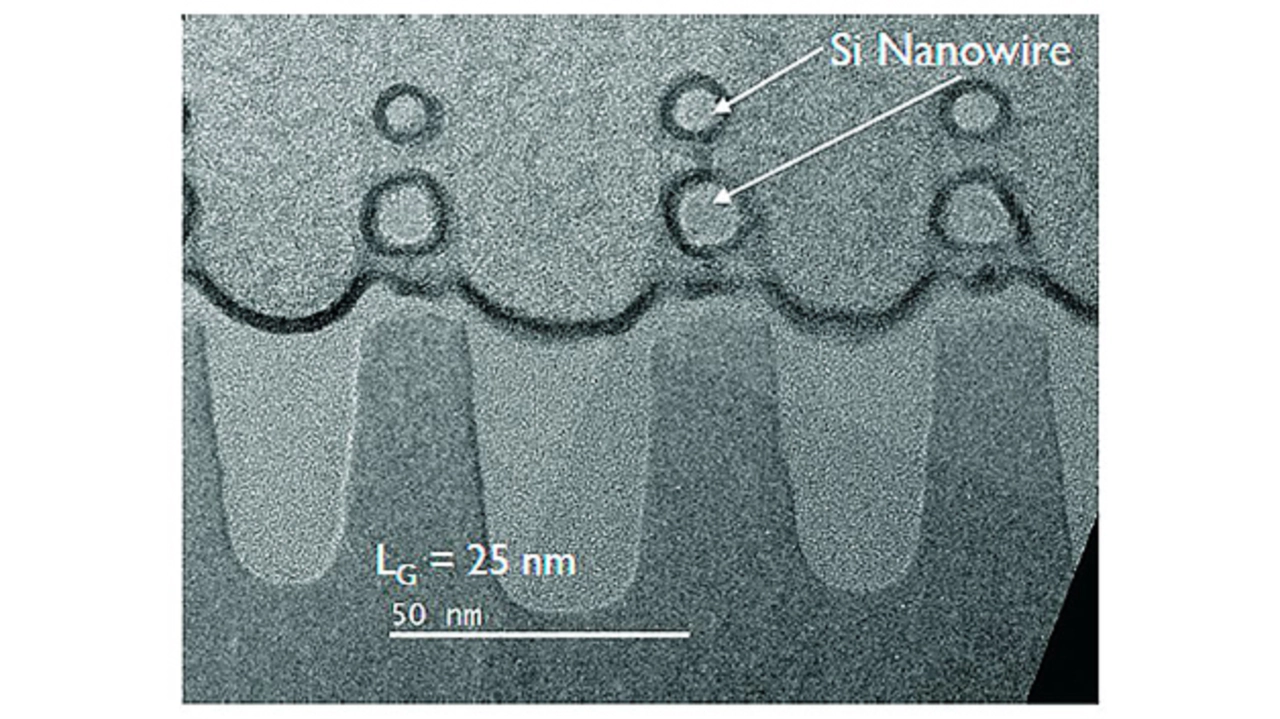

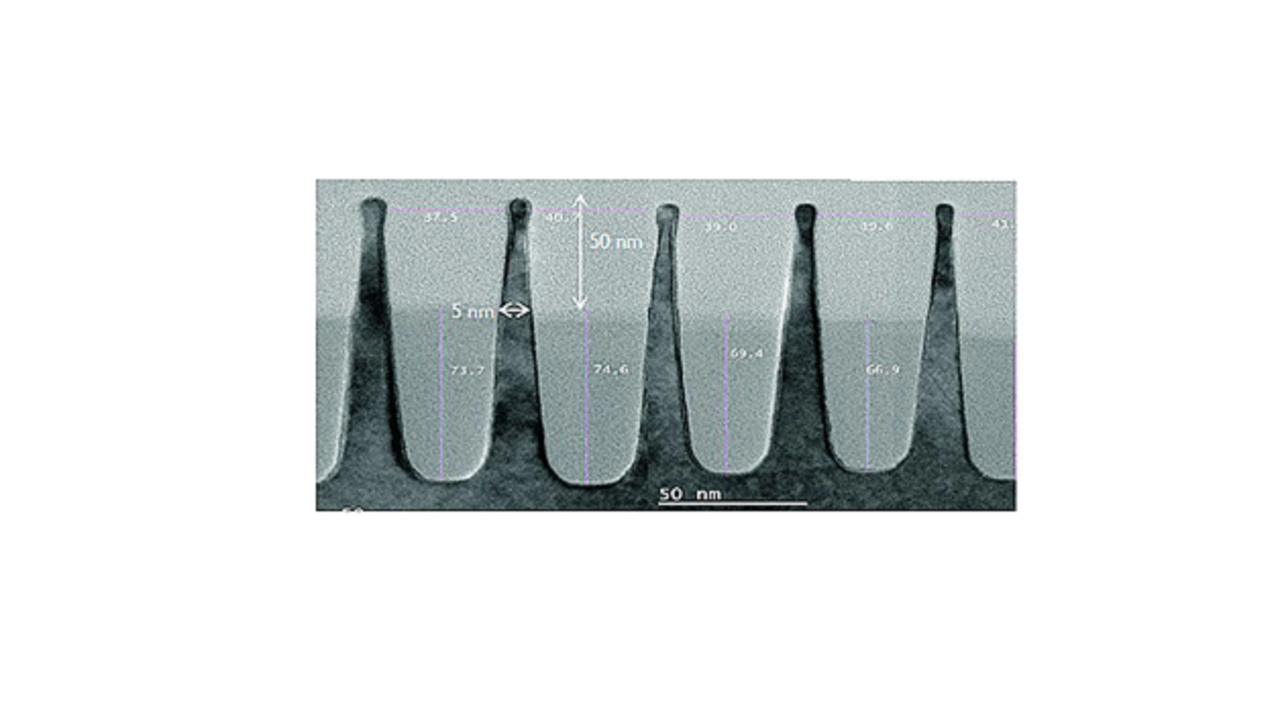

Will man die Infrastruktur für das Internet der Dinge schaffen, dann führt laut An Steegen, SVP für Prozesstechnik beim IMEC, kein Weg an weiterentwickelten Transistorstrukturen vorbei. Sie zeigte dabei verschiedene Ansätze auf, an denen im IMEC gearbeitet wird. Beispielsweise versprechen hohe Finnen (bei FinFETs) eine höhere Leistungsfähigkeit (Bild 6a), genauso wie Ge/SiGe-FinFETs durch ihre höhere Ladungsträgermobilität im Kanal. Laterale Nanowire-FETs (Bild 6b) verbessern die elektrostatischen Eigenschaften, genauso wie vertikale Nanowire-FETs.

STMicroelectronics hingegen setzt nicht auf FinFETs, sondern auf FD-SOI (Fully depleted Silicon on Insulator), einen planaren Halbleiterprozess, wie Jean-Marc Chery, Chief Operating Officer von STMicroelectronics, in seinem Vortrag erklärte. Damit lasse sich die Leistungsaufnahme eines Chip für eine Ultra-low-Power-Anwendung von 34 mW, gefertigt in einem 40-nm-Low-Power-Prozess, auf unter 10 mW bringen, gefertigt in FD-SOI mit 28 nm. Bei einem Videoanalyse-Lockstep-Prozessor für Automobile, hergestellt in 28-nm-Bulk-Prozesstechnik, konnte durch den Wechsel auf FD-SOI mit ebenfalls 28 nm die Leistungsaufnahme von 5 W auf 3 W gesenkt werden – allerdings auch ohne Lockstep, sondern mit einer optimierten Sicherheitsarchitektur.

- Europäische Spitzenforschung in der Mikroelektronik für die Welt

- "Heiliger Gral des Verkehrwesens" - Autonomes Fahren

- Kleinere Transistoren mit EUV-Lithografie