CadenceLIVE Europe 2020

Verifikationseffizienz auf Chipebene bis zum Faktor 10 gesteigert

Cadence bringt Verifikations-IP auf die Chip-Ebene. Damit erzielt die »System VIP«-Lösung eine bis zu zehnfach höhere Effizienz bei der Einrichtung, Ausführung und Analyse von Testbenches auf Systemebene für Hyperscale-, Automotive-, Mobilfunk- und Consumer-Chips.

Der im kalifornischen San Jose ansässige Anbieter von EDA-Tools Cadence Design Systems hat auf der seiner Europa-Konferenz CadenceLIVE 2020 mit »Cadence System-Level Verification IP« (System VIP), eine neue Suite mit Tools und Bibliotheken für die Automatisierung der Einrichtung von System-on-Chip (SoC) Testbenches, Bus- und CPU-Traffic-Generation, Cache-Kohärenz-Validierung und die Analyse von System-Peformance Engapaessen vorgestellt. Mit Hilfe von Cadence System VIP können Kunden, die komplexe Hyperscale-, Automotive-, Mobilfunk- und Consumer-Chips entwickeln, die Verifikationseffizienz auf Chip-Ebene um das bis zu Zehnfache steigern.

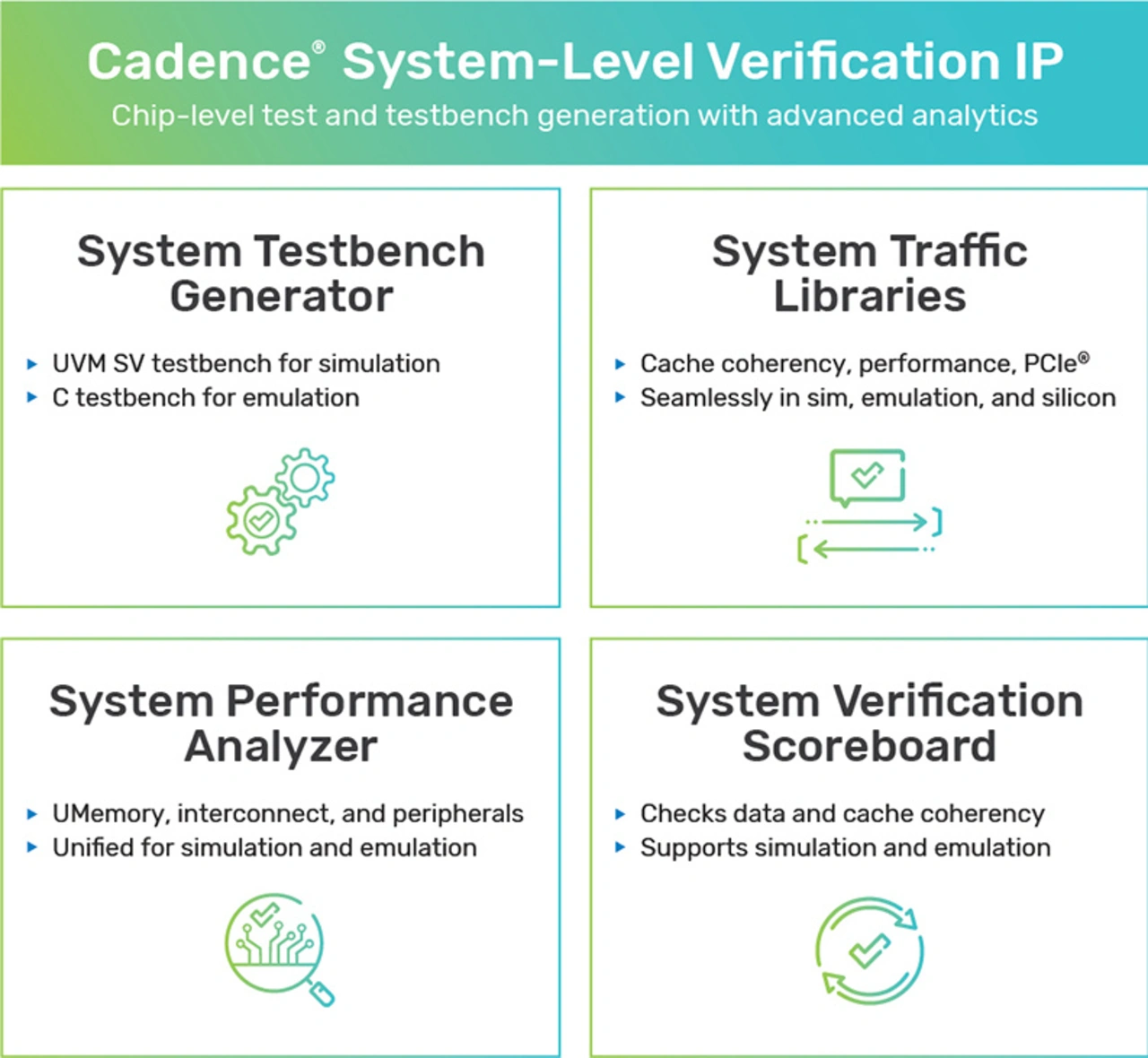

Mit der neuen System-VIP-Lösung erweitert Cadence sein Angebot im Bereich der Verifikationsautomatisierung auf IP-Ebene nun auf die Chip-Ebene. Die mit der System-VIP-Lösung erstellten Tests lassen sich auf Cadence Simulations-, Emulations- und Prototyping-Engines portieren und können auch für ein Post-Silicon-Bring-up erweitern. Cadence System VIP umfasst vier neue Tools und Bibliotheken:

- System Testbench Generator: Erlaubt den Anwendern die automatische Erstellung von SoC-Testbenches mit komplexen Speicher-, Cache-, Schnittstellen- und Bus-Konfigurationen

- System Traffic Libraries: Stellt dem Anwender ein umfangreiches Portfolio von vordefinierten Tests zur Verfügung, die in eine System-VIP-Testbench eingefügt werden können, einschließlich von Kohärenz-, Performance-, PCI Express- (PCIe) und NVMe-Subsystemen

- System Performance Analyzer: Erlaubt umfassende Berichte und Visualisierungen von Leistungsfähigkeits-Analysen für Speicher-Subsysteme, Verbindungen und Peripherie

- System Verification Scoreboard: Ermöglicht umfassende Daten- und Cache-Kohärenz-Prüfungen auf kohärenten Verbindungen, Speicher und Peripherie.

Jobangebote+ passend zum Thema

Erfolgreiche Erprobung bei Renesas und Arm

»Renesas hat Cadence VIP seit vielen Jahren im Einsatz und schätzt die führende Position von Cadence bei fortschrittlichen SoC-Verifikationstechnologien«, kommentiert Tetsuya Asano, Director, Design Methodology Department, Shared R&D EDA Division bei Renesas. »Durch die Erweiterung unserer vorhandenen Verifikationsumgebung auf der Basis von Xcelium und Palladium mit dem neuen System-VIP und die Verbesserung der Stimulus-Wiederverwendung und Automatisierung konnten wir den SoC-Verifikationsprozess durch eine um den Faktor 10 höhere Effizienz weiter beschleunigen, so dass wir unsere innovativen, hochwertigen Produkte schneller an unsere Kunden liefern können.«

»Arm hat gemeinsam mit Cadence die Bring-up-Dauer für die SoC-Verifikation und die Performance-Verifikation reduziert. Dies ermöglicht neue Wege bei der Entwicklung von CPU-Architekturen, wodurch künftige Prozessoren robuster werden und sich bestimmte Sicherheitslücken vermeiden lassen«, erklärt Tran Nguyen, Director of Design Services bei Arm. »Durch den Einsatz des Cadence-VIP-Systems für die DDR-Performance-Analyse in Verbindung mit der PCIe-System-Traffic-Bibliothek konnte Arm das Bring-up einer komplexen Systemverifikation in wenigen Tagen abschließen, während der manuelle Prozess bisher mehrere Wochen erfordert hat.«

»Die Verifikationsherausforderungen steigen exponentiell, da die Anzahl und Komplexität der integrierten IP-Blöcke in einem SoC zunehmen«, erläutert Paul Cunningham, Corporate Vice President und General Manager der System & Verification Group von Cadence. »Unsere neue Cadence System VIP Solution kann den Verifikationsdurchsatz durch die Automatisierung von einigen kritischen arbeitsintensiven Verifikationsherausforderungen auf Chip-Ebene drastisch erhöhen.«

Die System-VIP-Tool-Suite ist Teil der umfassenden Verification Suite von Cadence und unterstützt die Intelligent-System-Design-Strategie des Unternehmens. Die Cadence Verification Suite besteht aus Core Engines und intelligenten Verifikationstechnologien, die den Verifikationsdurchsatz und die Design-Qualität erhöhen sowie die Verifikationsanforderungen für unterschiedlichste Anwendungen und vertikale Segmente erfüllen.

- Verifikationseffizienz auf Chipebene bis zum Faktor 10 gesteigert

- Genaue EMV-Simulation senkt Prototypenaufwand