IEDM 2016, San Francisco

7-nm-CMOS-Plattformen mit FinFETs

Die Skalierung von Halbleitern geht weiter. Auf der IEDM 2016 wurden zwei Papers präsentiert, die komplette 7-nm-FinFET-CMOS-Plattformen zeigen. Während TSMC noch auf konventionelle Lithographie setzt, basiert die Plattform der Allianz IBM/Global/Foundries auf Lithographie mit extremem UV-Licht.

Für Technologien auf Transistor-Ebene ist das International Electron Devices Meeting die weltweit wichtigste Konferenz. Im Hilton San Francisco Union Square Hotel versammelten sich 1620 Halbleiterexperten aus der ganzen Welt, um sich auf den neuesten Stand in der Nanoelektronik zu bringen. Zwei spät eingereichte Papers dokumentieren dabei den aktuellen Stand in der CMOS-Skalierung.

FinFETs sind Hochleistungstransistorstrukturen, mit denen sich hochdichte, leistungsfähige ICs realisieren lassen. Sie sind gekennzeichnet durch eine mehrseitige Gate-Struktur, die einen Fin-förmigen Kanal umschließt, so dass sich der Transistor selbst bei Nanostrukturen präzise steuern lässt. Die derzeit modernsten FinFETs in der Halbleiterproduktion liegen beim 14/16-nm-Knoten.

In zwei spät eingereichten Papers enthüllten TSMC und die Allianz IBM/GlobalFoundries/Samsung ihre kommende 7-nm-FinFET-Technologie-Plattform. Der Umstieg auf den7-nm-Knoten belegt eindrucksvoll, dass die CMOS-Skalierung weitergeht. In der Produktion dürfte der 7-nm-Knoten allerdings erst 2018 oder später ankommen.

Jobangebote+ passend zum Thema

7-nm-CMOS-Plattformen auf der IEDM 2016

- 7-nm-CMOS-Plattformen mit FinFETs

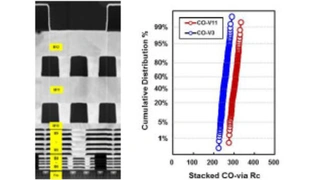

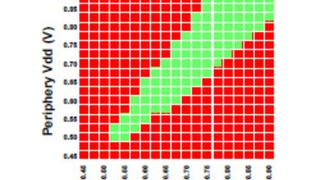

- TSMCs 7-nm-CMOS-Plattform für Mobilanwendungen

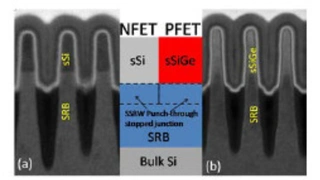

- Allianz IBM/GlobalFoundries/Samsung setzt auf EUV