IEDM 2016, San Francisco

7-nm-CMOS-Plattformen mit FinFETs

Fortsetzung des Artikels von Teil 2

Allianz IBM/GlobalFoundries/Samsung setzt auf EUV

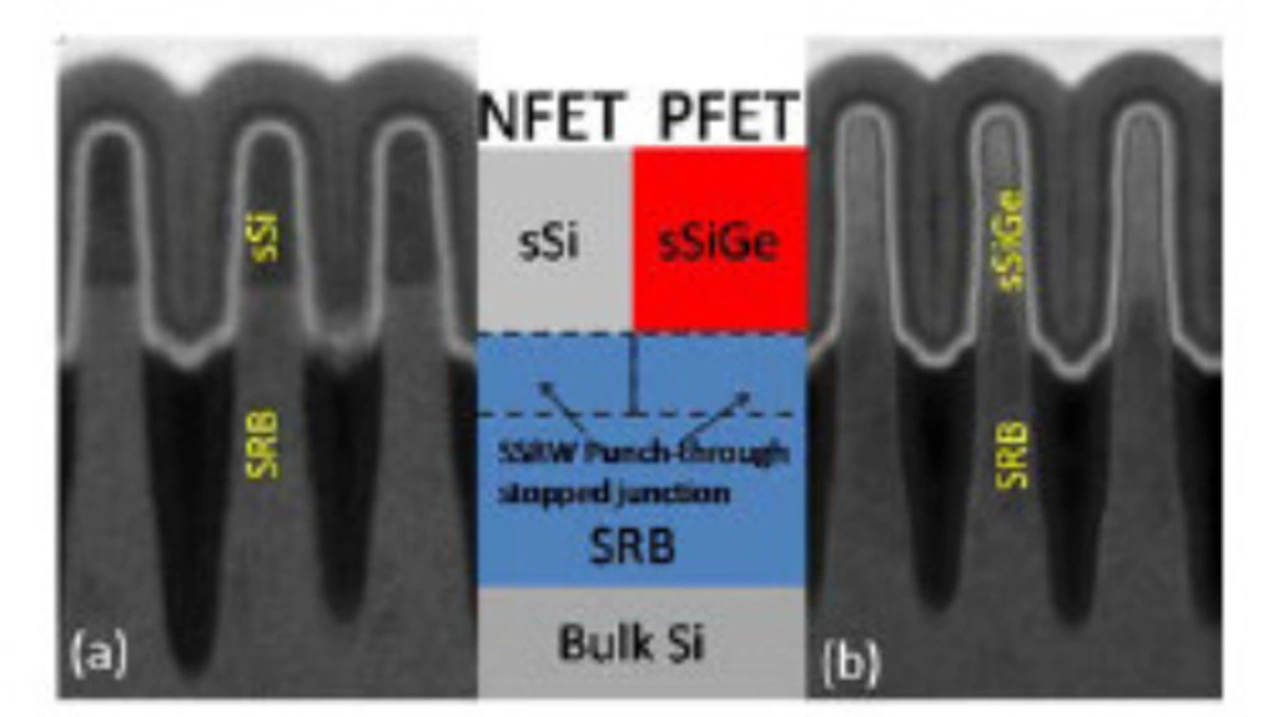

Der 7-nm-FinFET-Prozess, den die Allianz IBM/GlobalFoundries/Samsung auf der IEDM vorgestellt hat, ist die erste integrierte Prozessplattform, die extremes UV-Licht (EUV) zur Strukturierung der Transistoren nutzt. Schon lange wurde erwartet, dass es bei der Abbildung kleinster Strukturen nicht mehr ohne EUV-Lithographie gehen wird, denn die Wellenlänge von EUV ist mit 13,5 nm deutlich kürzer als die in konventionellen Belichtungsmaschinen gebräuchlichen 193 nm. Mit EUV ist es der Allianz gelungen, die engsten kontaktierten Polysilizium-Pitches mit 44/48 nm und Metallisierungs-Pitches von 36 nm herzustellen, ein neuer Rekord bei FinFETs. Der Prozess umfasst doppelt vorgespannte Transistorkanäle (dual strained channels), die auf einer dicken spannungsreduzierenden Pufferschicht (Strain Relaxed Buffer – SRB) als virtuellem Substrat dazu dienen, auseinandergezogene NMOS- und komprimierte SiGe-PMOS-Transistorstrukturen aufzubringen, die den Treiberstrom um 11 bzw. 20 Prozent steigern, verglichen mit einem planaren HKMG-Prozess. Ein weiteres Merkmal ist ein neues Trench-Epitaxie-Verfahren, das die Widerstände der stark skalierten Kontaktregionen minimiert.

Jobangebote+ passend zum Thema

Der Prozess umfasst doppelt vorgespannte Transistorkanäle (dual strained channels), die auf einer dicken spannungsreduzierenden Pufferschicht (Strain Relaxed Buffer – SRB) als virtuellem Substrat dazu dienen, auseinandergezogene NMOS- und komprimierte SiGe-PMOS-Transistorstrukturen aufzubringen, die den Treiberstrom um 11 bzw. 20 Prozent steigern, verglichen mit einem planaren HKMG-Prozess. Ein weiteres Merkmal ist ein neues Trench-Epitaxie-Verfahren, das die Widerstände der stark skalierten Kontaktregionen minimiert.

- 7-nm-CMOS-Plattformen mit FinFETs

- TSMCs 7-nm-CMOS-Plattform für Mobilanwendungen

- Allianz IBM/GlobalFoundries/Samsung setzt auf EUV