Mobile Health ohne Kompromisse

Das richtige ASIC-Design für medizinische Wearables

Individuelle ASICs ermöglichen es MedTech-OEMs, Funktion und Anforderungen von mobilen Medizingeräten besser abzuwägen – gerade wenn Energiebudget, Funktion und Formfaktor in engen Grenzen gehalten werden müssen. Wie Hersteller und Zulieferer den geeignetesten ASIC-Ansatz finden und abwägen.

Wearables für Gesundheits-Anwendungen stellen eine große Marktchance dar - sowohl für Medizintechnik-Firmen wie auch MedTech-Zulieferer. Als Grundlage der personalisierten Medizin reichen die möglichen Designs von intelligenten Pflastern über Überwachungsgeräte am Handgelenk bis hin zu therapeutischen Systemen.

Für Entwickler und Ingenieure sind die medizinischen Wearbales jedoch eine Herausforderung: Genauigkeit der Messdaten, Energieverbrauch, Größe und Kosten sind bei den meist mobilen Gesundheitsgeräten schwer auszubalancieren. Und obwohl jeder dieser Faktoren einen hohen Einfluss auf das Hardware-Design hat, konzentrieren sich die meisten Kompromisse auf das Energieprofil des Geräts. Wie sich der Energieverbrauch mit jeder Aktivität der Wearables ändert, bestimmt häufig die systemrelevanten Entscheidungen über den Aufbau und das Ausmaß - und ist damit maßgeblich dafür, wie das MedTech-Design die anderen Kriterien erfüllen kann.

Abwägung 1: »Always on« kontra Batteriegröße

Die Kapazität der Batterie bzw. des Akkus schränkt die Energie ein, die dem Gerät zugeführt werden kann. Batterielose Designs, die Energy Harvesting setzen, sind noch stärker eingeschränkt. Die Energiebegrenzung wirkt sich auf mehrere Aspekte des Designs aus. Aus Sicht des Systemdesigns ist die Entscheidung über den Arbeitszyklus diejenige mit den größten Auswirkungen auf allen Ebenen.

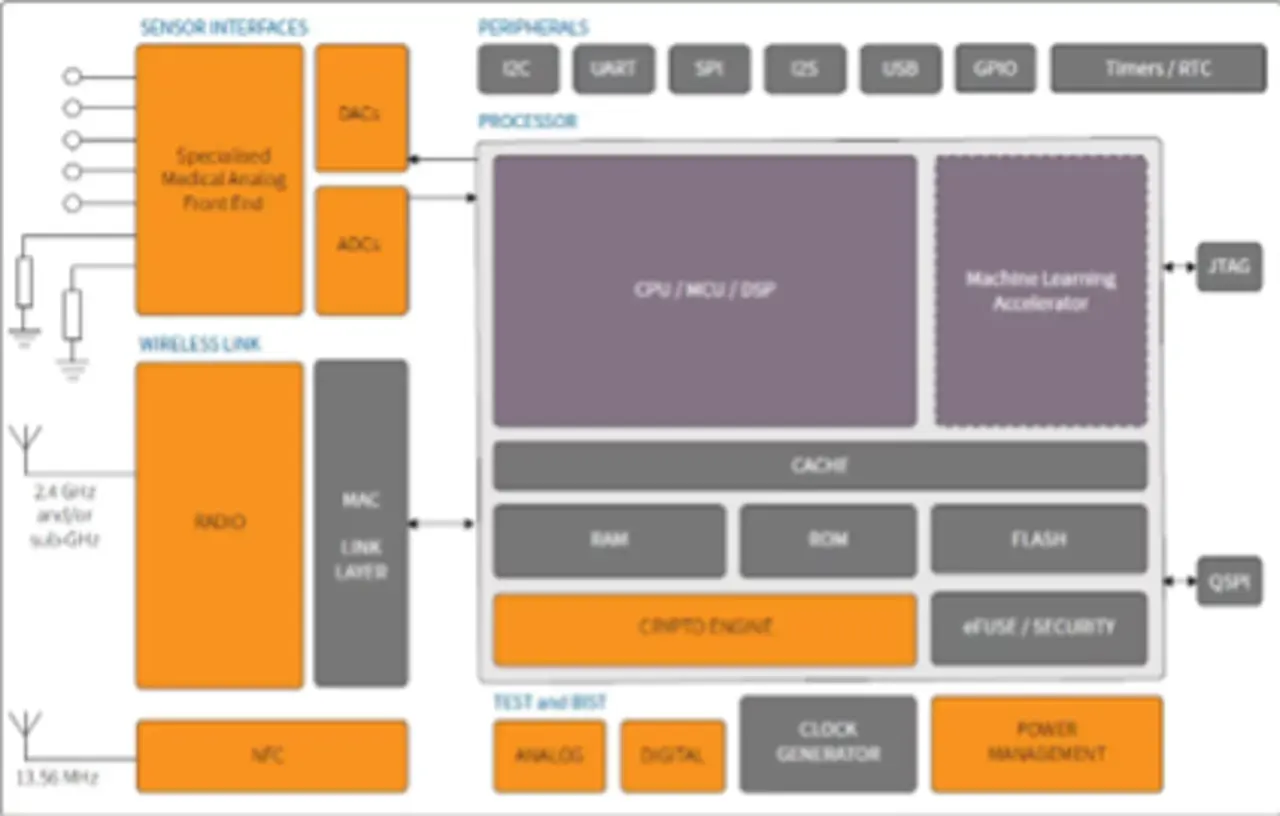

Obwohl viele Geräte im Gesundheitsbereich als »immer eingeschaltet« (always-on) fungieren, stellt ein effizientes Design sicher, dass der Großteil der Schaltkreise in einem niedrigen Arbeitszyklus verbleibt – im Ruhezustand und so lange wie möglich ausgeschaltet, bevor sie in Aktion treten. Bei modernen Halbleitertechnologien ist Power Gating unverzichtbar, um den ständig fließenden Leckstrom in stromführenden Transistoren zu verhindern. Durch mehrere Takt- und Stromversorgungsdomänen wird heute sichergestellt, dass nur die Subsysteme mit Strom versorgt werden, die ihn zum richtigen Zeitpunkt benötigen.

Ein energieeffizienter Timer und Speicherpuffer,

der die Frontend-Schaltkreise regelmäßig aktiviert, ist oft der einzige Teil des Systems, der ständig aktiv ist, um eine Datenwandlung durchzuführen und die Daten in den Puffer zu verschieben. Schaltkreise oder Firmware können die eingehenden Daten überwachen, um festzustellen, ob bestimmte Schwellenwerte überschritten wurden oder ob der Puffer voll ist. Ist dies der Fall, kann die Logik einen Zustandsübergang auslösen, der einen übergeordneten Mikrocontroller zur Analyse der Daten aktiviert. Die auf dieser Ebene getroffenen Entscheidungen können dazu führen, dass weitere Teile des Systems aktiviert werden, um weitere Maßnahmen zu ergreifen. Diese Aktion kann in Form einer Weiterleitung von Daten an ein anderes IoMT-Gerät oder einen Smartphone-Host über Bluetooth erfolgen.

Obwohl sich die Ruhezustand- und Betriebszyklen auf Software- oder Firmware-Ebene verwalten lassen, ist dies nicht unbedingt optimal für die Energieeffizienz. Dies ist einer der Gründe, warum ein Frontend-ASIC einen erheblichen Vorteil bietet, wenn der Stromverbrauch des Gesamtsystems betrachtet wird. Ein Frontend-ASIC bietet die Möglichkeit, die Steuerung von Stromversorgungszuständen fein abzustimmen, die in den vordefinierten Zuständen eines gängigen Frontend-Datenwandlers möglicherweise nicht zur Verfügung stehen.

| ASIC Vorteile |

|---|

|

Abwägung 2: Leistungsfähigkeit kontra Batteriegröße

Viele hochauflösende A/D-Wandler basieren auf einer Sigma-Delta-Funktion. Dabei tauscht ein digitaler Filterabschnitt die Abtastrate gegen die Auflösung einer einfachen analogen Eingangsstufe ein. Dies ist ein Ansatz, der bei modernen Halbleiterprozessen eine hohe Genauigkeit und einen großen Dynamikbereich zu relativ geringen Kosten bietet. Der hohe Dynamikbereich trägt dazu bei, Störungen in medizintechnischen Geräten zu bewältigen, bei denen oft ein erhebliches Rauschen dem Signal von Interesse beigemischt ist.

Die digitale Signalverarbeitung der erfassten Daten

durch einen leistungsstarken Prozessor kann einen Großteil des Rauschens und der Störer aus einem möglicherweise kleinen Signal von Interesse herausfiltern. Leider führt diese Strategie zu einem System mit hohem Stromverbrauch. Nicht nur für die Überabtastung und Filterung durch den DSP wird viel Energie benötigt, sondern auch für die umfangreiche digitale Nachbearbeitung auf dem Host-Mikrocontroller, der unter Umständen bei jeder Erfassung aktiv sein muss.

Dieses Problem wird durch die hohe Latenzzeit von Sigma-Delta-Wandlern noch verschärft, wenn Dezimierungsfilter für eine hohe Auflösung hochskaliert werden. Die Zeit, die benötigt wird, um jeden Block von Abtastwerten ab dem Beginn der Erfassungssequenz zu erhalten, kann zu einem Anstieg des Tastverhältnis des Host-Mikrocontrollers/Systems führen.

Eine energieeffizientere Lösung besteht darin, sich auf die Behandlung von Störungen näher an der Quelle zu konzentrieren. Dabei kommen Mixed-Signal-Schaltungen zum Einsatz, um häufige Rauschquellen zu beseitigen, so dass ein saubereres Signal mit niedrigerer Rate an den Host-Mikrocontroller weitergeleitet wird. Bei dieser Art von Design wird häufig ein kundenspezifischer DSP auf dem ASIC eingesetzt, um die digitale Filterung des überabgetasteten Signals für zwei Zwecke durchzuführen. Werden die Auswirkungen großer Störsignale an der Quelle beseitigt, lässt sich der Dynamikbereich des A/D-Wandler verringern. Zweitens kann das gefilterte Signal mit einer niedrigeren Abtastrate an den Mikroprozessor übertragen werden, was die Schaltungsaktivität und damit den Stromverbrauch reduziert.

Weitere Einsparungen lassen sich erzielen,

indem einige Ausgangssignale im Speicher des ASIC gepuffert werden und der Mikrocontroller in unregelmäßigen Abständen aktiviert wird, um sie auszulesen und zu verarbeiten. Im Grenzbereich können nur bestimmte Signalmerkmale oder Ereignisse, z. B. ein abnormaler Herzfrequenzwert, übertragen und protokolliert oder das System für weitere Maßnahmen aktiviert werden. Da die Ausgangsabtastrate jetzt niedrig ist, lassen sich weitere Stromeinsparungen erzielen, indem die Ausgangsabtastwerte im Speicher des ASIC abgelegt werden und der Mikrocontroller nur sehr selten zum Auslesen aktiviert wird.

Da ein hoher Dynamikbereich eher nicht erforderlich ist, kann der resultierende ASIC einen weit weniger energieintensiven Wanderschaltkreis verwenden. Es kann immer noch ein Sigma-Delta-Wandler sein – aber einer, der eine einfachere Dezimierungsfilterstufe mit geringerer Latenz verwendet. Ein solches Design hat einen kürzeren Startup-Overhead, der sich für schnellere Ein- und Ausschaltzyklen oder Multiplexing über Eingangskanäle eignet. Eine weitere Option ist ein SAR-Wandler (Sukzessive Approximation), der insgesamt zu einer höheren Energieeffizienz beiträgt. Bei sich langsam ändernden Eingängen bietet eine ladungsintegrierende Schaltung die beste Kombination aus Energieverbrauch, Auflösung und Erfassungsrate.

Abwägung 3: Funktion kontra Formfaktor?

Ein Merkmal von Frontend-ASICs ist, dass sie sehr platzsparend sein können. In der Regel misst der Chip weniger als 3 mm x 3 mm, wodurch sich die Bauteile sehr gut für die kleinen Abmessungen von Wearables im Gesundheitswesen eignen. Chip-Scale-Gehäuse nutzen die Kompaktheit des ASIC zwar voll aus, führen jedoch zu einer begrenzten Zahl von I/Os. Dies steht im Gegensatz zum Trend, mehr Sensoreingänge in das System zu integrieren. Mehrere Eingänge bieten die Möglichkeit, mehr Hautstellen zu untersuchen, um ein besseres Signal zu erhalten. Intelligente Wearables für die Gesundheitsfürsorge kombinieren zunehmend Daten aus verschiedenen Sensormodalitäten, um die Gesamtergebnisse zu verbessern und das Rauschen der einzelnen Eingänge besser in den Griff zu bekommen.

Eine herkömmliche Methode, um den Kompromiss zwischen Chipgröße und einer Zunahme von I/Os auszugleichen, besteht darin, auf Gehäuse mit einer höheren Rasterdichte (Pitch) als dem Standard von 0,4 mm überzugehen. Der Nachteil dabei ist, dass sich die Gesamtsystemkosten erhöhen, da Änderungen in der Leiterplatten- und Montagetechnik erforderlich sind, um die Leiterbahnen mit geringerem Abstand zu verarbeiten. Eine weitere Möglichkeit ist, den Grad an Multiplexing für die I/O-Kanäle zu erhöhen – insbesondere für Verbindungen zu einem externen Mikrocontroller.

Multiplexing über serielle Anschlüsse

bietet eine Möglichkeit, die Anzahl der Pins gegen den Datendurchsatz abzuwägen. Bei der Wahl des Protokolls besteht Flexibilität. Kann die erforderliche Datenrate unterstützt werden, stehen mithilfe von I2C über zwei Leitungen (anstelle von SPI über vier Leitungen) zwei wertvolle I/O-Pins frei.

Eine weitere Einsparmöglichkeit in Bezug auf die Anzahl der Pins ergibt sich durch ein Schaltungsdesign, das externe passive Bauelemente wie Kondensatoren und Induktivitäten für Analogfunktionen vermeidet. Mixed-Signal-Prozesse, die von Foundries angeboten werden, ermöglichen es, passive Bauelemente in den Interconnect-Stack einzubauen, was einen effektiven Kompromiss zwischen Chipgröße und Pinzahl ermöglicht.

Fortschrittliche Gehäusetechnik setzt zudem Platz auf der Leiterplatte und I/O-Pins frei, da das analoge Frontend als auch die Sensoren in ein einziges Gehäuse integriert werden.

Abwägung 4: Kleinere Stückliste kontra Kosten?

Ideal wäre es, die meisten Funktionen eines Systems in einem einzigen ASIC unterzubringen. Es gibt jedoch mehrere Fälle, in denen dies wirtschaftlich nicht machbar ist.

Welche Funktionen in einen ASIC integriert werden und welchen Halbleiterfertigungsprozess dieser benötigt, um sie zu implementieren, hängt von zahlreichen Anforderungen ab. Dazu gehören Spannungspegel, IP-Verfügbarkeit, Unterstützung für nichtflüchtige Speicher, die Anzahl der erforderlichen Logikgatter und die Kosten. Analoge Schnittstellen und andere unterstützende Schaltkreise sind in ausgereiften Prozessen oft wirtschaftlicher, da Transistoren und andere integrierte Komponenten nicht so skalieren wie Logik- oder Speichertransistoren.

Möglicherweise kann man nicht alles haben, was man will – aber ein guter ASIC-Entwickler ist in der Lage, Kompromisse abzuwägen und das Gesamtsystem zu betrachten, um die beste Option zu finden.

Ein Blutzucker-Überwachungspflaster

dient als Beispiel für diese Abwägungen. Das Gerät benötigt ein analoges Frontend, Bluetooth Low-Energy (BLE) für die Funkkommunikation, einen Prozessorkern und Flash-Speicher. Geht man von einem 55-nm-Prozess aus, können die Gesamtkosten für die ASIC-Entwicklung mehrere Millionen US-Dollar erreichen. Dies gilt nicht nur für den Entwurf und die Erstellung der Masken, die für die Fertigung in der Fab verwendet werden, sondern auch für die Lizenzierung des BLE- und Prozessor-IPs.

Eine kostengünstigere Methode für dasselbe Design ist ein Analog-Frontend-ASIC, der für gängige BLE-fähige Prozessoren ausgelegt ist. Die Flexibilität, verschiedene externe Prozessoren zu unterstützen, würde Änderungen in der Fertigung ermöglichen, sobald die Bedingungen in der Lieferkette dies erfordern.

Dies würde duplizierte Funktionen im ASIC erfordern, was zusätzliche Universal-I/Os und I2C- oder SPI-Schnittstellen sowie Schnittstellen für das Stromversorgungsmanagement erfordert und die Größe des ASICs und damit die Kosten erhöht. Es ließen sich allerdings noch größere Einsparungen erzielen, wenn der ASIC in einem ausgereiften Prozess mit niedrigeren Maskenkosten hergestellt wird, z. B. 130 nm. Zudem müsste für den ASIC weniger IP lizenziert werden, was die Entwicklungskosten senkt. Das Design würde aber immer noch den Schutz der Lieferkette gewährleisten.

ASICs schützen Design und Lieferkette

Der ASIC-Ansatz schützt vor Problemen in der Lieferkette und ermöglicht Design-Optimierungen. Es müssen jedoch immer Kompromisse eingegangen werden, über die man sich im Klaren sein sollte, falls man diesen Weg einschlägt. (uh)

| Über den Autor |

|---|

| Dr. Konstantinos Glaros ist leitender Analog-, HF- und MS-IC-Designer bei EnSIlica und arbeitet in verschiedenen Produktbereichen, darunter Medizin- und Fitnessgeräte mit geringem Stromverbrauch und kleinem Formfaktor. |