Schuld ist nur der Durchlasswiderstand?

Mit dem richtigen MOSFET Schaltnetzteil-Verluste verringern

Fortsetzung des Artikels von Teil 2

Schaltverluste

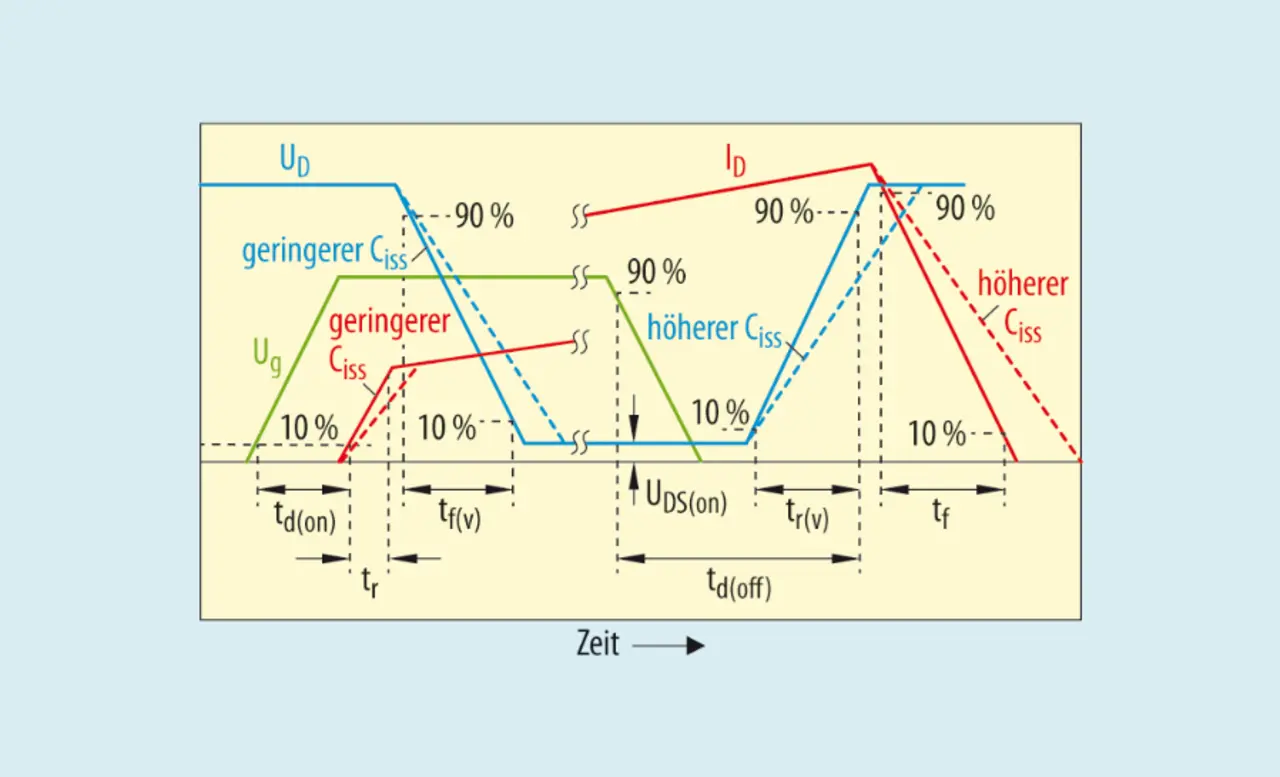

Als vereinfachte Definition der Schaltverluste eines MOSFET kann das Produkt aus UDS und ID über den Schaltzeitraum gewählt werden. Dieses tritt auf, wenn entweder ID oder UDS ungleich Null sind. Die Definitionen der MOSFET-Schaltparameter (tdly(on), tdly(off), tr und tf) unterscheiden sich überraschenderweise je nach MOSFET-Hersteller. Beim Verwenden von MOSFET-Parametern aus Datenblättern ist es also sinnvoll, zu überprüfen, ob die Parameterdefinitionen einer bestimmten Norm entsprechen, zum Beispiel der Norm JEDEC JESD77-B. Bild 6 zeigt die exakten Definitionen der MOSFET-Schaltparamater nach JESD77-B.

In der frühen Entwicklungsphase ist es äußerst nützlich, die Einschalt- und Ausschaltverluste aus den Datenblatt-Parametern abzuschätzen, anstatt den Prototyp aufzubauen und das tatsächliche Schaltverhalten des MOSFET zu betrachten. Der Schaltzeitraum eines induktiven festverdrahteten PWM-Netzteils ist in Bild 6 zu sehen. Resonanz-Schaltnetzteile weisen einen anderen Satz an Wellenformen auf.

Jobangebote+ passend zum Thema

Die Schaltverluste hängen von den parasitären Kapazitäten des MOSFET sowie der externen Beschaltung und deren parasitären Effekten ab. Diese ändern sich in Abhängigkeit vom Treiber und den Betriebsbedingungen. Hier erfolgen die Übergänge von Strom und Spannung (ansteigend oder abfallend) über die Drain- und Source-Anschlüsse des MOSFET während dieses Zeitraums gleichzeitig.

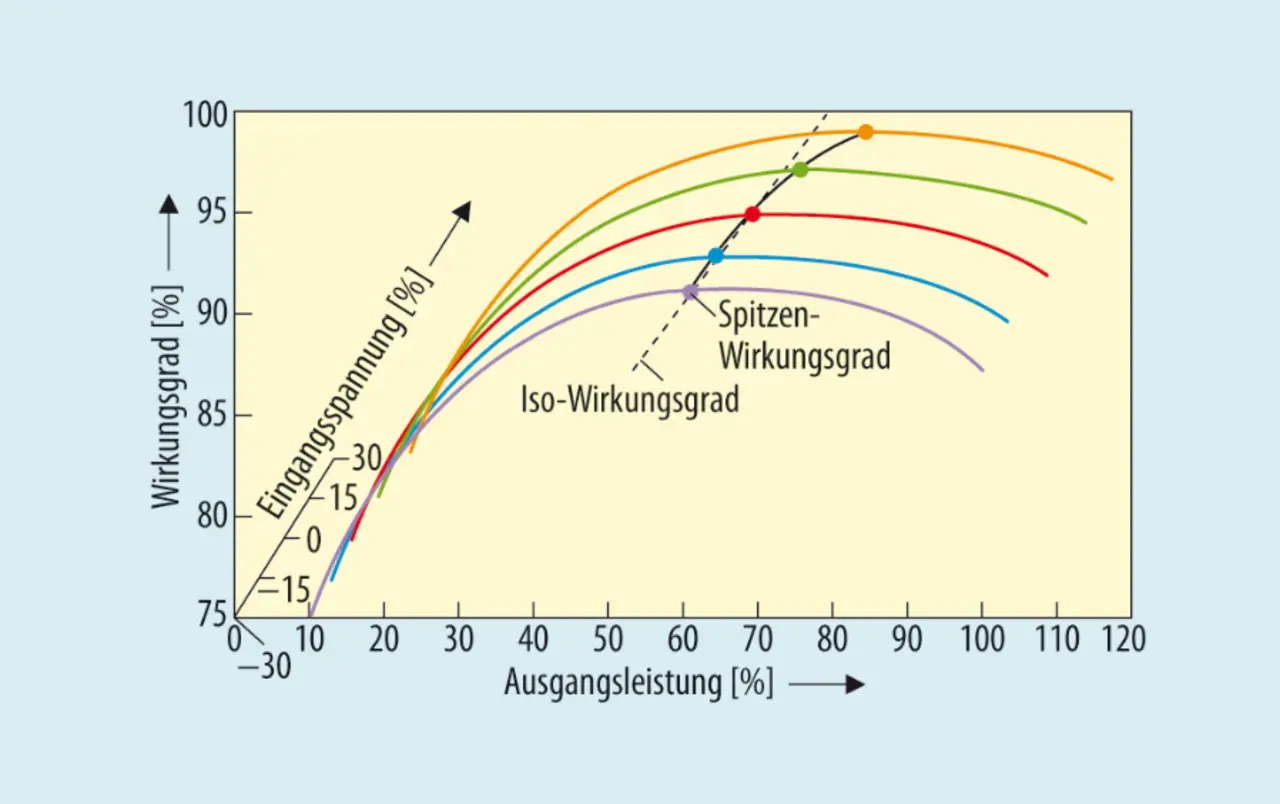

Grafisch lassen sich die Verluste durch Aufsummieren der Dreiecks- und Rechteck-Flächen abschätzen. Die Schaltverluste sind direkt proportional zur Schaltfrequenz des Netzteils. Bei einem Design für eine feste Frequenz hängen sie somit nur von Uin, Pout und Ig ab. Mit anderen Worten ist der in Bild 3 gezeigte zweidimensionale Graph in Wirklichkeit ein dreidimensionaler Graph, wobei die X-Achse die Ausgangslast, die Y-Achse den Wirkungsgrad und die Z-Achse die Eingangsspannung darstellen (siehe Bild 7).

- Mit dem richtigen MOSFET Schaltnetzteil-Verluste verringern

- Die Leistung des Netzteils

- Schaltverluste

- Treiberverluste

- Abschätzung der Verluste