Schuld ist nur der Durchlasswiderstand?

Mit dem richtigen MOSFET Schaltnetzteil-Verluste verringern

Fortsetzung des Artikels von Teil 1

Die Leistung des Netzteils

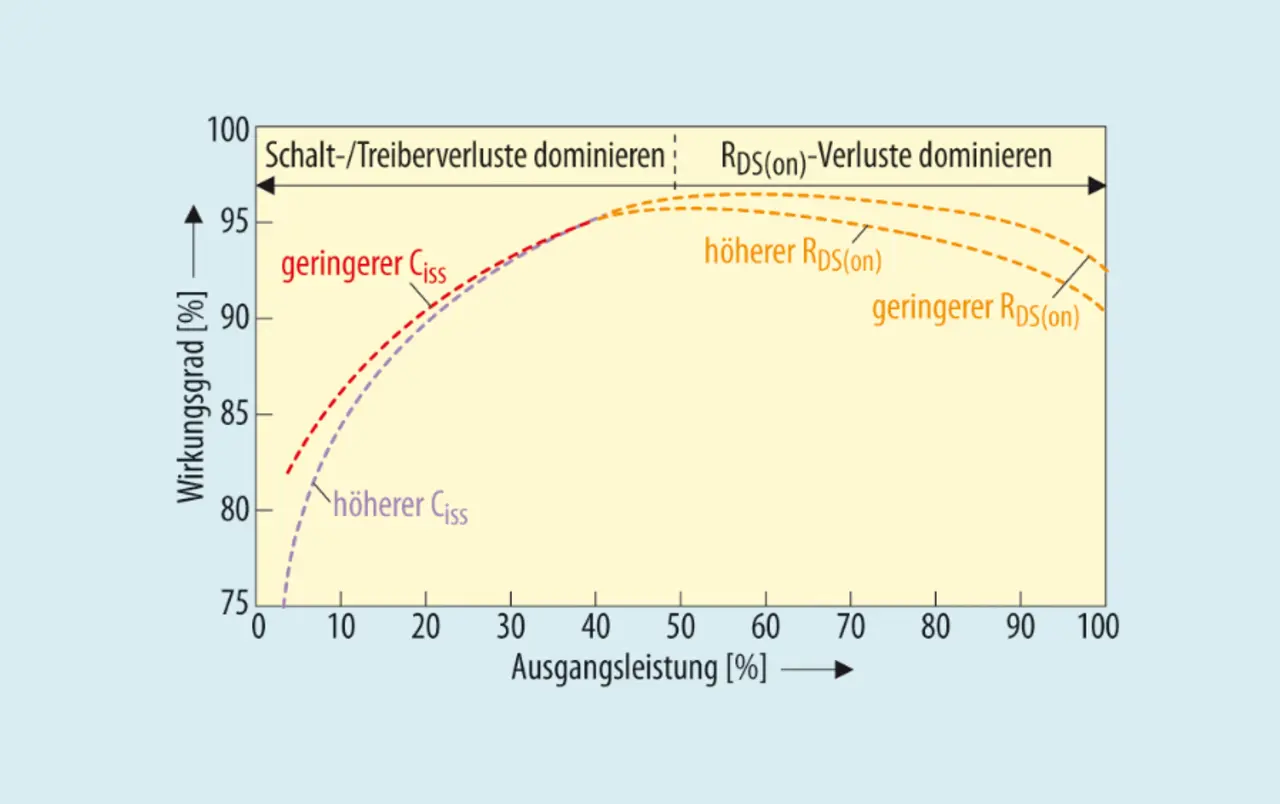

Bild 3 zeigt eine Abhängigkeit, die üblicherweise bei der Prüfung eines Schaltnetzteils angeschaut wird. Geprüft wird der Wirkungsgrad des Netzteils über dessen erwarteten Lastbereich. Der Wirkungsgrad weist einen Spitzenwert an einem Punkt zwischen der minimalen und maximalen Last auf. Bei einem guten Design befindet sich dieser Maximalwert an oder in der Nähe des Betriebspunktes, in dem das Netzteil mehr als 90 % seiner Betriebsdauer verbringt. Denn der Ort und der Wert des Maximums werden durch Abwägung der verschiedenen MOSFET-Parameter während des Entwurfsprozesses bestimmt.

Jobangebote+ passend zum Thema

Bei kleinen Lasten ist die Einschaltzeit (Tastverhältnis) gering. Dies macht die Leitungsverluste des MOSFET weitaus weniger signifikant, denn in diesem Fall wird der Wirkungsgrad durch die Schalt- und Gate-Treiber-Verluste dominiert. In typischen Schaltnetzteilen ist die Schaltfrequenz relativ konstant, weshalb die Schalt- und Treiberverluste ebenfalls konstant sind. Bei höheren Lasten gewinnen die Leitungsverluste des MOSFET (und des Ausgangsgleichrichters) gegenüber den Schalt- und Treiberverlusten die Oberhand. In diesem Fall kommt dem Wert für RDS(on) eine besondere Bedeutung zu. Wie bei allen resistiven Schaltern wird der Wirkungsgrad mit zunehmender Last schlechter. Dieser nichtlineare Effekt wird ID2(RDS(on))-Verlust genannt.

Die MOSFET-bezogenen Verluste

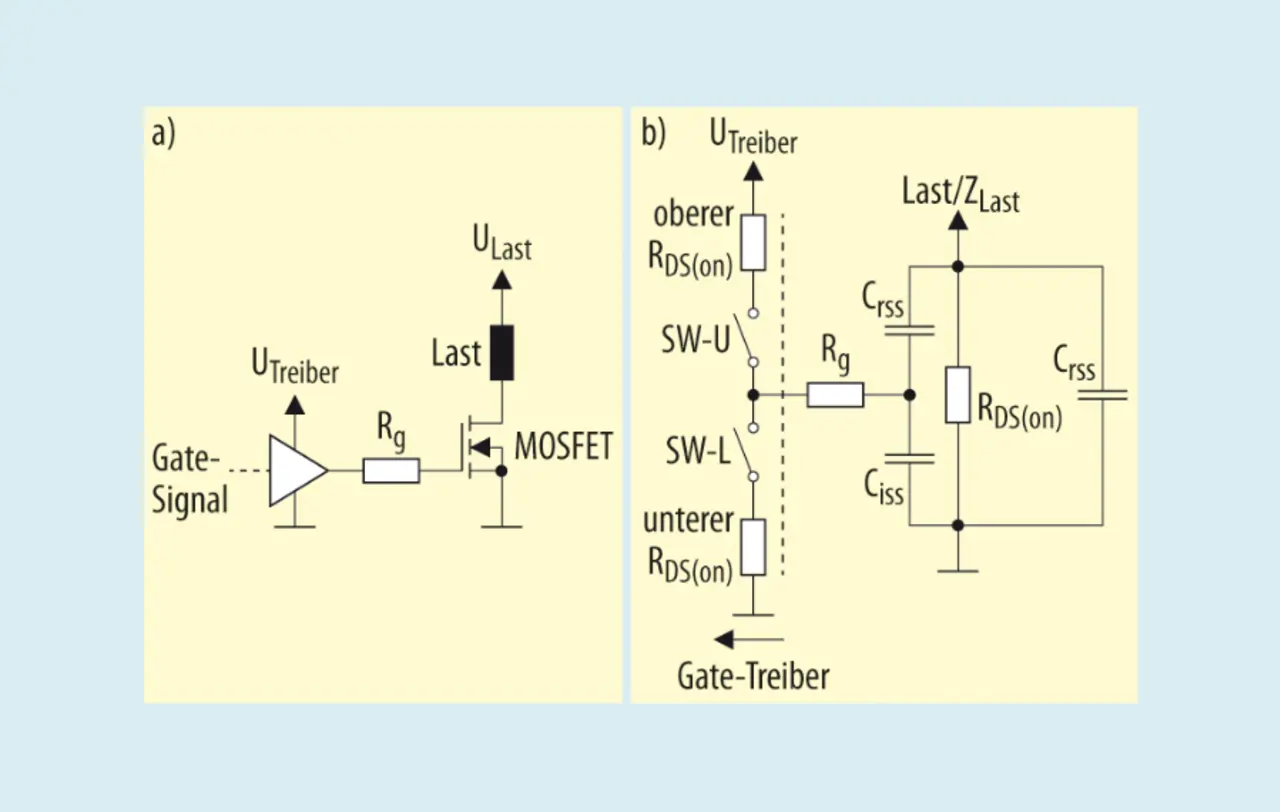

Die Verluste innerhalb der Leistungsschaltstufe (MOSFET, BJT, IGBT etc.) lassen sich in drei verschiedene Kategorien unterteilen: Leitungsverluste, Schaltverluste und Treiberverluste. Diese Verluste können sehr genau in der tatsächlichen Schaltung betrachtet und gemessen werden. Sie lassen sich zudem anhand der Parameter aus dem Datenblatt abschätzen. Bild 4a zeigt die Leistungs-Schaltstufe. Aus der in Bild 4b gezeigten Schaltung lässt sich das Verlustmodell für jeden der drei Verlustzeiträume ableiten, die während eines Schaltzyklus auftreten.

Leitungsverluste

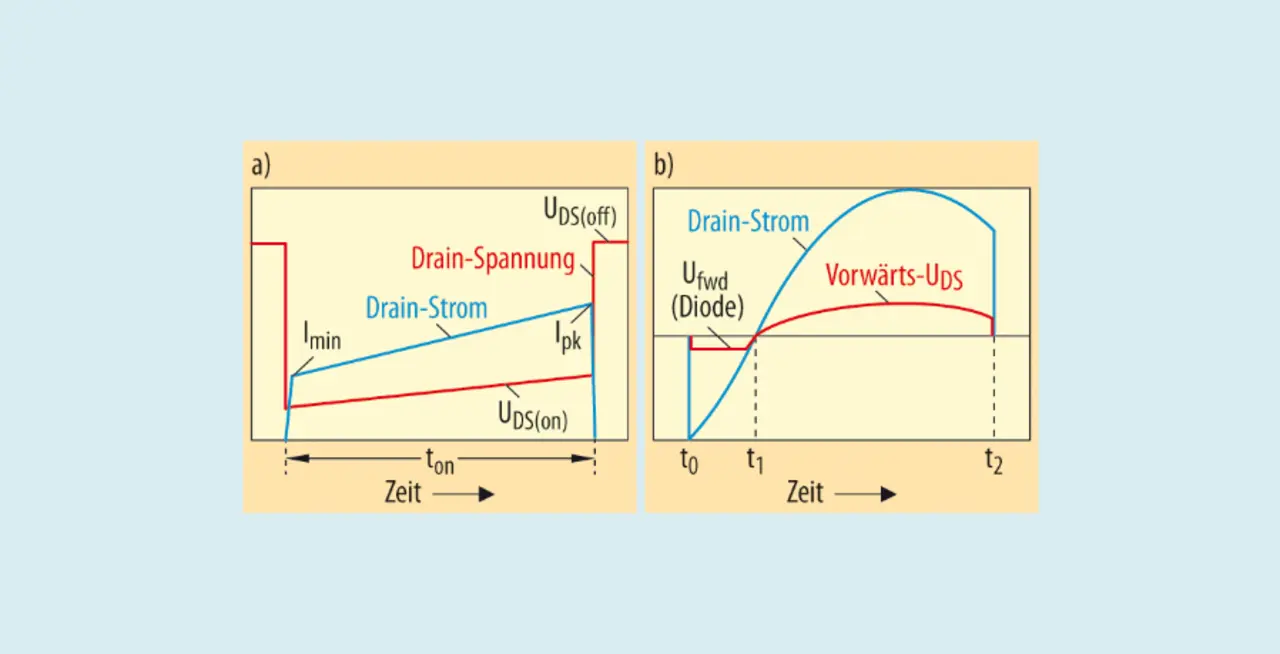

Leitungsverluste treten nur während der Einschaltzeit des MOSFET auf. Die relevanten Wellenformen hierbei sind die Absolutwerte von Drain-Source-Spannung und Drain-Strom. In festverdrahteten PWM-Netzteilen ist der Drain-Strom einfach ein Trapez, dessen Amplitude am Anfang Imin und am Ende Ipk beträgt, wie in Bild 5a gezeigt. Bei Resonanznetzteilen sind die Wellenformen komplizierter.

In diesem Fall hat der Drain-Strom üblicherweise die Form eines Abschnitts der Sinuskurve. Er wird durch einen Anfangs- und Endphasenwinkel oder dessen Abstand zur Resonanz beschrieben. Seine Amplitude kann je nach Phase positiv oder negativ sein. Während des positiven Drain-Stromflusses resultiert die Drain-Source-Spannung UDS aus dem Drain-Strom, der durch den aktiven RDS(on) des MOSFET fließt. Bei negativem Drain-Strom ist die Drain-Source-Spannung der Spannungsabfall in Vorwärtsrichtung der antiparallelen Diode des MOSFET. Einen repräsentativen Leitungszeitraum für einen LLC-Wandler zeigt Bild 5b.

Die Leitungsverluste sind vollständig durch die Einschaltzeit (Tastverhältnis) der Schaltstufe bestimmt. Sie hängen somit nicht von der Schaltfrequenz ab. Der maßgeblich bestimmende Parameter für die Leitungsverluste ist der RDS(on) des MOSFET.

- Mit dem richtigen MOSFET Schaltnetzteil-Verluste verringern

- Die Leistung des Netzteils

- Schaltverluste

- Treiberverluste

- Abschätzung der Verluste