Schuld ist nur der Durchlasswiderstand?

Mit dem richtigen MOSFET Schaltnetzteil-Verluste verringern

In einem typischen Schaltnetzteil ist der MOSFET für den größten prozentualen Anteil der Verluste verantwortlich. Durch eine Analyse von Verhalten und Leistung des MOSFET, lässt sich der Wirkungsgrad des Netzteils im zu erwartenden Betriebsbereich erheblich verbessern.

Bei der Auswahl des am besten geeigneten MOSFET für eine Schaltnetzteilkonstruktion sind viele Aspekte zu berücksichtigen. Eine gängige Meinung ist, dass die Wahl des MOSFET mit dem kleinsten Durchlasswiderstand RDS(on) zum Netzteil mit dem höchsten Wirkungsgrad führt. Zwar hat der RDS(on) sicherlich eine Auswirkung auf den Wirkungsgrad, doch müssen auch andere Parameter berücksichtigt werden. Um den optimalen MOSFET für ein Schaltnetzteil zu finden, ist es wichtig, über ein grundlegendes Verständnis zum Aufbau eines MOSFET zu verfügen sowie die Auswirkungen verschiedener voneinander abhängiger Parameter auf ein Netzteil zu kennen.

Entwickler von Stromversorgungen sind mit den Bedingungen und Grenzwerten vertraut, unter denen ihr Netzteil eingesetzt wird – Eingangsspannung, Last, Temperatur etc. Sie sollten idealerweise aber auch wissen, in welchem Betriebsbereich das Netzteil mehr als 90 % seiner Lebenszeit verbringen wird. Denn nur dann lässt sich das bestmögliche Design zu den geringstmöglichen, angemessenen Kosten

realisieren.

Jobangebote+ passend zum Thema

Planar- versus Superjunction-MOSFET

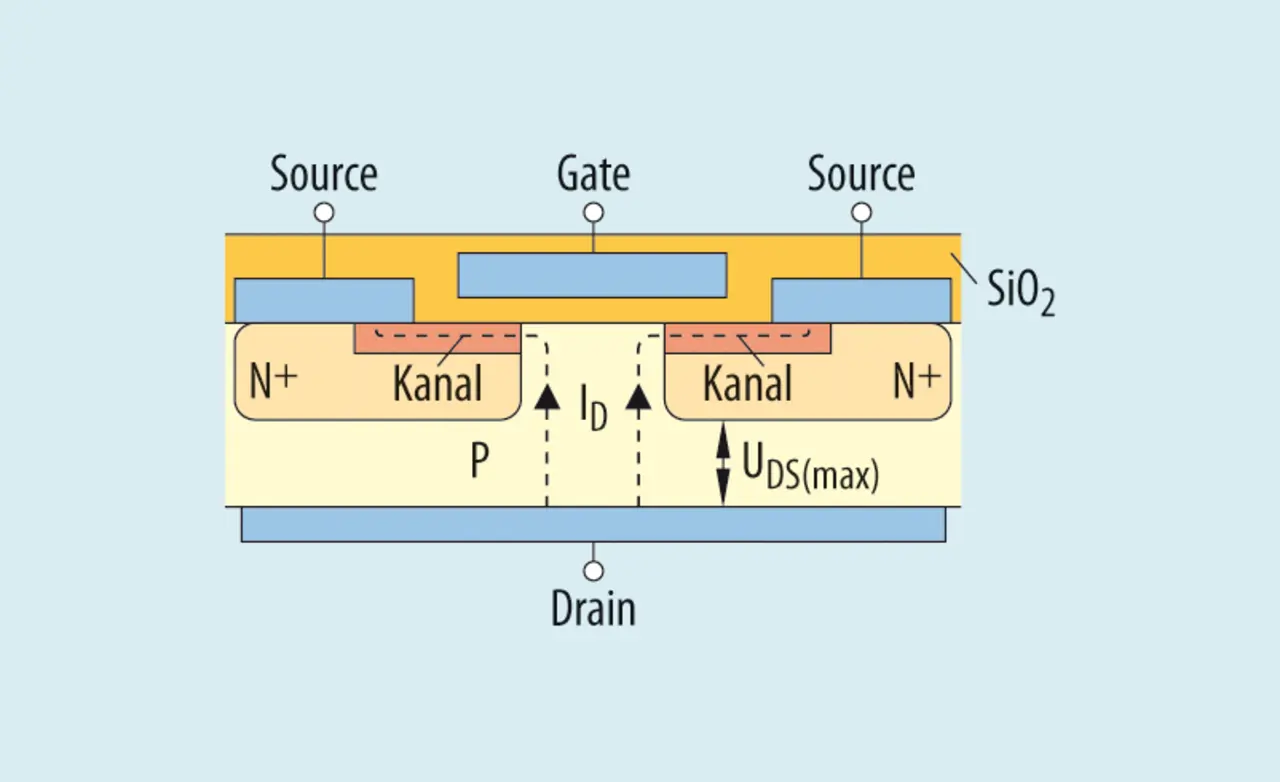

Heute sind Silizium-MOSFETs im Wesentlichen in zwei Hauptkategorien unterteilbar: in Planar- und/oder Trench-MOSFETs sowie Superjunction-MOSFETs. Bei planaren MOSFETs liegt die aktive Region in der Nähe der Die-Oberfläche, wie in Bild 1 zu sehen ist. Zur Verringerung des Durchlasswiderstands RDS(on) ist zusätzliche Chipfläche erforderlich. Um die Spannung des MOSFET zu erhöhen, muss die Chip-Dicke vergrößert werden.

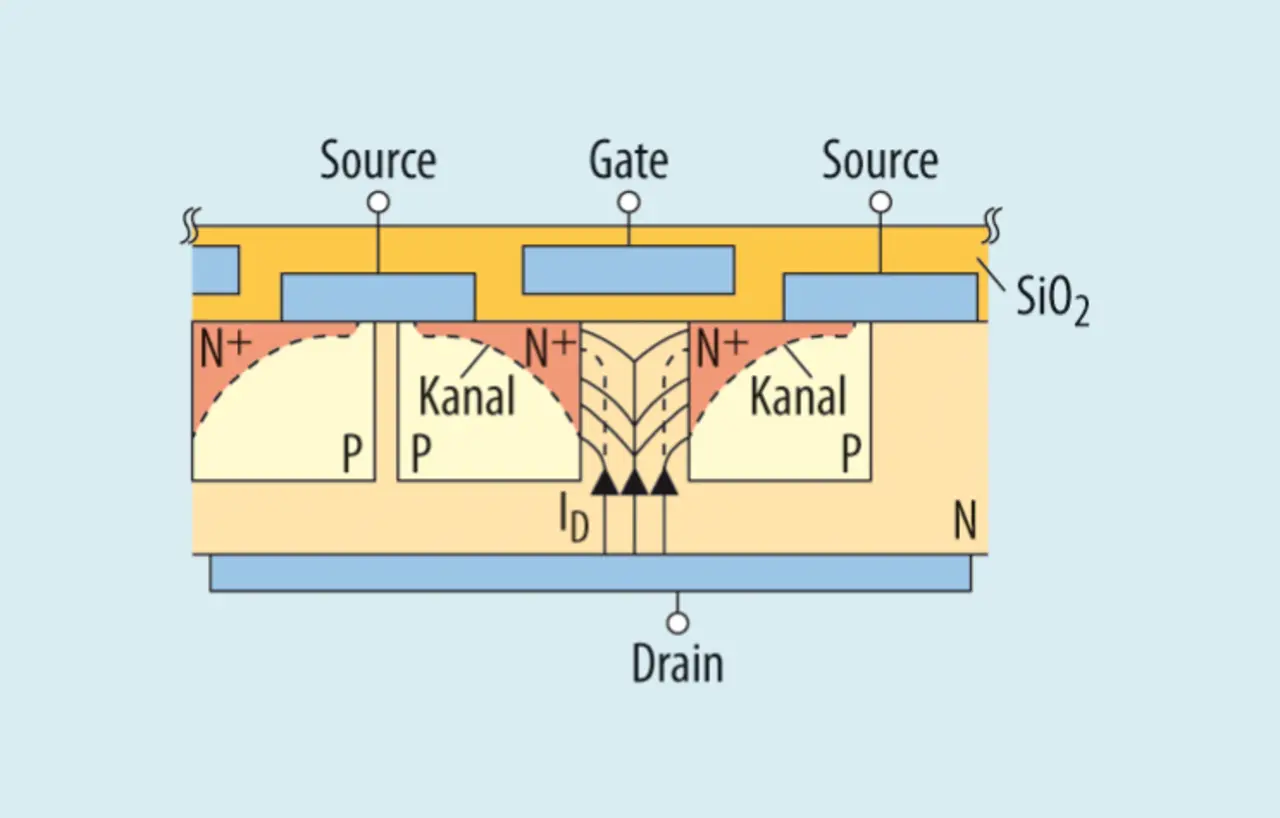

Der Superjunction-MOSFET nutzt die vorhandene Chip-Dicke zur Vergrößerung des Kanalbereichs, was dessen RDS(on) für eine gegebene Chipfläche beträchtlich verringert. Der Kanal des Superjunction-MOSFET liegt im Die, anstatt sich nur auf oder in der Nähe der Oberfläche zu befinden. Dies führt zu einer beträchtlichen Vergrößerung des Leitungsbereichs innerhalb einer weitaus kleineren Oberfläche. Der Superjunction-MOSFET ist in Bild 2 zu sehen.

Das Ergebnis ist ein deutlich geringerer Einschaltwiderstand. Dies führt für alle Nennströme zu einer kleineren Chipfläche im Vergleich zum Planar-MOSFET. Ein zusätzlicher Vorteil ist, dass sich weitaus geringere parasitäre Kapazitäten mit höheren Schaltgeschwindigkeiten erreichen lassen.

In Tabelle 1 werden die wesentlichen Parameter eines Standard-Planar-MOSFET mit den Parametern eines Superjunction-MOSFET von D3 Semiconductor verglichen. Die in der Tabelle gezeigten Bauteile besitzen nahezu identische Drain-Source-Spannungen und Drain-Ströme.

Der RDS(on) und die störenden parasitären Kapazitäten (Ciss, Crss) sind beim Superjunction-MOSFET deutlich geringer; die Schaltzeiten sind dreimal so schnell (trise, tfall). Besonders bemerkenswert ist aber, dass die freie Chipfläche des Superjunction-MOSFET nur ein Drittel der freien Oberfläche des planaren MOSFET beträgt.

| Teilenummer | Gehäuse | UDSS | ID bei 100 °C | ID bei 25 °C | Qg | trise | tfall | Ciss | Crss | RDS(on) | Eas | PD | θjc |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| XXX10N60 | T0-220FP | 600 V | 6,0 A | 10,5 A | 47 nJ | 31,0 ns | 23,0 ns | 1373 pF | 35 pF | 650 mΩ | 300 mJ | 39 W | 3,2 °C/W |

| D3S340N65 | T0-220 | 650 V | 7,3 A | 11,4 A | <25 nJ | 9,0 ns | 6,4 ns | 940 pF | 1,3 pF | <340 mΩ | 200 mJ | 160 W | 5,3 °C/W |

- Mit dem richtigen MOSFET Schaltnetzteil-Verluste verringern

- Die Leistung des Netzteils

- Schaltverluste

- Treiberverluste

- Abschätzung der Verluste