Radarsignale erfassen und bearbeiten

Bausteine für die neuen ADAS

Fortsetzung des Artikels von Teil 2

Anforderungen an Automotive-Radarsysteme

Wie eingangs erwähnt, ist in Automotive-Anwendungen nicht nur eine herausragende Leistung bei der Verarbeitung der Radarsignale erforderlich, sondern auch weitere Kriterien wie die funktionale Sicherheit, eine geringe Leistungsaufnahme und kleine Sensorabmessungen spielen eine immer wichtigere Rolle. Radarsensoren generieren sicherheitskritische Befehle für Chassis-Systeme wie zum Beispiel das Antiblockiersystem (ABS), die elektrische Servolenkung oder das aktive Federungssystem, das Auswirkungen auf die Dynamik eines Fahrzeugs hat.

Ein fälschlich ausgelöster Notbremsbefehl zum Beispiel kann fatale Folgen haben und wird deshalb als sicherheitskritisch eingestuft. Eine energieeffiziente Implementierung hilft bei der Senkung der CO2-Emissionen, vereinfacht das thermische Design des Sensors und erlaubt möglicherweise die Verwendung eines preisgünstigeren Gehäusematerials. Darüber hinaus ist es bei einem Design mit geringer Leistungsaufnahme einfacher, die Abmessungen des Sensors zu verringern, da die Verlustleistungs-Restriktionen gelockert werden.

Hardware-Lösungen für Radaranwendungen

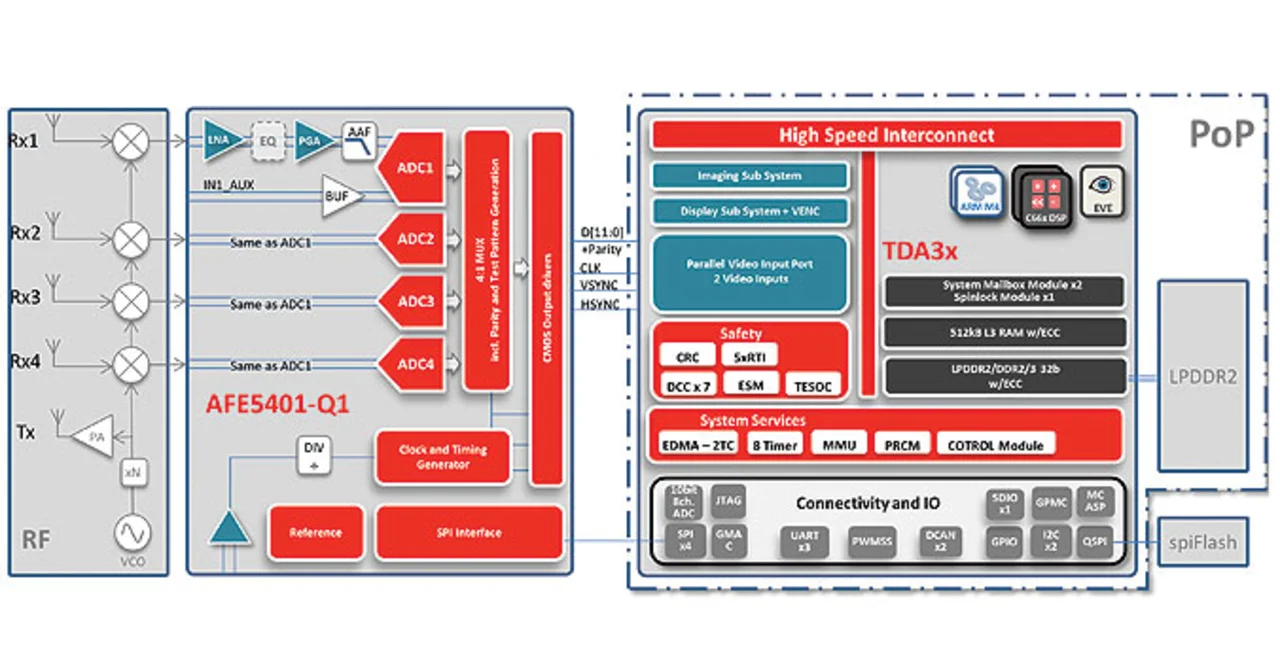

Nun zu einem realen Beispiel auf der Basis des AFE5401-Q1 und des System-on-Chip (SoC) TDA3xR von Texas Instruments (Bild 4): Diese Implementierung bietet vier Empfangskanäle. Die Bausteinfamilie TDA3xR unterstützt bis zu acht Empfangskanäle und ermöglicht damit die Implementierung einer skalierbaren Bestückung mit Radarsensoren.

Beide Bausteine sind für Radar-Anwendungen optimiert und besitzen die Automotive-Qualifikation bzw. bekommen diese noch. Beim AFE5401-Q1 handelt es sich um ein Analog-Front-End mit vier identischen Kanälen und Unterstützung für simultane Analog-Digital-Wandlung. Jeder Kanal besteht aus einem rauscharmen Verstärker (LNA, Low-Noise Amplifier), einem optionalen Equalizer, einem PGA (Programmable Gain Amplifier) und einem Anti-Aliasing-Filter, an das sich ein schneller 12-bit-A/D-Umsetzer (ADC) mit einer Abtastrate von bis zu 25 MS/s pro Kanal anschließt. Durch die gründliche, vorab erfolgende Aufbereitung verringert sich der Bedarf an weiteren externen Bauelementen erheblich. Der Equalizer kann entfernungsabhängige Verluste kompensieren, und die Abtastrate von 25 MHz unterstützt schnellere Chirps mit einer entsprechend höheren Entfernungs- und Geschwindigkeitsauflösung. Ein 12-bit-paralleler digitaler Ausgang mit einem Taktsignal und zwei programmierbaren Sync-Signalen ermöglicht die nahtlose Anbindung an einen der Videoeingänge des SoC. Optional können auf einer dreizehnten Datenleitung Paritätsinformationen übertragen werden, um eine lückenlose funktionale Absicherung vom internen ADC-Ausgang bis zum Speicher des TDA3x zu gewährleisten. Die digitalen Daten der vier Kanäle werden verschachtelt ausgegeben: Jeder vierte Wandlungswert gehört zu einem bestimmten Kanal. Ein eingebauter Mustergenerator kann vorgegebene Prüfmuster erzeugen wie zum Beispiel Rampen- oder Toggle Patterns oder aber ein individuelles Muster. Dieses Feature lässt sich nutzen, um während des Hochfahrens oder auch gelegentlich während des normalen Betriebs die physische Verbindung zwischen ADC und SoC zu überprüfen. Die erwähnten programmierbaren Features des ADC sind vom SoC aus per SPI (Serial Peripheral Interface) konfigurierbar. Das ADC-Front-End wird in einem kompakten, 9 × 9 mm2 großen QFN-Gehäuse angeboten. Wie die Bezeichnung erkennen lässt, ist TDA3x die dritte Generation einer für Fahrerassistenzsysteme entwickelten SoC-Familie. Die Familie wurde von Beginn an mit Blick auf funktionale Sicherheit und die Konformität zur Norm ISO 26262 entwickelt. Sie ist in unterschiedlichen Konfigurationen und Geschwindigkeitsvarianten verfügbar. Die mit TDA3xR bezeichneten Bausteine der TDA3x-Familie sind besonders für Radar-Anwendungen geeignet. Das „x“ dient als Platzhalter für verschiedene Geschwindigkeitsvarianten, die eine skalierbare Implementierung von Radarsensoren ermöglichen.

Mehrere Elemente kombinieren

Die TDA3x-Familie besteht aus einer heterogenen Kombination von Verarbeitungselementen, die für die unterschiedlichen Software-Aufgaben optimiert sind. Ein Subsystem mit zwei Cortex-M4-Cores, einem Embedded Vision/Vector Engine (EVE) Subsystem und bis zu zwei C66x-Gleitkomma-DSP-Subsystemen erlauben eine energieeffiziente Implementierung der Schritte zur Verarbeitung der Radarsignale. Die EVE ist ein RISC-Controller mit einem Vektor-Koprozessor und für hohen Durchsatz, hohe Verarbeitungsleistung und geringe Leistungsaufnahme optimiert. Diese Engine kann in Echtzeit alle Entfernungs- und Doppler-FFTs ausführen und das digitale Beamforming für mehrere Beams übernehmen. Darüber hinaus ist die EVE in der Lage, die kanalweise verschachtelten ADC-Daten umzusortieren und die Paritätsprüfung während der Übertragung und mit sehr geringem Zusatzaufwand auszuführen. Die Erkennung von Zielen und die Verfolgung von Objekten kann das C66x-DSP-Subsystem übernehmen.

Die Cortex-M4-Cores eignen sich gut zum Konfigurieren der HF-Bauteile und des AFE5401-Q1 sowie zum Verwalten und Überwachen der Verarbeitungsabläufe der anderen Cores. Ebenso können sie die Objektinformationen nach außen kommunizieren. Der TDA3x bietet darüber hinaus eine Vielzahl an Schnittstellen, darunter Videoeingänge für den Empfang paralleler oder serieller CSI‑2-Daten vom Radar-Front-End, ein CAN-Controller, verschiedene serielle Schnittstellen und ein QSPI, das einen schnellen Quad-Lane-Boot-Prozess unterstützt. Die DDR-Schnittstelle kommt mit verschiedenen SDRAM-Typen zurecht und besitzt eine ECC-Ergänzung für die Fehlererkennung und -korrektur. Auch die internen Speicher des TDA3x sind mit ECC oder Parität geschützt. Abgesehen von einer Hardware-mäßigen BIST-Funktion (Built-In Self-Test – eingebauter Selbsttest für wichtige Funktionen des Chips) sind weitere Sicherheitsmerkmale der Safety-MCU-Familie Hercules TMS570 eingebaut. Hierdurch ist die TDA3x-Familie für sicherheitskritische Fahrerassistenzsysteme wie etwa Radar geeignet. Die Reihe TDA3xR ist mit zwei Gehäusevarianten verfügbar, nämlich mit Abmessungen von 15 × 15 mm2 oder 12 × 12 mm2, wobei es sich bei letzterer um die sogenannte POP-Variante (Package On Package) handelt. Durch die Anordnung des DDR-Speichers auf dem TDA3x lassen sich hier die Abmessungen des Sensors minimieren.

In Kombination mit einem oder zwei Bausteinen des Typs AFE5401-Q1 erlaubt der TDA3xR skalierbare Implementierungen von Radarsensoren für kleine, mittlere und große Distanzen und vier bis acht Kanäle, wobei die Software-Kompatibilität gewahrt bleibt. Dabei bilden die Sicherheits-Features des TDA3x und des AFE5401-Q1 eine solide Basis für die Realisierung sicherheitskritischer Anwendungen. Beide Bausteine sind mit Blick auf geringe Leistungsaufnahme optimiert und werden in platzsparenden Gehäusen angeboten, damit sich die Abmessungen der Sensoren reduzieren lassen. Mit der POP-Variante des TDA3x lässt sich das Leiterplatten-Layout vereinfachen und die Zahl der Signallagen reduzieren.

Die Leistungsreserven der heterogenen TDA3x-Architektur erlauben beispielsweise die Integration des AUTOSAR Software Stack in einen der beiden Cortex-M4-Cores oder die Implementierung der Sensorfusion für eine autonome Notbremsfunktion (Autonomous Emergency Brake – AEB) zusätzlich zur Radarsignal-Verarbeitung. Die Bausteine TDA3x und AFE5401-Q1 befähigen die Entwickler von Radarsensoren dazu, den nächsten Schritt in Richtung autonomes Fahren zu unternehmen, bei dem der Sehsinn des Fahrers durch einen oder mehrere Umfeldsensoren abgelöst wird.

Der Autor

| Peter Aberl |

|---|

| studierte Elektrotechnik mit Schwerpunkt Datenverarbeitung an der Fachhochschule München. 1994 startete er als Applications Engineer im Bereich Automobilelektronik bei Texas Instruments (TI). Seit 2009 unterstützt er Kunden aus der europäischen Automobilindustrie bei Fahrerassistenzsystemen und Hercules-Sicherheits-Mikrocontrollern. Peter Aberl ist Senior Member Technical Staff (SMTS) und Principal Field Application Engineer |

- Bausteine für die neuen ADAS

- Signalerfassung und -verarbeitung

- Anforderungen an Automotive-Radarsysteme