GaN-FETs für Schaltnetzteile

Durchstarten dank großer Bandlücke

Fortsetzung des Artikels von Teil 1

Erste Schritte mit GaN für höhere Spannungen

Für Anwendungen mit höheren Spannungen bietet Nexperia zwei für 650 V ausgelegte GaN-FETs an, den GAN063-650WSAQ und den GAN041-650WSBQ. Beide sind N-Kanal-FETs, die normalerweise ausgeschaltet sind. So ist der GAN063-650WSAQ für eine maximale Drain-Source-Spannung von 650 V ausgelegt und kann eine Transiente (mit einer Pulsbreite von weniger als einer Mikrosekunde) von 800 V aushalten. Er ist für einen Drainstrom von 34,5 A und eine Verlustleistung von 143 W bei 25 °C ausgelegt. Sein Durchlasswiderstand zwischen Drain und Source beträgt im Allgemeinen 50 mΩ, mit einer Obergrenze von 60 mΩ.

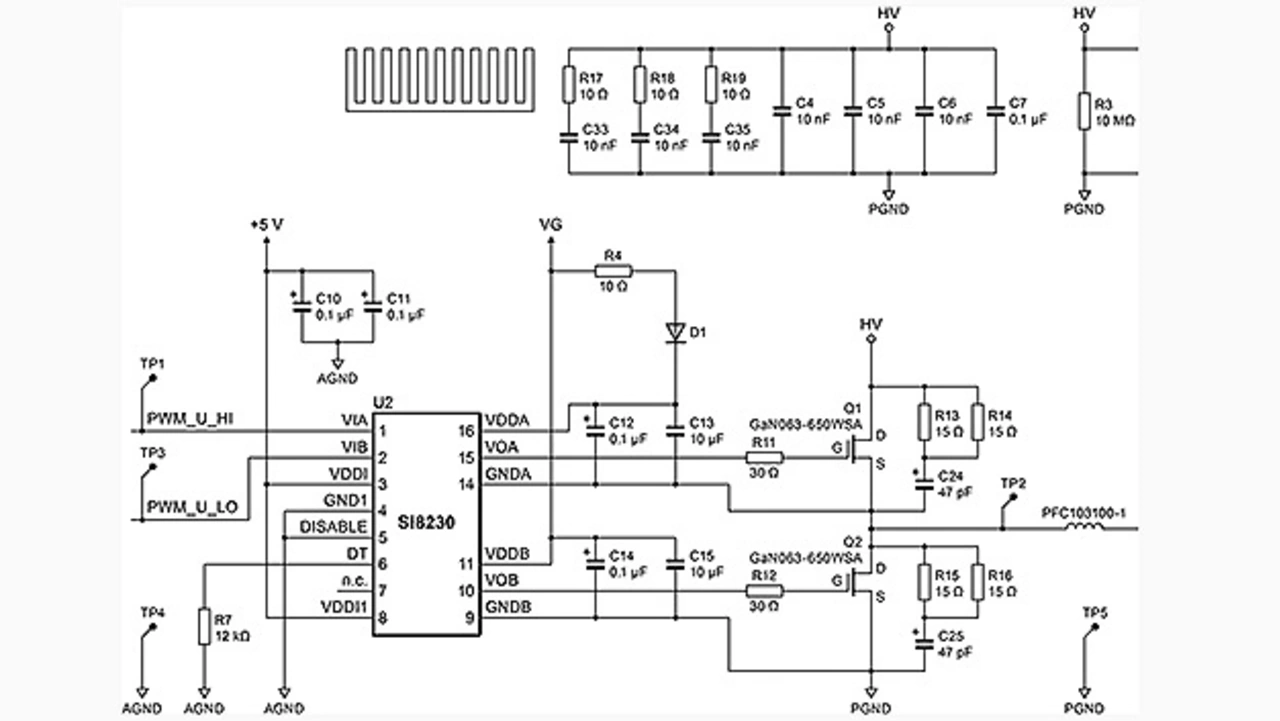

Im Vergleich dazu hat der GAN041-650WSBQ die gleiche maximale Drain-Source-Spannung von 650 V und die gleiche Transientengrenze von 800 V. Beide Bausteine unterscheiden sich jedoch in dem Punkt, dass er einen maximalen Drainstrom von 47,2 A und eine maximale Verlustleistung von 187 W bei Raumtemperatur verarbeiten kann. Sein typischer Kanalwiderstand beträgt 35 mΩ, mit einem Maximum von 41 mΩ. Ein Nexperia-Referenzdesign mit dem GAN063-650WSAQ in einer Halbbrückenkonfiguration ist in Bild 5 dargestellt.

Im Schaltplan dargestellt ist der doppelt isolierte High/Low-Gate-Treiber Si8230, der zur Ansteuerung der Gates der GaN-FETs Verwendung findet. Sein Ausgang ist über einen 30-Ω-Gate-Widerstand mit dem Gate verbunden, der für alle GaN-Bauelemente erforderlich ist. Durch den Gate-Widerstand wird die Ladezeit der Gate-Kapazität gesteuert, wodurch das dynamische Schaltverhalten beeinflusst wird. R-C-Netzwerke zwischen Drain und Source der FETs tragen ebenfalls zur Steuerung des Schaltverhaltens bei. Die Gate-Ansteuerungspegel für den GaN-FET liegen zwischen 0 und 10 bis 12 V.

Durch die hohe Schaltgeschwindigkeit der GaN-FETs (typischerweise im Bereich von 10 bis 11 ns) ist ein sorgfältiges Layout erforderlich, um die parasitäre Induktivität zu minimieren, und die Verwendung von RC-Gliedern zur Dämpfung von Schwingungen aufgrund von Spannungs- und Stromtransienten.

Zwischen der Hochspannungsversorgung und der Masse sind mehrere RC-Dämpfungsglieder (R17 bis R19 und C33 bis C35) eingebaut. Diese Dämpfungsglieder reduzieren das durch die Wechselwirkung zwischen dem GaN-FET und dem Bypass-Netzwerk verursachte Ringing. Dämpfungsglieder sollten so nah wie möglich an den Drain des High-Side-FET angeschlossen werden. Sie werden mit oberflächenmontierbaren Widerständen und Keramikkondensatoren mit niedrigem effektivem Serienwiderstand (ESR) implementiert, um die Leitungsinduktivität zu minimieren.

Das von R4, D1, C12 und C13 gebildete Bauteilnetzwerk ist eine Bootstrap-Stromversorgung für den High-Side-Gate-Treiber. D1 sollte eine schnelle Diode mit geringer Kapazität sein, da ihre Sperrschichtkapazität zu den Schaltverlusten beiträgt. R4 begrenzt den Einschaltladestrom; ein Wert in der Größenordnung von 10 bis 15 Ω hat sich in der Praxis als gut geeignet erwiesen.

Der Autor

Rolf Horn

Der Applikationsingenieur bei Digi-Key Electronics ist seit 2014 in der technischen Supportgruppe für Europa tätig und in erster Linie für die Beantwortung aller Art von entwicklungs- und ingenieurtechnischen Fragen von Endkunden in DACH und Benelux sowie für das Schreiben und Korrekturlesen von Artikeln und Blogs auf den Plattformen TechForum und maker.io von Digi-Key zuständig.

Vor seiner Zeit bei Digi-Key arbeitete er bei verschiedenen Herstellern im Halbleiterbereich mit Schwerpunkt auf eingebetteten FPGA-, Mikrocontroller- und Prozessorsystemen für IoT, Industrie- und Automobilanwendungen. Horn hat einen Abschluss in Elektrotechnik und Elektronik von der Fachhochschule München und begann seine berufliche Laufbahn bei einem Distributor für Elektronikkomponenten.

- Durchstarten dank großer Bandlücke

- Erste Schritte mit GaN für höhere Spannungen