Design-Praxis RISC-V

Von den Grundlagen bis zum Prototyp

Fortsetzung des Artikels von Teil 5

III. Prototyping mit dem Vega-Board

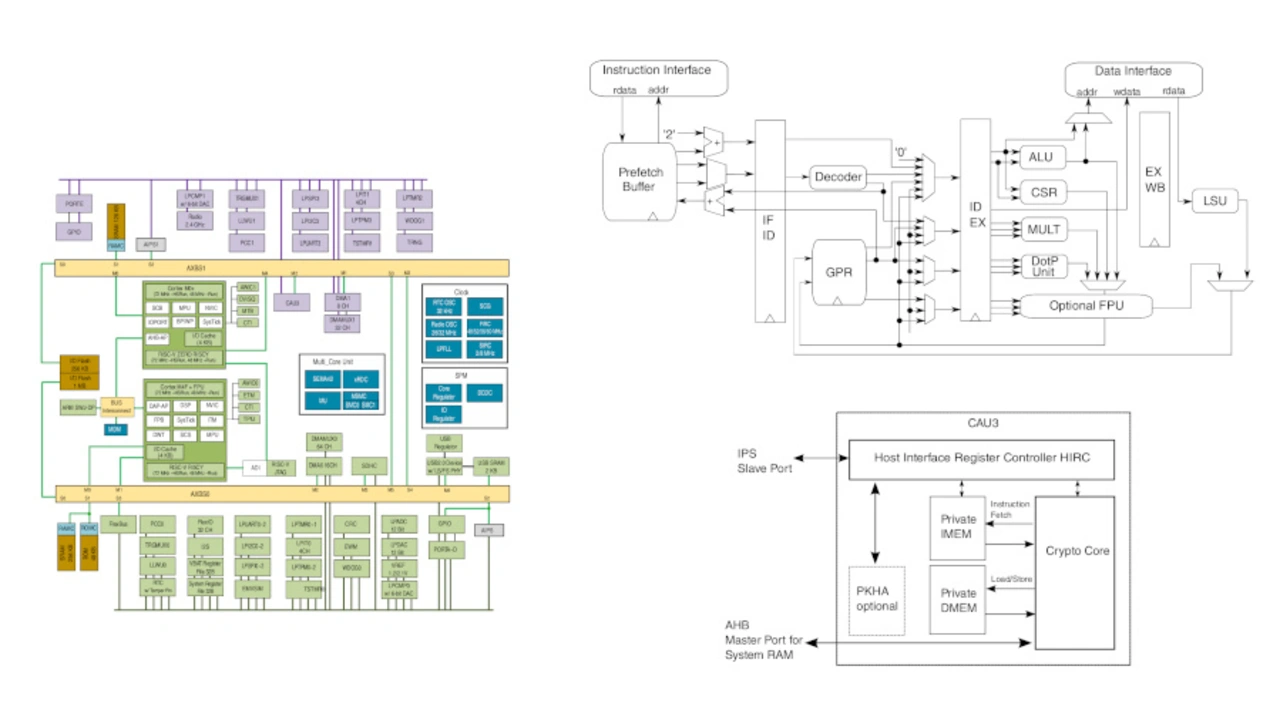

Die open-isa.org hat den RISC-V-Enthusiasten mit dem Vega-Board ein Hardware-testbed gegeben. Das Nutzerhandbuch zählt 4413 Seiten oder etwa 50 Kapitel. Vega trägt vier Recheneinheiten (Bild 3, links), jeweils in vergleichbaren Paaren, der arm- und RISC-Welt: (Cortex-M4, RIVCY) und (Cortex M0+, ZER0 RISCY).

Jobangebote+ passend zum Thema

Hardware-Merkmale

RI5CY - NXPs RISC-Flaggschiff

RI5CY (Bild 3, rechts oben) trägt nach [12] die Standard-Erweiterungen RIVE und RIVM sowie einige spannende proprietäre Erweiterungen:

- Verschobenes Laden und Speichern - führt einen Lade-/Speichervorgang simultan mit der Verschiebung des Adressursprungs aus. Damit fallen einige notwendige Teilbefehle in Standard-Zugriffsmustern weg.

- Beschleunigte Multiplikation - RI5CY setzt einen Einzyklus-32-Bit x 32-Bit-Multiplizierer mit 32-Bit-Ergebnis ein. Hier gibt es Befehle um die Multiplikation zu beschleunigen.

- ALU-Erweiterung - RI5CY hat ALU-Erweiterungen, die feste Befehlsketten aus dem Standardsatz in einem Einzelbefehl abarbeiten.

- Hardware Schleifen - eine hinreichend kleine Schleife kann auf RI5CY direkt in Hardware laufen. Der Software-Überhang wird damit reduziert. In Hardware können Startadresse, Zieladresse und ein Schleifenzähler gesetzt werden. Für das debugging werden diese Werte in das CSR abgebildet.

- Der Kryptografiebeschleuniger CAU3 (Bild 3, rechts unten) handelt u.a. die Verfahren DES, 3DES, AES-{128,192,256}, SHA-{1,256,512} und ECC. Er wird mit spezieller Firmware gesteuert.

- Entropie-Generator - Ein unabhängiger Hardwarebeschleuniger erzeugt eine 512-Bit-Entropie, die als Eingabe an Zufallsfunktionen genutzt wird.

Die Präsentation [11] zeigt generischen asm-Code für einige dieser Erweiterungen. Das Vega-Board hat eine IoT-typische Peripherie mit Funkstandards wie bluetooth, integrierter Sensorik, einer Arduino-artigen GPIO und low-power-Betriebsarten der Rechenkerne.

Debug-Schnittstellen

Die Hardware-Schnittstelle ist auf arm-Seite Coresight-Trace über SWD-Stecker und für RISC ein JTAG-Interface. Die RISC-Seite hat keine eigene trace-Funktion, so dass ad-hoc zunächst kein direkter Performanzvergleich zwischen arm und RISC möglich ist. Unter Umständen kann in einem Vielkernszenario, von der arm-Seite auf die RISC-Seite geschlossen werden. Eine profane Lösung, durch Schreiben/Lesen der Fremdspeicher (Flash oder RAM), wird den Kontrollfluss wesentlich beeinflussen [10] und ist daher abzulehnen.

Es ist nicht auszuschließen, dass die Interkern-Kommunikation über MU [10],

nach einem firmware-Anpassung teilweise trace-Daten handeln kann.

- Von den Grundlagen bis zum Prototyp

- I. RISC-V Prinzipien nach ISA-Spezifikation

- I. Verhalten in der Umgebung

- I. Interrupt- und Erweiterungsmodell

- II. Design und Verifikation nach DVCon Europe

- III. Prototyping mit dem Vega-Board

- III. SDK-Komponenten

- IV. Fazit