IEDM 2021

Die Skalierung geht munter weiter

Fortsetzung des Artikels von Teil 1

GaN auch hier ist Moore’s Law ein entscheidender Faktor

GaN (Galliumnitrid) eignet sich bekanntlich hervorragend für HF/mmWave-Anwendungen und Leistungselektronik, da es im Vergleich zu Silizium bei höheren Spannungen und Frequenzen mit geringeren Verlusten arbeiten kann. Könnte die GaN-Technologie effektiv in die CMOS-Technologie integriert und mit den üblichen Silizium-CMOS-Werkzeugen und -Herstellungsprozessen realisiert werden, ließen sich hochleistungsfähige, energieeffiziente und kostengünstige Systeme für die nächste Generation von PCs, Mobilgeräten, Datenzentren, KFZ-Radar, Kommunikationsnetzwerken etc. realisieren.

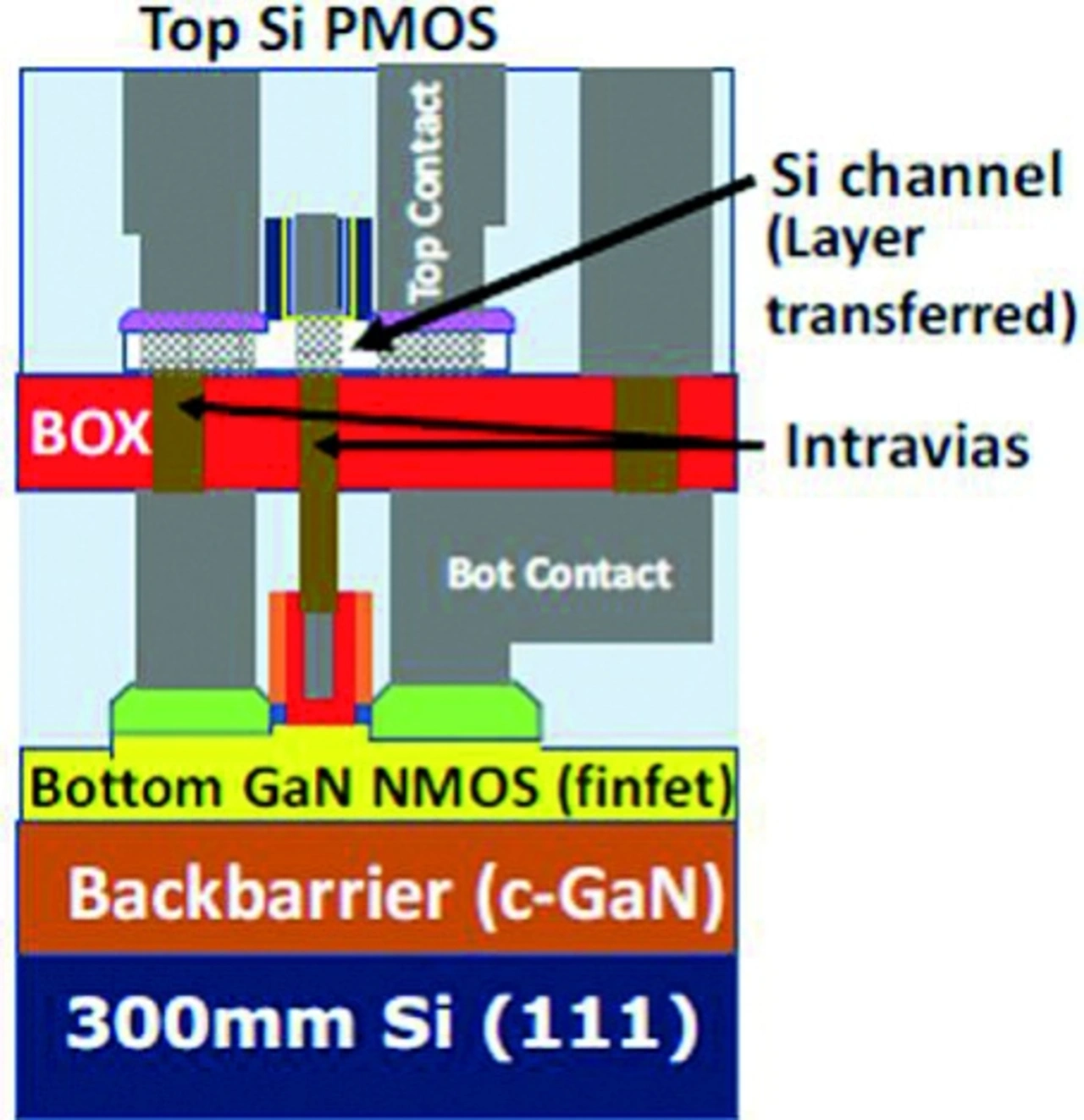

Genau darum ging es bei einem weiteren Intel-Vortrag, frei nach dem Motto: GaN trifft auf Moore’s Law. Die Forscher von Intel haben einen hochskalierten, leistungsstarken High-k-GaN-on-Si-NMOS-FinFET im Enhancement-Modus beschrieben, der auf einer 300-mm-Si-Plattform aufgebaut und in die Si-PMOS-FinFET-Technologie integriert wurde. Das heterogene Bauelement wurde durch eine von Intel auf der IEEE IEDM 2019 erstmals beschriebene Schichttransfertechnik möglich, mit der GaN-NMOS- und Si-PMOS-Bauelemente parallel produziert werden können. Der NMOS-GaN-FinFET weist die bislang schmalste GaN-Finne (Breite: 25 nm) auf, plus einer sehr kurzen Gate-Länge (30 nm). Der NMOS-FinFET wurde mit einem Si-PMOS-FinFET mit einer Breite von 35 nm integriert.

Der Baustein zeichnet sich durch viele Rekordwerte für GaN-on-Si-Ansätze aus. Dazu zählen ein fT/fMAX-Rekord mit 300/400 GHz und eine Rekord-Transkonduktanz (GM > 2100 µS/µm) mit dem dünnsten TOXE der Branche (14,8 Å). In Intels Vortrag handelt es sich um den ersten echten GaN-Transistor im Anreicherungsmodus (also typischerweise ausgeschaltet) mit einem IOFF-Wert von unter 25 pA/µm (bis zu VD = 30 V). Die Intel-Forscher haben die Fähigkeiten der Technologie mithilfe eines verlustarmen Wechselrichters demonstriert. Intel ist überzeugt, dass GaN-FinFET-Architekturen und 3D-Schichttransfertechnologien in Zukunft eine wichtige Rolle bei der Skalierung von GaN-Bauelementen und bei der Möglichkeit spielen werden, mehr Funktionen in die GaN-Technologie zu integrieren.

Jobangebote+ passend zum Thema

Speichertechnologien

Im DRAM-Bereich haben Forscher von Samsung in einem Vortrag deutliche Verbesserungen hinsichtlich der Zuverlässigkeit von DRAMs auf Basis von 17- bis 15-nm-Knoten gegenüber dem 18-nm-Knoten beschrieben. Dieser Fortschritt wurde durch mehrere Umstellungen erreicht: Erstens durch den Übergang auf eine EUV-Lithografie anstelle von ArF-Immersionslithografie für kritische Schichten; zweitens durch die Nutzung einer HK/MG-Prozesstechnologie für DRAM. Samsung nutzte außerdem Buried-Channel-Array-Transistoren (BCAT), Dual-Poly-Gate-Core/Peripherie-Transistoren, 4-Metal-Layers mit Cu/Al-Verbindungen sowie Embedded-DRAM-Kondensatoren und realisierte 8-, 12- und 16-GB-Chips, mit denen mobile LPDDRs, Grafik-DDRs, HBM und DIMMs mit bis zu 256 GB für Server-Anwendungen möglich werden. Tests zur Lebensdauer bei hohen Temperaturen (High Temperature Operation Life, HTOL) ergaben eine 2,2-fache Reduzierung der Ausfallraten bei 17-nm- und 15-nm-Knoten. Um den Erfolg ihrer Zuverlässigkeitsverbesserungen zu bestätigen, verfolgten die Forscher Hunderttausende von DIMMs über einen Zeitraum von einem Jahr, was einen niedrigen kumulativen Ausfall von rund 100 ppm ergab, ein Wert, der mit ihren beschleunigten Tests übereinstimmt.

Intel wiederum glänzte auch in diesem Bereich, und zwar mit einem Vortrag über FeFRAMs. Ferroelektrisches RAM (FeRAM) auf Hafnium-Basis speichert Bits in FE- oder AFE-Kondensatoren (AFE: antiferroelektrisch), indem sie elektrisch polarisiert werden. Die FeRAM-Technologie gilt als vielversprechender Kandidat für Embedded Memories, da sie hoch skalierbar, schnell, niedrigvoltig und CMOS-kompatibel sind und keine Transistoren mit geringem Leckstrom benötigt, wie dies bei DRAM-basierten eingebetteten Speichern der Fall ist. Intel-Forscher beschrieben, wie sie FeRAM mit Deep-Trench-AFE-Kondensatoren entwickelt haben, das eine industrieweit führende Leistung (Lese-/Schreibgeschwindigkeit von rund 2 ns) und eine sehr hohe Zuverlässigkeit (Lebensdauer von über 1012 Zyklen) bei hoher Gleichmäßigkeit auf Basis von 300-mm-Wafern aufweist.

Forscher der Chinese Academy of Sciences und Huawei wiederum haben eine Möglichkeit gezeigt, DRAMs mit extrem hoher Dichte zu realisieren. Die Skalierung herkömmlicher DRAM-Speicher wird zunehmend infrage gestellt, also sind Alternativen gefragt. Ein Team der Chinese Academy of Sciences und Huawei haben neue IGZO-FETs mit vertikalem Kanal beschrieben, die das Potenzial haben, die Größenbeschränkung der traditionellen 4F2-DRAM-Speicherzellen zu überwinden. Der 4F2-2T0C-Bitzellenbaustein (zwei Transistoren, keine Kondensatoren – die Ladung wird im Gate gespeichert) hat eine Gate-Elektrode, die von einem Gate-Isolator und einem IGZO-Kanal (Indium-Gallium-Zink-Oxid) umgeben ist. Die Source-/Drain-Elektroden sind vertikal durch eine Isolatorschicht getrennt und bilden eine Metall/Isolator/Metall-Struktur. Das Bauelement weist einen niedrigen Ausschaltstrom (rund 1,8 × 10 bis 17 A/µm) und lange Verweilzeiten (300 s) auf. Die Möglichkeit, mehrere Bitzellen monolithisch zu stapeln, deutet darauf hin, dass es sich um eine Alternative mit höherer Dichte zu herkömmlichen 1T1C-DRAM handeln könnte.

- Die Skalierung geht munter weiter

- GaN auch hier ist Moore’s Law ein entscheidender Faktor