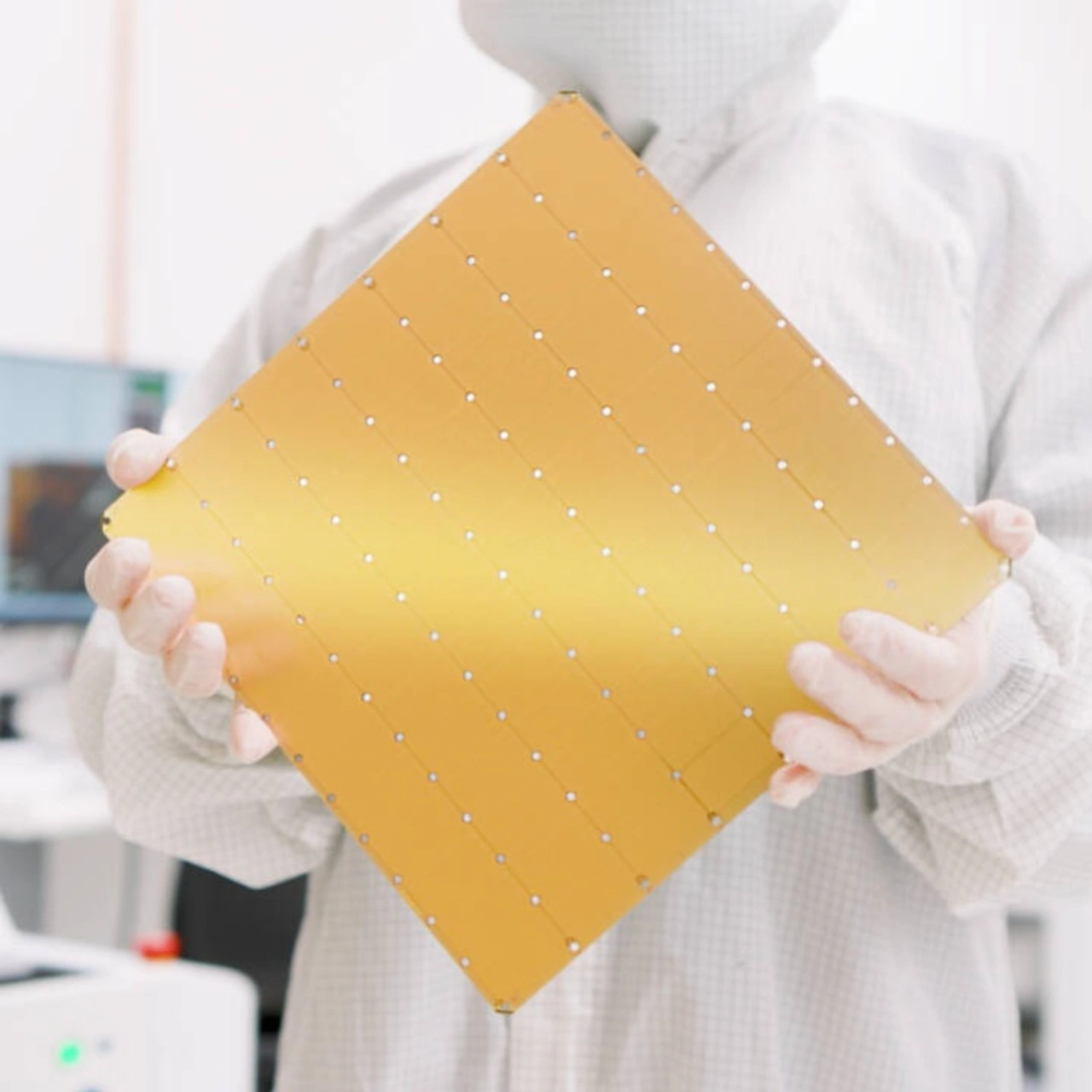

Advanced Packaging von TSMC

Chips in Wafer-Größe für KI-Training

Bis 2027 will TSMC »Systems on Wafer« auf Basis seines Advanced-Packging-Prozess CoWoS fertigen, die 40mal mehr Rechenleistung erreichen als heutige GPUs und auf denen 60 HBM-Chips integriert sind.

Wer den Begriff »Systems on Wafer« hört, wird sofort an die Monster-Chips von Cerebras denken, die TSMC bereits für den KI-Chip-Spezialisten herstellt. Hier sind identische KI-Cores über den gesamten Wafer verteilt, die jeweils eine kleinere Fläche einnehmen als die Belichtungsfenster der Lithografie-Anlage. Diese Belichtungsfenster definieren, wie groß die Fläche eines Dies auf dem Wafer höchsten sein kann, das sogenannte »Reticle Limit«, das bei derzeit 800 mm² liegt. Die Dies auf dem Wafer von Cerebras werden über die »Scribe Lines« elektrisch miteinander verdrahtet. Entlang der »Scribe Lines« wird der Wafer normalerweise zersägt, so dass die einzelnen Dies entnommen und in ihr Gehäuse gesetzt werden können. Sie bieten also Platz für die Verbindungsstrukturen. Cerebras hat auf dem Wafer ausreichend Redundanzen vorgesehen, damit unvermeidlich auftretende Fertigungsfehler umgangen werden können.

Davon unterscheidet sich aber der eigene System-on-Wafer-Ansatz von TSMC, für den das Unternehmen auf seinen CoWoS-Prozess (Chip-on-Wafer-on-Substrate) setzt. Hier verwendet TSMC zuvor getestete Dies, um die Zahl der Defekte auf dem späteren System-on-Wafer zu senken. Die Dies werden auf einen Carrier-Wafer gesetzt und die freien Flächen zwischen ihnen verfüllt. Darüber wird mit Hilfe von TSMCs Fan-Out-Prozess (InFO) meine Schicht von High-Density-Connects aufgebracht. So können auf dem System on Wafer Bandbreiten zwischen den nun verbundenen Dies erreicht werden, die so hoch sind, dass sich das System verhält, als ob es auf einem einzigen Die monolithisch gefertigt worden wäre. Bis 2027 will TSMC auf diese Weise einen Chip auf Wafer-Ebene fertigen, der in seiner Größe mehr als 40 Belichtungsfeldern entspricht, so dass das Reticle-Limit auf diese Weise umgangen wird.

Jobangebote+ passend zum Thema

Dazu setzt TSMC vorgetestete Logik-Dies und HBM-DRAMs (High Bandwidth Memory) auf ein Siliziumsubstrat, das mit High-Densitiy-Interconnects und Through Silicon Vias für die vertikalen Verbindungen strukturiert wurde. Außerdem kann TSMC für noch höhere Integration auch 3D-Advanced Packaging-Technologie heranziehen, die das Unternehmen »SoIC« nennt.

Soweit ist es aber noch nicht. Derzeit fertigt TSMC bereits ein KI-Trainingsmodul für Tesla, »Dojo«, genannt, wie TSMC auf dem North American Technology Symposium sagte. Den CoWoS-Prozess wird TSMC nutzen, um die nächste Generation der GPUs von Nvidia, genannt Blackwell zu produzieren. Dort sollen Dies integriert werden, deren Größe zusammen drei Belichtungsfenstern entspricht. Dazu gehören acht HBM-Chips. 2026 soll eine Fläche von 5,5 Belichtungsfenstern erreicht und 12 HBMs integriert werden. Damit kann laut TSMC die Rechenleistung gegenüber 2023 um den Faktor 3,5 erhöht werden. 2027 soll dann die volle Wafer-Integration erreicht werden, wie oben beschrieben.

Die System-on-Wafer-Prozess auf Basis von CoWoS erinnert an die Silicon-Interconnect Fabric (Si-IF), die vor fünf Jahren an der University of Clifonia in Los Angeles (UCLA) entwickelt wurde. Dahinter standen unter anderem Prof. Puneet Gupta und Subramanian Iyer, der sich jetzt darum kümmert, das Advanced-Packaging in den US CHIPS Act zu implementieren.

Über die vergangenen fünf Jahre hat sich das Team um Gupta und Iyer damit beschäftigt, die Interconnects auf dem Wafer noch dichter zu packen und weitere Funktionen zu integreren. »Um die volle Infrastruktur aufzubauen, werden sehr viel mehr Funktionen benötigt als nur die Finte-Pitch-Verbindungstechnik«, sagte Gupta kürzlich gegenüber IEEE Spectrum. »Eine der größten Herausforderungen besteht derzeit darin, das System mit ausreichend Leistung zu versorgen.« Deshalb arbeiten die Wissenschaftler daran, Kondensatoren und Induktivitäten sowie GaN-Leistungstransistoren in das Siliziumsubstrat zu integrieren.

Das erste Anwendungsfeld für die Wafer-Scale-Rechenmonster ist das KI-Training. IEEE Fellow Rakesh Kumar, Computer-Architekt an der University of Illinois Urbana-Champaign wird auf dem International Symposium on Computer Architecture ein Wafer-Scale-Switch-Design für Datenzentren vorstellen. In einem Datenzentum mit 16.000 Racks lässt sich die Zahl der Netzwerk-Switches damit von 4608 auf lediglich 48 reduzieren. Ein Datenzentrum mit 8000 Racks benötigte nur noch eine einzige Wafer-Scale-Switch.

TSMC setzt den eigenen CoWoS-Prozess für die Wafer-Scale-Integration ein, um leistungsfähige Systeme für das KI-Training zu realisieren.

Ein System on Wafer von Cerebras