IEDM 2018

Wohin verschieben sich die Grenzen der Halbleitertechnik?

Das 64. International Electron Devices Meeting ist der bedeutendste Treffpunkt der Halbleiter-Experten auf Transistor-Ebene. Dieses Jahr sind die Highlights ein 3-nm-CMOS-Prozess, DRAMs in 16 nm und HF-FinFETs für 5G in 22 nm. Außerdem spielen Quanten-Computing und KI eine wichtige Rolle.

Wenn San Francisco ganz frisch weihnachtlich geschmückt ist, findet im »Hilton Union Square« traditionell das International Electron Devices Meeting (IEDM) statt, in diesem Jahr vom 1. bis 5. Dezember. Das umfangreiche Programm kann sich sehen lassen. Einschließlich der Plenary Session gibt es in diesem Jahr insgesamt 40 halbtägige Sessions an den drei Konferenztagen von Montag bis Mittwoch zu fast allen Themen rund um die Halbleiterei. Am Wochenende zuvor veranstaltet die IEDM noch sechs Tutorials (Samstag nachmittags) und zwei Short Courses (Sonntag ganztags).

Den Auftakt macht die Plenary Session, bei der anerkannte Experten auf den drei Regionen Amerika, Europa und Asien zu Wort kommen. In diesem Jahr startet der Südkoreaner ES Jung, President des Foundry Geschäfts bei Samsung mit dem Thema »4th Industrial Revolution and Foundry: Challenges and Opportunities«. Den Europäischen Part übernimmt Prof. Gerhard Fettweis, Inhaber des Vodafone Stiftungslehrstuhls an der TU Dresden mit »Venturing Electronics into Unknown Grounds«. Einen klaren Heimvorteil hat der dritte Plenar-Sprecher Jeff Welser, Vice President und Lab Director vom IBM-Forschungszentrum Almaden, das in den Bergen südlich von San Jose liegt. In seinem Vortrag dreht es sich um künstliche Intelligenz: »Future Computing for AI«.

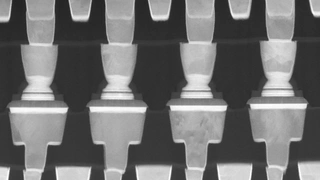

Mit der Veröffentlichung des Programms zeichnen sich bereits im Vorfeld einige bemerkenswerte Papers ab. Unter den Späteinreichungen findet sich ein 3-nm-CMOS-Prozess von Samsung auf Basis von GAA-Transistoren, bei denen das Gate den gesamten Kanal umschließt. Der Kanal besteht dabei aus horizontalen Schichten von Nanosheet, die Samsung als Multi-Bridge-Channel-Architektur bezeichnet. Ebenfalls spät kam ein Paper von IMEC in Belgien mit Lösungsansätzen, wie man DRAMs bis 16 nm und darunter skalieren kann. Das Problem liegt in den aufgrund der Verkleinerung winzigen Kapazitäten die Nullen und Einsen zuverlässig speichern sollen. Ein säulenförmiger 11-nm-Kondensator aus SrTiO3, der per ALD (Atomic Layer Deposition) aufgebaut wurde, soll das Problem lösen.

Jobangebote+ passend zum Thema

Vorschau auf die IEDM 2018

Unter den 40 Sessions sind auch vier »Focus Sessions«, die sich anstelle von Technologie-Bausteinen mit bestimmten Anwendungsfeldern befassen:

- Quantum Computing Devices, beschäftigt sich mit den Schaltelementen, die man für Quantencomputer benötigt

- Future Technologies Towards Wireless Communications: 5G and Beyond. Hier geht es um den Technik-Baukasten, den am für die Umsetzung der fünften Mobilfunkgeneration braucht.

- Challenges for Wide Bandgap Device Adoption in Power Electronics. In dieser Session stehen SiC und GaN im Mittelpunkt.

- Interconnects to Enable Continued Technology Scaling. Wie kann die Chipverdrahtung mit der Skalierung der Transistorstrukturen Schritt halten?

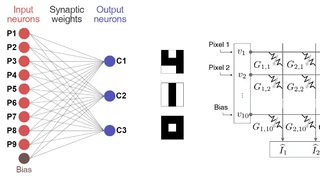

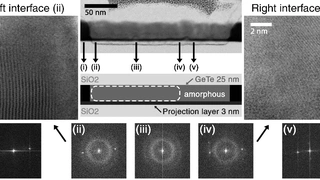

Eine wichtige Rolle spielt auch das Feld der neuronalen Netzwerke, der künstlichen Intelligenz und des neuromorphen Computings. Dazu wird eine analoge synaptische Zelle auf Basis ferroelektrischer FETs für tiefe neuronale Netzwerke vorgestellt, genauso wie eine elektrochemische synaptische Zelle, die sich auf die Speichertechnologien RRAM (resistive RAM) und PCM (Phasenwechselspeicher) stützt. Außerdem gibt es noch Papers zum In-Memory-Computing mit projected-PCM und ein physikbasiertes analytisches Modell für flüchtige RRAMs.

Rund 1700 Teilnehmer versammelten sich letztes Jahr auf der IEDM. Es wird spannend, ob das Programm in diesem Jahr mehr Teilnehmer anzieht. Die Elektronik ist wieder live dabei.