Anwendungsprozessor

Chip für industrielle Kommunikation

Industrielle Kommunikation erfordert meist mehrere Kommunikationsprotokolle, zum Teil mit Echtzeit-Anforderungen. Universalprozessoren sind dieser Aufgabe meist nicht gewachsen. Besser geeignet ist ein Prozessor mit dedizierten Kommunikationsfunktionen wie der Sitara von Texas Instruments.

Industrielle Kommunikationsfunktionen sind das Schlüsselelement für moderne Fertigungsstrategien. Sie müssen Subsysteme aus Sensoren, Motoren, Stellantrieben, speicherprogrammierbaren Steuerungen (SPS) und Mensch-Maschine-Schnittstellen miteinander vernetzen und dabei eine zuverlässige Verbindung unter Einhaltung strenger Zeitvorgaben sicherstellen. Neben dieser großen Vielzahl an Subsystemen besteht eine industrielle Anwendung unter Umständen aus Spezialgeräten und veralteten Systemen, die eine Unterstützung mehrerer Netzwerktechnologien und -protokolle erforderlich machen. Aus diesem Grund könnte es passieren, dass eine einzelne Umgebung mehrere Feldbusprotokolle wie beispielsweise Control Area Network (CAN), Modbus und Profibus sowie industrielle Ethernet-Protokolle wie Profinet, EtherCAT, Sercos III und andere unterstützen muss.

Ebenso wie für die Feldbusstandards gilt auch für die Ethernet-Standards, dass jeder einzelne dieser Standards auf spezielle Anforderungen zugeschnitten ist. Jeder bietet die Art von Echtzeit-Performance, die das herkömmliche Ethernet missen lässt, die für die Industriekommunikation jedoch erforderlich ist. Wie sie dies erreichen, unterscheidet sich von einem industriellen Ethernet-Standard zum anderen.

Jobangebote+ passend zum Thema

Vielfalt industrieller Protokolle

Profinet beispielsweise gestattet dem Master-Controller die Kommunikation mit allen Geräten im Netzwerk. Slave-Geräte wiederum können Frames mit dem Controller austauschen, mit anderen Geräten aber nur azyklisch kommunizieren. Für die Kommunikation bietet dieses Protokoll einen standardmäßigen TCP/IP-Kanal für den herkömmlichen, nicht in Echtzeit erfolgenden Datenaustausch. Für den Datenaustausch in Echtzeit unterstützt ein Profinet-Echtzeitkanal den zyklischen oder azyklischen Austausch zwischen einem Controller und Slave-Geräten.

In EtherCAT kommuniziert der Master mit den Slaves, indem Frames mit Befehlen und Daten für jeden Slave von Knoten zu Knoten übertragen werden. Bei der Übertragung liest jeder Slave-Knoten die für ihn bestimmten Befehle und Daten im Frame und fügt seine eigenen Daten zum Frame hinzu, der seinen Weg daraufhin fortsetzt. Wie Profinet auch, kombiniert EtherCAT einen herkömmlichen TCP/IP-Kanal für die ethernet-kompatible Kommunikation mit einem Echtzeitkanal für die zeitkritische Kommunikation (Bild 1).

Obwohl die industriellen Ethernet-Standards auf sehr unterschiedlichen Mechanismen basieren, sorgen sie alle für die bei herkömmlichem Ethernet nicht vorhandene Echtzeit-Performance, die für die Industriekommunikation erforderlich ist. Bei der Implementierung dieser Standards stehen die Entwickler jedoch vor dem Dilemma von Performance-Beschränkungen industrieller Mikrocontroller und den Echtzeit-Anforderungen der Anwendung.

Echtzeit – eine industriespezifische Anforderung

Echtzeitanwendungen erfordern innerhalb eines einheitlichen Zeitraums schnelle Reaktionen auf einen Befehl, eine Eingabe oder einen Interrupt. In den zyklischen Prozessen typischer Steuerungen sorgen Systeme mit niedriger Latenz dafür, dass Prozesse möglichst kurz nach dem Beginn jedes Zyklus stattfinden. Jitter oder andere Faktoren in diesen Systemen können unvorhersehbare Folgen haben und führen dazu, dass Zeitschranken überschritten werden und Prozesse mit hohen Zyklusraten nicht mehr zuverlässig und konsistent abgearbeitet werden.

In der Vergangenheit waren die Entwickler häufig dazu gezwungen, eigene Hardware-Lösungen zu entwickeln, um die Herausforderungen bei der Echtzeit-Performance im Zusammenhang mit der industriellen Konnektivität zu meistern.

Erschwert wurden die meisten Ansätze dadurch, dass die meiste Computer-Hard -und Software und Hardware darauf ausgelegt ist, die Gesamtleistung des Systems zu optimieren, anstatt auf die Anforderungen von Echtzeit-Prozessen einzugehen.

Auf der Software-Ebene benötigen die Entwickler industrieller Anwendungen deterministische Reaktionsfähigkeit mit niedriger Latenz, wie sie üblicherweise mit einem Echtzeit-Linux-System und – auf anspruchsvollerer Ebene – einem Echtzeitbetriebssystem (RTOS, Real-Time-Operating-System) bereitgestellt wird. Letztendlich sind die Latenz und die deterministische Performance vom Prozessor der zugrunde liegenden Plattform abhängig.

Cache-Architekturen bremsen Echtzeit aus

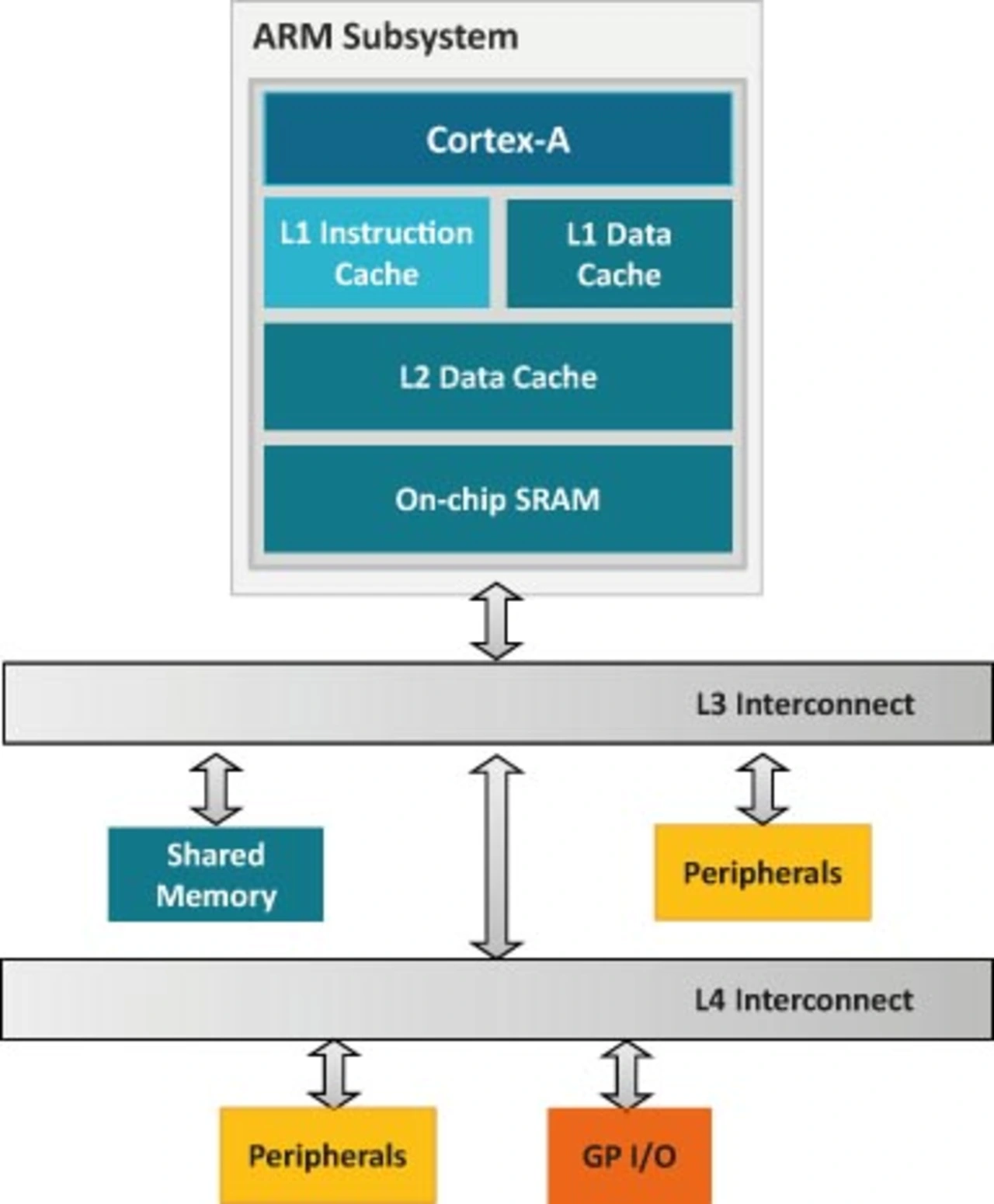

Ein Allzweckprozessor wie der Arm-Cortex-A-Kern eignet sich ideal zur Ausführung von Software, die die übergeordneten Aufgaben jeder beliebigen Anwendung ausführt, inklusive derjenigen der industriellen Automatisierung. Typische Allzweckprozessoren nutzen Cache-Speicherhierarchien mit mehreren Ebenen und mehrstufigen Anweisungspipelines, um die Verarbeitung zu beschleunigen (Bild 1).

Genau diese Architekturmerkmale erweisen sich als Beeinträchtigung für die deterministische Ausführung industrieller Echtzeit-Ethernet-Systeme. Jede Cache-, Speicher- und Verbindungsebene verlängert die Dauer zyklischer Prozesse (Latenz). Da sich die Anzahl der Ebenen, die der Prozessor durchlaufen muss, von Zyklus zu Zyklus ändern kann, sind enorme Abweichungen bei der Reaktionszeit möglich.

Abhilfe kann die Implementierung zeit- und performance-kritischer Teile des Systems mit dedizierter Hardware schaffen. Zur Unterstützung von Echtzeit-Ethernet etwa mussten bei diesem Ansatz die MAC und andere Echtzeitfunktionen in einem FPGA oder ASIC implementiert werden. Obwohl maßgefertigte Hardware überaus effizient in Bezug auf die Performance ist, sorgen der signifikante Anstieg von Kosten und Komplexität dafür, dass dieser Ansatz nur für solche Anwendungen praktikabel ist, bei denen die Performance wichtiger ist als alle anderen Punkte. Für die industrielle Kommunikation hat Texas Instruments mit der Multi-Prozessor-Architektur der Sitara-Prozessorfamilie eine praktikablere und kostengünstigere Lösung im Angebot.

Subsystem für die Industriekommunikation

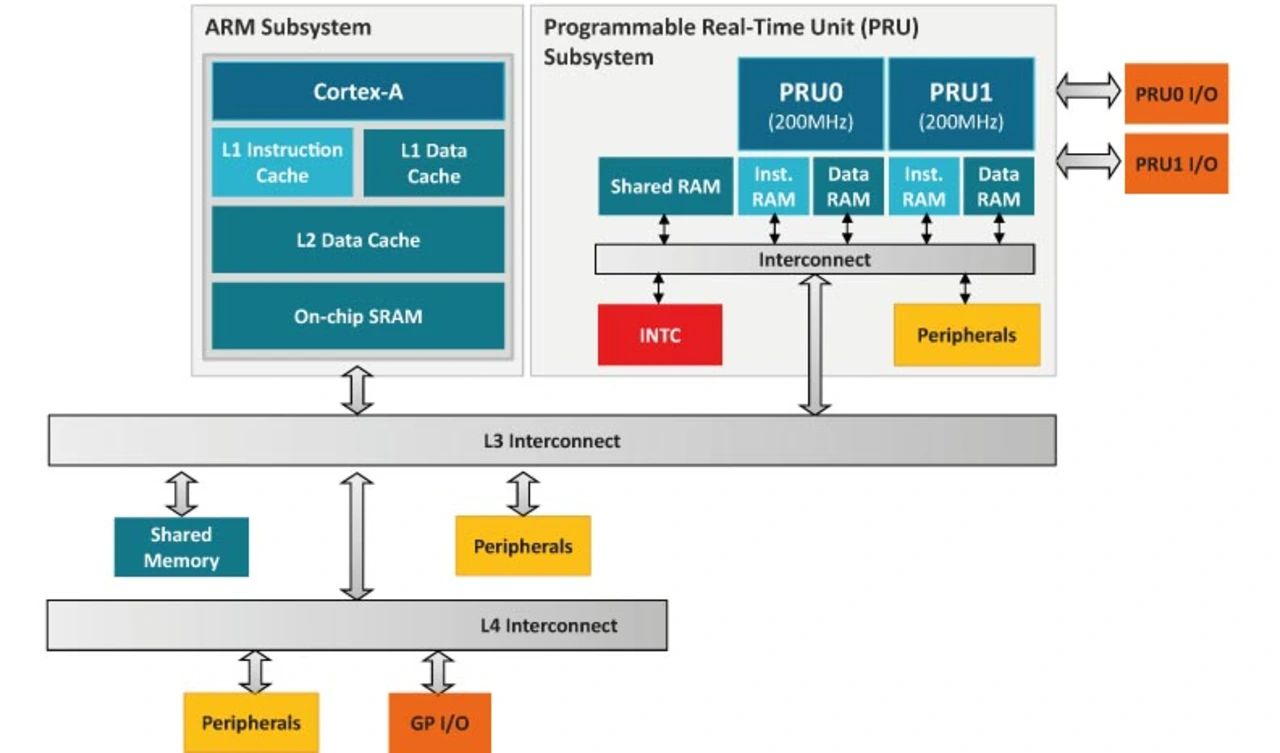

Die Sitara-Prozessorfamilie vereint einen leistungsstarken Arm-Cortex-A-Anwendungsprozessor mit einer oder mehreren Instanzen ihres PRU-ICSS (Programmable Real-Time Unit and Industrial Communication SubSystem). Während der Cortex-A-Prozessor für die Ausführung der Hauptanwendung zuständig ist, stellt das PRU-ICSS die Echtzeitverarbeitung und die I/O-Funktionen zur Verfügung, die für industrielle Ethernet-Protokolle und weitere Steuerungsfunktionen erforderlich sind (Bild 2). Eine Übersicht über die verschienenen Varianten der Sitara-Prozessoren und ihrer Unterschiede hinsichtlich der PRU-ICSS-Instanzen zeigt die Tabelle.

| Eigenschaft | AM18x/OMAPL138 | AM335x | AM437x | AM571x | AM572x (PG1.1) | |

|---|---|---|---|---|---|---|

| PRUSS | PRU-ICSS1 | PRU-ICSS1 | PRU-ICSS0 | 2× PRU-ICSS | 2× PRU-ICSS | |

| PRU core version | 1 | 3 | 3 | 3 | 3 | 3 |

| Anzahl PRU cores | 2 | 2 | 2 | 2 | 2 | 2 |

| max Frequenz | CPU freq / 2 | 200 MHz | 200 MHz | 200 MHz | 200 MHz | 200 MHz |

| IRAM pro PRU core | 4 KB | 8 KB | 12 KB | 4 KB | 8 KB | 8 KB |

| DRAM pro PRU core | 512 B | 8 KB | 8 KB | 4 KB | 8 KB | 8 KB |

| shared DRAM pro PRU core | – | 12 KB | 32 KB | – | 32 KB | 32 KB |

| GPI Pins (PRU0, PRU1) | 30, 30 | 17, 17 | 13, 0 | 20, 20 | 21, 21 | 21, 21 |

| GPO Pins (PRU0, PRU1) | 32, 32 | 16, 16 | 12, 0 | 20, 20 | 21, 21 | 21, 21 |

| MPY/MAC | N | Y | Y | Y | Y | Y |

| Scratchpad | N | Y (3 Bänke) | Y (3 Bänke) | N | Y (3 Bänke) | Y (3 Bänke) |

| CRC16/32 | 0 | 0 | 2 | 2 | 2 | 0 |

| INTC | 1 | 1 | 1 | 1 | 1 | 1 |

| Peripherals | n/a | Y | Y | Y | Y | Y |

| UART | 0 | 1 | 1 | 1 | 1 | 1 |

| eCAP | 0 | 1 | 1 | no connect | 1 | 1 |

| IEP | 0 | 1 | 1 | no connect | 1 | 1 |

| MII_RT | 0 | 2 | 2 | no connect | 2 | 2 |

| MDIO | 0 | 1 | 1 | no connect | 1 | 1 |

| Simulierte Protokolle | 1 | 1 | 2 | 2 | ||

Quelle: Digi-Key

Vergleich der verschiedenen Sitara-Bausteine.

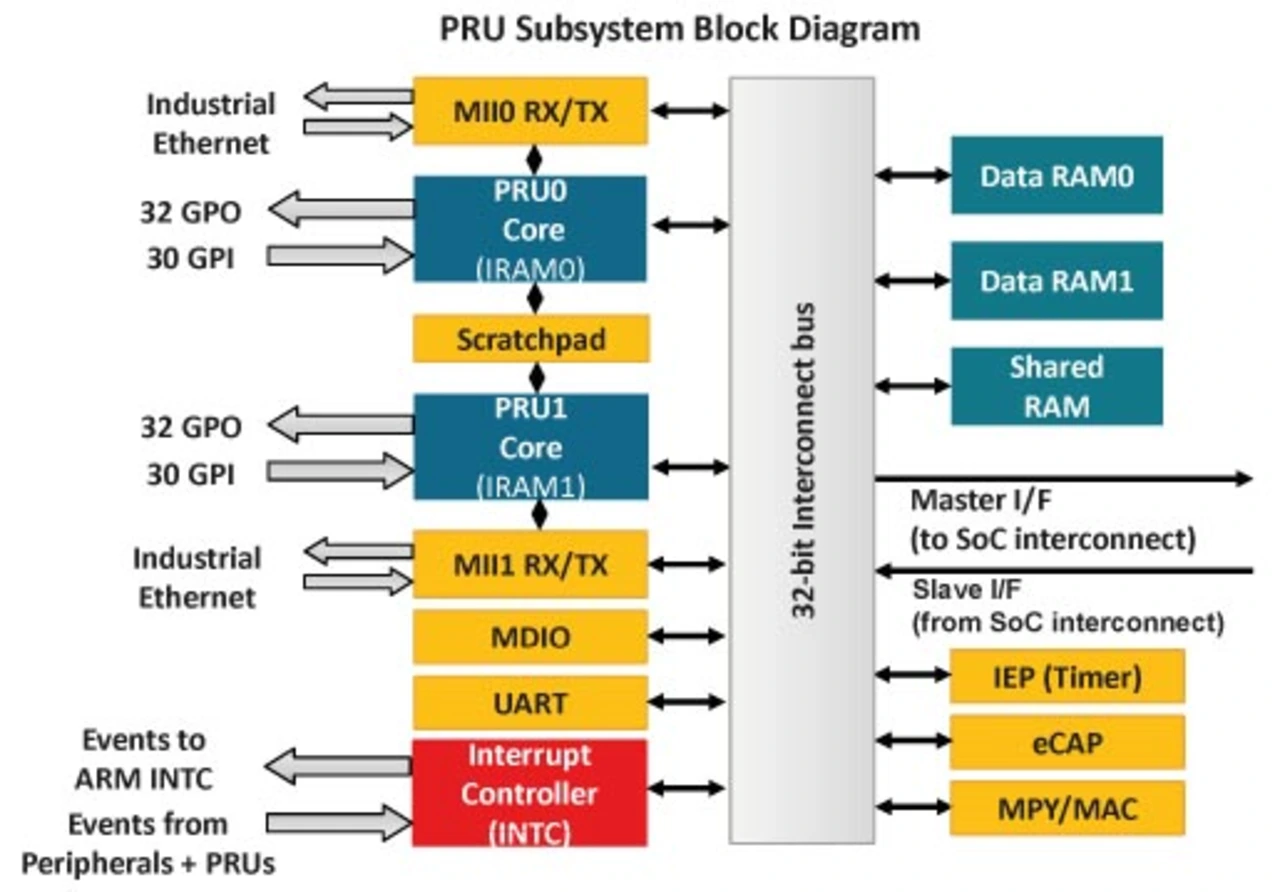

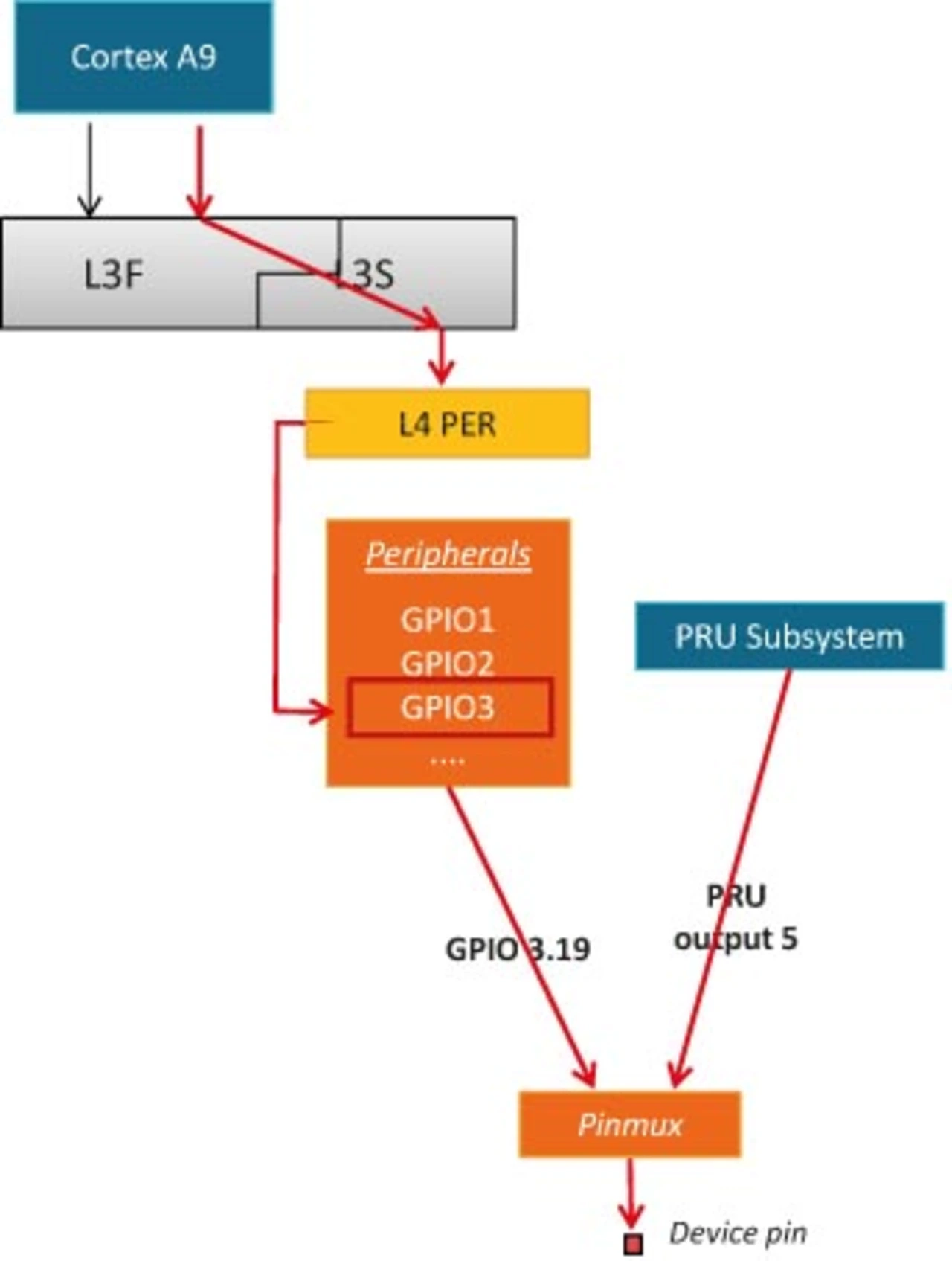

Jedes PRU-Subsystem der Sitara-Prozessoren umfasst zwei Echtzeitkerne (PRU0 und PRU1, siehe Bild 2) mit 200 MHz, die eine Zykluszeit von fünf Nanosekunden pro Anweisung bieten. Die Kerne verfügen über einen kleinen Satz von Befehlen, die ohne Befehls-Pipeline verarbeitet werden, um die deterministische Ausführung in einem einzelnen Zyklus zu gewährleisten. Um die Latenz für den Betrieb von Peripheriebausteinen zu reduzieren, greifen die Kerne über eine dedizierte 32-Bit-Verbindung auf gemeinsam genutzte Ressourcen zu (Bild 3). Dank dieser eng gekoppelten Peripheriearchitektur können die Echtzeitkerne unabhängig voneinander betrieben werden. Die Kombination aus schneller Ausführung in einem Zyklus und direktem Zugriff auf Peripheriebausteine ermöglicht dem Subsystem die deterministische Ausführung zyklusbasierter Prozesse. Dadurch kann das PRU-Subsystem I/O-Vorgänge ausführen und externe Pins sehr viel effizienter erreichen als der begleitende Allzweckprozessor (Bild 4).

Um die Zuweisung und das Management von Ressourcen in der eng gekoppelten Ausführung zu optimieren, bietet die Sitara-Systemarchitektur sowohl in der Hardware als auch in der Software Mechanismen zur Koordinierung. Auf der Hardwareebene tragen Funktionen zur Kommunikation zwischen den Prozessoren, wie etwa Mailboxen und Sperrregister dazu bei, dass die Synchronisierung des Cortex-A-Prozessors und des PRU-ICSS funktioniert.

Software-Unterstützung

Auf der Softwareebene bieten die Multiprocessing-Dienste von Linux eine Standardbetriebsumgebung zur Koordinierung der Aufgabenausführung im eng gekoppelten Betrieb. Zur Laufzeit koordiniert der Betriebssystemkern, der auf dem Arm-Cortex-A-Kern ausgeführt wird, die PRU-Systemvorgänge. Hierfür verwendet er die standardmäßige Steuerung über RemoteProc- (Remote Process) und rpmsg-Dienste (Remote Process Messaging) zusammen mit seinen eigenen Treibern und den passenden Treibern in der PRU-Firmware. Während sich die RemoteProc-Dienste um das Laden der PRU-Firmware und die nachfolgende Verarbeitung kümmern, ermöglicht das rpmsg-Framework den Nachrichtenaustausch zwischen Anwendung und PRU mithilfe der Virtualisierungsschnittstelle Virtio.

TI stellt vollständige Protokoll-Stacks für mehrere verschiedene serielle Kommunikationsprotokolle, Feldbusprotokolle und Echtzeit-Ethernet-Protokolle – inklusive EtherCAT, Profinet und Sercos III – zur Verfügung. Durch die Kombination von Protokoll-Stacks auf demselben Sitara-System können Entwickler die verschiedenen Konnektivitätsanforderungen für typische SPS oder industrielle Switches unterstützen, die beispielsweise auf der Host-Seite ein industrielles Ethernet-Protokoll wie Profinet und auf der Peripherieseite einen Feldbus wie Profibus oder IO-Link unterstützen müssen.

Die verfügbaren Standardpakete für industrielle Ethernet-Protokolle werden als Blackbox-Binärprogramme angeboten, wobei TI die Entwickler auch mit verschiedenen Beispielen für industrielle Kommunikationsdienste versorgt. Für die Anwendungsentwicklung bietet ein familienspezifisches Prozessor-Softwareentwicklungskit von TI, beispielsweise das Prozessor-SDK für AM437x Sitara-Prozessoren, eine API (Application Programming Interface) für die entsprechende Prozessorfamilie. Durch die Bereitstellung familienspezifischer Funktionen bieten diese APIs intuitive Abstraktionen für Low-Level-Vorgänge wie GPIO- oder IO-Link-Transaktionen.

Hardware für das Prototyping

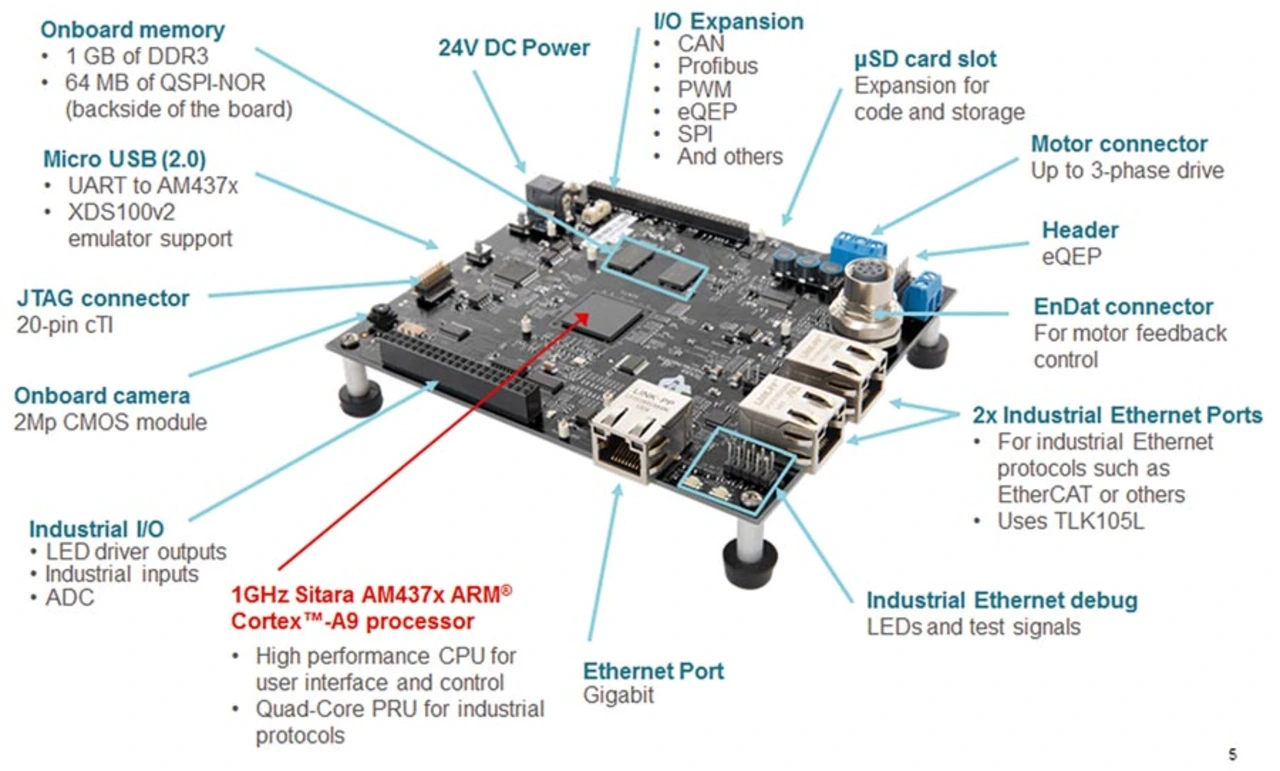

Auf ähnliche Weise beschleunigt das IDK (Industrial Development Kit) TMDSIDK437X von TI die Entwicklung, indem es eine umfassende Hardware-Plattform auf Sitara-Basis für Industrieanwendungen bereitstellt (Bild 5). Die IDK-Platine TMDSIDK437X von TI ist mit 1 GB DDR3-RAM, Quad-SPI-NOR-Flash-Speicher und einem Sitara-Prozessor AM4379 von TI ausgestattet. Der AM4379-Prozessor kombiniert einen Arm-Cortex-A9-Prozessor mit zwei PRU-Subsystemen, von denen jedes über die zwei oben beschriebenen PRU-Kerne verfügt.

In einem typischen industriellen Automatisierungsnetzwerk kann der Sitara AM4379 mehrere Rollen übernehmen. Neben der Verwendung in Multi-Protokoll-Systemen wie SPSen, Switches und Gateways können die AM4379-Prozessoren der Sitara-Familie in Endgeräten zum Einsatz kommen, die aufgrund ihrer integrierten Grafiksubsysteme HMI-Unterstützung erfordern.

Neben mehreren Peripheriebausteinen und Kommunikationsanschlüssen befinden sich auf der IDK-Platine auch Ethernet-Bausteine, unter anderem der PHY-Transceiver TLK105 von Texas Instruments mit 10/100 Mbit/s für industrielle Ethernet-Verbindungen und von Microchip Technology der PHY-Gigabit-Transceiver KSZ9031RNXIA-TR für herkömmliche Ethernet-Verbindungen.

Die Implementierung einer industriellen Kommunikationsanwendung gelingt mit diesem Kit im Handumdrehen, da lediglich eine 24-Volt-Spannungsquelle und ein Ethernet-Kabel für die Verbindung zum Entwicklungssystem benötigt werden. Die TI-PRU-ICSS-Industriesoftware bietet Softwarepakete für die weiter oben erwähnten industriellen Kommunikationsprotokolle.

Für maßgefertigte Anwendungen dient das Kit als umfassendes Referenzdesign, das zur Beschleunigung der Hardware-Entwicklung beitragen kann. In Kombination mit dieser Hardware-Basis ergeben das Prozessor-SDK und das PRU-ICSS-Industriesoftwarepaket von TI eine Entwicklungsplattform, die den Anforderungen neuer Anwendungen gerecht wird, die auf verschiedenen industriellen Kommunikationsprotokollen aufbauen.

Blaupause für industrielle Geräte

Unter den immer zahlreicher werdenden Anforderungen ist eine hohe Performance für die Ausführung industrieller Kommunikationsprotokolle entscheidend, um moderne industrielle Automatisierungssysteme realisieren zu können. Während Überwachungs- und Regelungsalgorithmen in diesen Systemen Allzweckprozessoren erfordern, benötigen Echtzeit-Aufgaben spezialisierte Komponenten, um die niedrige Latenz und Determinismus sicherzustellen, die zur Unterstützung von industriellen Echtzeit-Kommunikationsprotokollen für Feldbus- und Industrial-Ethernet erforderlich sind.

Die Sitara-Prozessorfamilie von Texas Instruments enthält sowohl die Allzweck- als auch die Echtzeit-Verarbeitungseinheiten, die erforderlich sind, um diesen vielseitigen Anforderungen gerecht zu werden. Mit einem Industrial-Development-Kit auf Sitara-Basis von TI und vorgefertigten Kommunikationsprotokoll-Stacks können Entwickler im Handumdrehen anspruchsvolle industrielle Automatisierungsanwendungen bereitstellen, die verschiedenste industrielle Kommunikationsoptionen unterstützen können. (jk)