IEDM 2023 – Teil 2

Neuromorphes Computing, Speicher, Photonik

Im Speicherbereich wurden auf der letzten IEDM wieder einige interessante Neuentwicklungen vorgestellt, selbst in der alteingesessenen DRAM-Technologie. Aber auch neuere Themen wie neuromorphes Computing oder eine Plattform für die Neurowissenschaft haben die Aufmerksamkeit der Experten erlangt.

MTJ-basierte STT-MRAMs (Spin-Transfer Torque Magnetic RAM) gelten als vielversprechende Speichertechnologie, um Embedded Flash ab einem Prozessknoten von 28 nm zu ersetzen. Die Technologie bietet schnelle Schreibzyklen, das Potenzial für sehr hohe Speicherdichten, einen energiesparenden Betrieb und einen langen Datenerhalt. Um die Bitdichte von STT-MRAMs zu erhöhen, besteht ein Ansatz darin, die STT-MRAM-Zelle mit einem 2-Anschluss-Threshold-Selektor zu integrieren, um 1S1R-Crosspoint-Arrays (ein Widerstand, ein Selektor) zu realisieren (Bild 1). Im Vergleich zu einer konventionellen 1T1R-Konfiguration (ein Transistor, ein Widerstand) wird davon ausgegangen, dass die Dichte mit dem 1S1R-Ansatz bei einem 16-nm-Knoten um einen Faktor von mehr als 2,2 höher ist. Der 1S1R-STT-MRAM-Ansatz hat aber noch einen weiteren Vorteil: Dank der BEOL-Kompatibilität (BEOL: Back-End-Of-Line) von STT-MRAMs und der vielen Threshold-Selektoren ist der 1S1R-Zellenprozess vom darunter liegenden Silizium entkoppelt, was stapelbare 3D-Speicher-Arrays ermöglicht.

Dafür sind aber 1S1R-Komponenten mit niedriger Spannung wichtig, damit sie kompatibel mit den I/O-Versorgungsspannungen in Logik-Chips sind (z. B. 1,8 V bei16 nm). In früheren Forschungsarbeiten wurde die Integration von STT-MRAM mit Schwellenwert-Selektoren auf Oxidbasis, einschließlich SiO-As und dotiertem HfOx, gezeigt. Die Forscher von TSMC gehen einen anderen Ansatz, denn sie nutzen für den Selektor ein neues Material: SiNGeCTe (ohne Arsen). Die Forscher konnten die Leistung ihres 1S1R-Bausteins im Spannungspulsbetrieb demonstrieren. Ihnen ist es zum ersten Mal gelungen, mehr als 109 störungsfreie Lesezyklen (mehr als 106 Schreibzyklen) bei einem 1S1R-STT-MRAM experimentell nachzuweisen. Außerdem wurde von TSMC gezeigt, dass sich der Speicher durch eine niedrige Spannung (unter 1,8 V), eine hohe Schaltgeschwindigkeit (Off-On/On-Off-Übergänge: 2,5 bzw. 3 ns), eine niedrige Schreibfehlerrate (unter 9 ppm bei 1,7 V/50 ns) und hohe Schreibzyklen (über 2M Zyklen) auszeichnet.

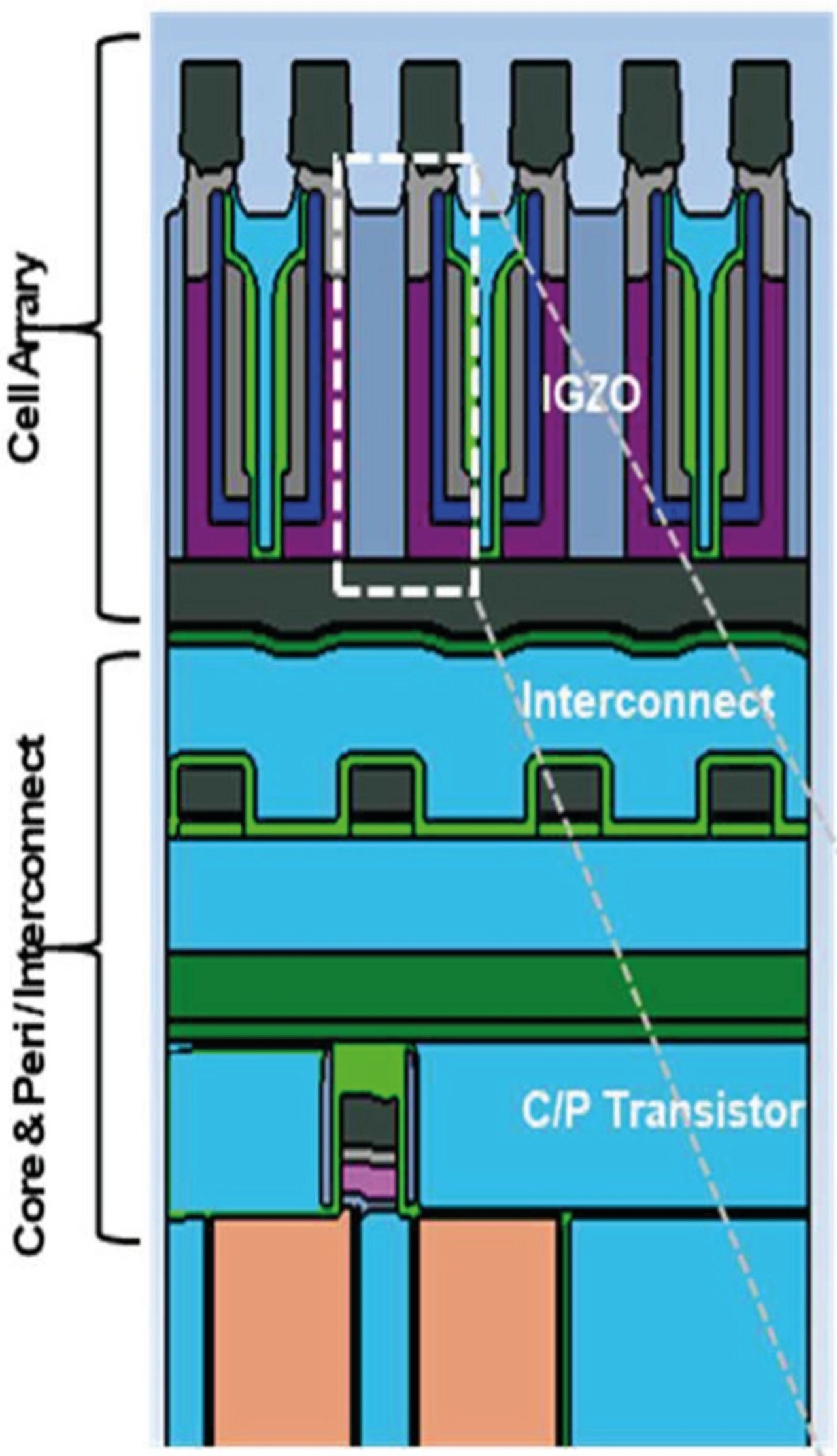

DRAM auf Basis von VTCs und IGZO

Auch im DRAM-Bereich werden die Entwicklungen hin zu kleineren Strukturen vorangetrieben. Denn DRAMs sind nun mal das Arbeitspferd elektronischer Systeme, aber eine Skalierung auf 10 nm und darunter ist alles andere als trivial. Bei fortgeschrittenen Knoten ist es äußerst schwierig, die extrem kleinen Strukturen herkömmlicher DRAM-Technologie auf Basis von BCATs (Buried-Cell-Array-Transistoren) mit einer Grundfläche von lediglich 6F2noch weiter zu skalieren und gleichzeitig elektrische Interferenzen von benachbarten Zellen oder Rowhammer- oder Passing-Gate-Effekte (PGE) zu unterdrücken.

Jobangebote+ passend zum Thema

Die Forscher von Samsung waren der Überzeugung, dass diese Probleme nur mit einer vollkommen neuen DRAM-Zellenstruktur in Kombination mit alternativen Kanalmaterialien wie IGZO (Indium-Gallium-Zink-Oxid) in den Griff zu bekommen sind. Auf der IEDM 2023 haben sie das Ergebnis ihrer Überlegungen gezeigt: Ein DRAM mit VTCs (Vertical-Channel-Transistoren), bei denen IGZO als Kanalmaterial verwendet wurde. IGZO zeichnet sich durch eine hohe Elektronenbeweglichkeit, geringe Leckströme und ein hohes Ein-/Aus-Verhältnis aus, was zu einem niedrigen Stromverbrauch führt und sich für die Verarbeitung bei niedrigen Temperaturen eignet.

Die Samsung-Forscher konnten auf der IEDM die erste erfolgreiche Integration eines 4F2-IGZO-VCT mit einfachem Gate präsentieren, die monolithisch auf Core-/Peripheral-Transistoren gestapelt wurden, und das Ganze ohne Wafer-Bonding. Die Samsung-Forscher sind überzeugt, dass sich dieser Ansatz für DRAM-Speicher eignet, die mit Prozessstrukturen von weniger als 10 nm gefertigt werden. Darüber hinaus heißt es seitens Samsung, dass sich die neue DRAM-Technologie durch einen geringen Leckstrom (IOFF <1 fA/Zelle), einen Unterschwellenhub (SS) von 164 mV/dec und eine angemessene Schwellenspannung (VT = –1,73 V bei 85 °C) auszeichnet. Die vertikale Architektur unterdrückt außerdem vollständig Rowhammer-Effekte, da der aktive Bereich nicht mit benachbarten Zellen geteilt wird.

NVDRAM für KI-Anwendungen

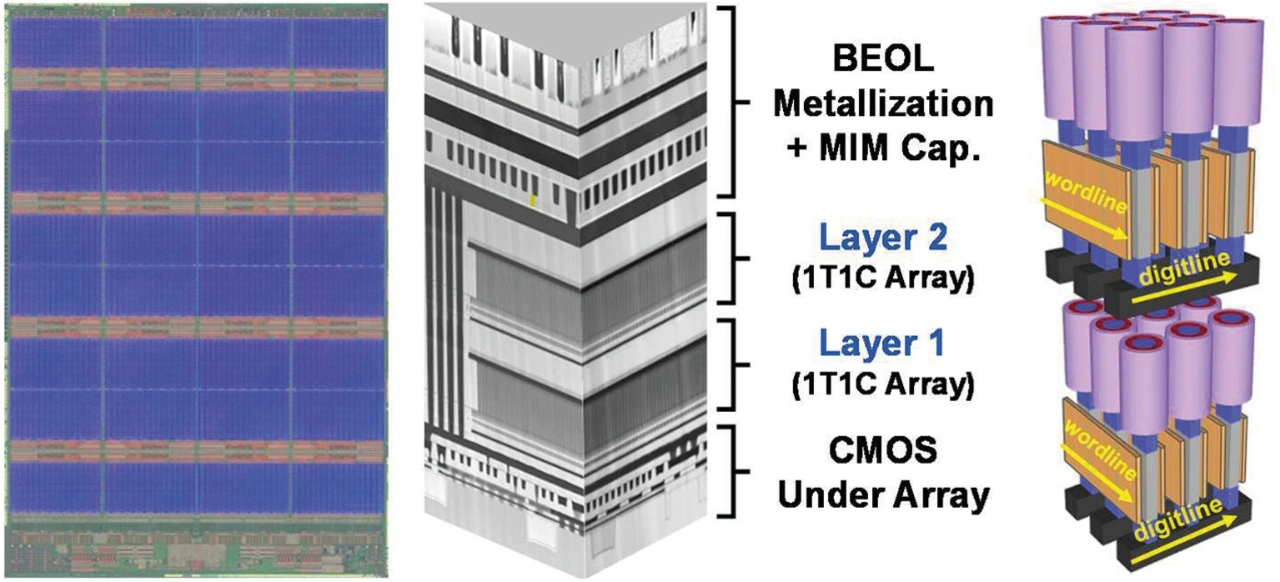

Das rasante Wachstum der Datenmodelle, die in Anwendungen der künstlichen Intelligenz (KI) und des maschinellen Lernens (ML) verwendet werden, führt zu einem dringenden Bedarf an Speicher mit größerer Bandbreite. Während neue Compute-Paradigmen wie Near-Memory-Compute und Processing in Memory erforscht werden, besteht die beste kurzfristige Chance darin, traditionelle Compute-Architekturen mit effizienterem Speicher auszustatten, um Daten schneller zu bewegen und größere Modelle unterzubringen.

Und genau darauf zielt ein Vortrag von Micron Technology ab. Forscher von Micron stellen eine neue Speichertechnologie für diese Anwendungen vor, die sie NVDRAM nennen. Dabei handelt sich um die weltweit erste zweilagige ferroelektrische Speichertechnologie, die stapelbar, leistungsstark, hochdicht (32 Gbit) und nichtflüchtig ist. Sie kombiniert die nichtflüchtige, auf langen Datenerhalt ausgelegten ferroelektrischen Speicherzellen mit DRAM-ähnlichen Lese-/Schreibgeschwindigkeiten und übertrifft außerdem die Zeit des Datenerhalts, die NAND-Speicher erreichen. Das NVRAM basiert auf einem sehr kleinen ferroelektrischen Kondensator (5,7 nm) als Speicherzelle und einem stapelbaren, polykristallinen Siliziumtransistor mit Dual Gate als Zugriffskomponente. Um eine hohe Speicherdichte zu erreichen, werden zwei Speicherschichten mit einer 4F2-Architektur und einem Pitch von 48 nm über einer CMOS-Schaltung angeordnet.

Micron kann die vollständige Ausbeute im Gehäuse für einen Temperaturbereich von –40 bis +95 °C nachweisen, zusammen mit einer Zuverlässigkeit von zehn Jahren, und das sowohl für den Datenerhalt als auch für die Schreibzyklen. Das entwickelte NVDRAM nutzt das LPDDR5-Befehlsprotokoll; die Systemkompatibilität wurde mit einer kommerziellen Entwicklungsplattform erfolgreich nachgewiesen. NVDRAM erreicht eine Bitdichte von 0,45 Gbit/mm2, die gemäß der Forscher sogar noch höher ist als die branchenführende, hauseigene 1-Beta-Planar-DRAM-Technologie.

Hohe Leistung, geringer Energieverbrauch

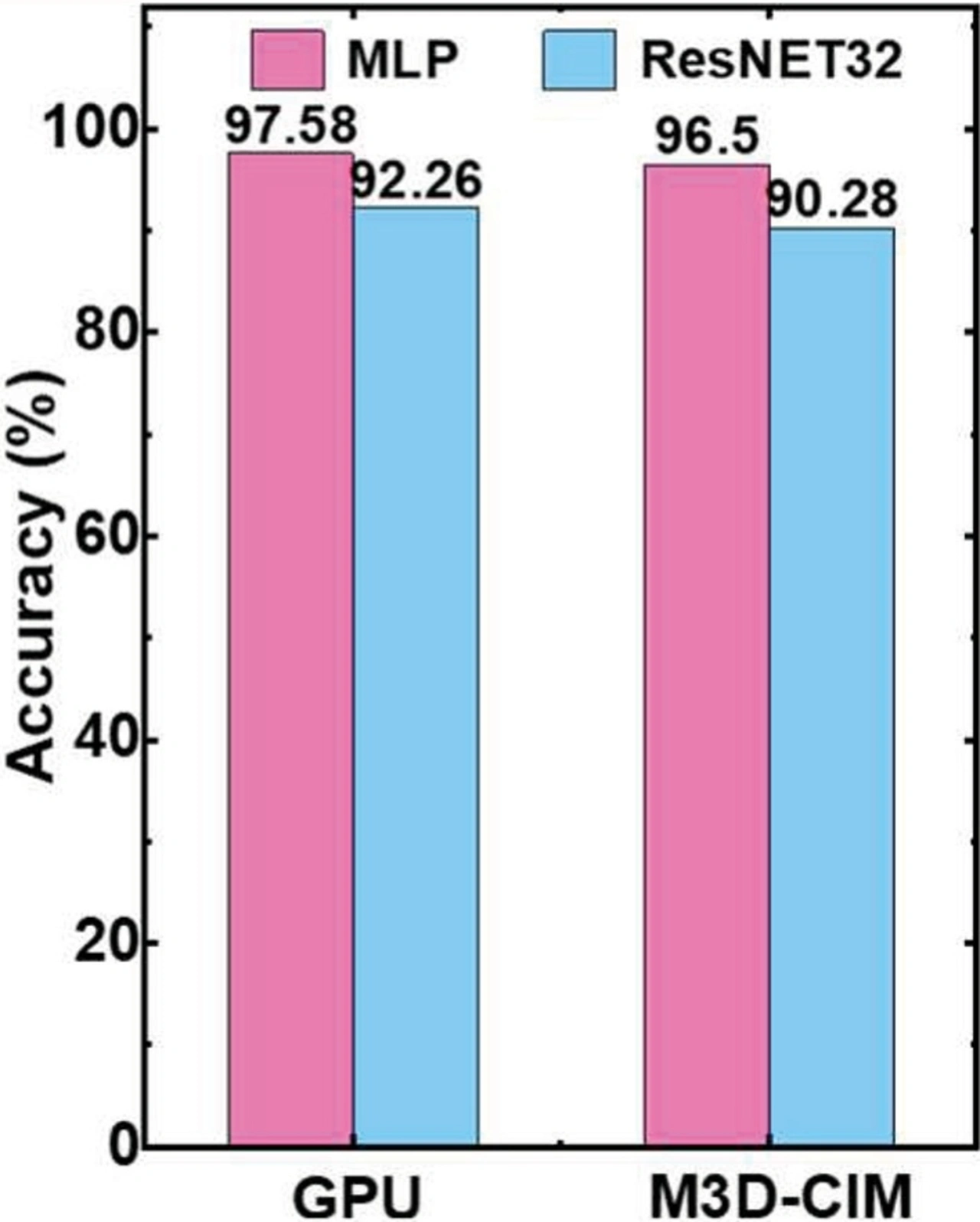

Ein Team, das von der Tsinghua-Universität geleitet wurde, hat eine monolithische 3D-Architektur vorgestellt, die eine GPU-ähnliche Genauigkeit erreicht, aber mit einem weitaus geringeren Energieverbrauch und einer deutlich kürzeren Inferenzzeit, und adressiert damit das Problem, dass groß angelegte KI-Modelle immer höhere Anforderungen an die Rechenleistung und Geschwindigkeit der Hardware stellen. Typische 2D-Compute-in-Memory-Architekturen (CIM) leiden unter Engpässen bei der Datenübertragung zwischen den verschiedenen CIM-Array-Schichten, die als Verarbeitungselemente verwendet werden. Das liegt daran, dass die Berechnungsergebnisse jeder Schicht einen On-Chip-Bus mit begrenzter Bandbreite nutzen müssen, um zwischen den CIM-Arrays und Puffern zu wechseln, was die Gesamtrechenzeit für tiefe neuronale Netze erheblich verlängert.

Das Team unter der Leitung der Tsinghua-Universität hat eine monolithische 3D-Bauelementarchitektur (M3d-CIM) entwickelt, bei der Puffer-Arrays direkt auf den CIM-Arrays angeordnet sind und über dichte, feinkörnige Vias verbunden sind, was die Bandbreite erhöht. Das 1-kbit-Array besteht aus drei Funktionsschichten: eine Si-CMOS-Logikschicht, ein RRAM-Array als CIM-Schicht und eine CNT-RRAM-Schicht für den Daten-Cache. Alle Komponenten und Schaltungen wurden charakterisiert, um zu bestätigen, dass jede Schicht wie vorgesehen funktioniert. Mit diesem Ansatz konnten die Forscher bei der Bildklassifizierung mit MLP- und ResNET32-Netzwerken eine GPU-äquivalente Genauigkeit von zirka 96,5 Prozent erreichen, wobei der Energieverbrauch um den Faktor 39 und die Inferenzzeit um den Faktor 49,6 geringer ausfallen.

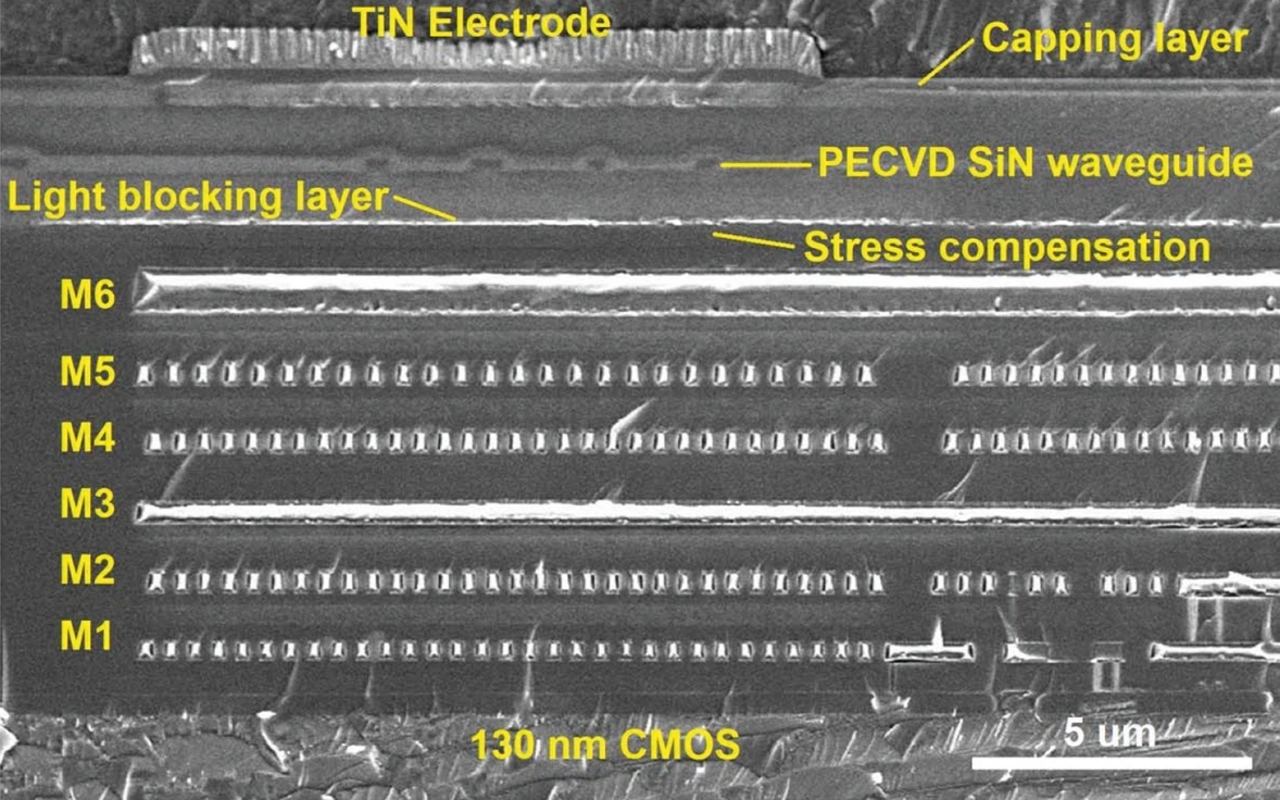

CMOS/Photonik-Plattform

Forscher vom imec haben eine monolithisch integrierte CMOS/Photonik-Plattform präsentiert, die passive und aktive Photonik im sichtbaren Bereich mit thermooptischen Schaltern unterstützen kann. Um die Fähigkeiten dieser Plattform zu demonstrieren, haben die Entwickler auf Basis dieser Plattform eine implantierbare CMOS-basierte neuronale Sonde realisiert, die das Gehirn optisch stimuliert und gleichzeitig elektrische Signale auslesen kann.

Die Plattform ist mit PECVD-SiN-Wellenleitern ausgestattet, die im BEOL (Back End of Line) integriert werden. Der Sondenstapel ist folgendermaßen aufgebaut: 130-nm-CMOS, sechs Metallisierungslagen, SC-Lage (SC: Stress-Compensation), LBL (Light-Blocking-Layer), WG-Schicht (Wellenleiter, Wave-Guide) und Schicht mit TiN-Elektrode. Die Forscher konnten mit diesem Aufbau eine Sonde realisieren, die aus einem hochdichten Array mit 960 auswählbaren Elektroden/384 Aufzeichnungskanälen mit 14 programmierbaren optischen Emissionsstellen für zwei sichtbare Wellenlängen (450 nm und 638 nm) besteht. Im Vergleich zu bisherigen multifunktionalen neuronalen Sonden mit optischen Übertragungs- und elektrischen Aufzeichnungsmöglichkeiten zeichnen sich die imec-Sonden durch die größte Anzahl von Emittern mit zwei Wellenlängen (eine 14-fache Verbesserung), eine um eine Größenordnung höhere Anzahl von Elektroden (>10-fache Verbesserung) und zum ersten Mal ein monolithisch integriertes Auslese-IC. Aus Sicht der Experten steht mit dieser Technologie ein leistungsfähiges Werkzeug für die Neurowissenschaft zur Verfügung, sie kann aber auch neue Möglichkeiten in anderen Anwendungen wie Biosensoren und Superauflösungsmikroskopen eröffnen.