Intern oder extern?

Renesas: Weiterentwicklung von Speicherarchitekturen

Wollen die Hersteller von IoT-Geräten die Funktionalität und Leistungsfähigkeit ihrer Systeme erhöhen, brauchen sie nicht nur mehr Rechenleistung, sie brauchen auch größere Speicher.

Die Nutzer von Edge-Geräten wollen mehr Funktionalität und Intelligenz. Entsprechend benötigen die Geräte mehr Rechenleistung und größere Speicher, denn nur so können die Edge-Geräte das Mehr an Funktionalität unterstützen. Und die Funktionen sind durchaus anspruchsvoll, denn dazu gehören ausgefeilte Grafiken und Benutzeroberflächen, Lernalgorithmen, Netzwerkkonnektivität und erweiterte Sicherheitsfunktionen.

Dazu kommt, dass maschinelles Lernen in jüngster Zeit die Integration von Sprach- und Bildverarbeitungsfunktionen in Edge-Geräte vorangetrieben hat. Damit ist es möglich, dass Geräte ohne menschliches Eingreifen intelligente Entscheidungen treffen und Aktionen in Edge ausführen können.

Damit steigt die Rechenleistung, aber auch der Bedarf an schnellen, zuverlässigen, energieeffizienten und nichtflüchtigen Speichern für Code und Daten. Denn bei der Entwicklung von Embedded-Systemen kann die Wahl des Speichers erhebliche Auswirkungen auf die Leistung, die Kosten, die Komplexität des Designs sowie die Leistungsaufnahme haben.

Es werden neue Architekturen benötigt, um den steigenden Anforderungen nach höherer Leistung, größerem Speicher und geringerem Stromverbrauch bei niedrigen Kosten gerecht zu werden. Eine enge Zusammenarbeit mit Speicherherstellern ist erforderlich, um vollständig verifizierte Lösungen zu gewährleisten, die die Leistungsanforderungen erfüllen.

Dieser Artikel beschreibt die gängigsten derzeit verwendeten Speicherarchitekturen sowie die verschiedenen möglichen Topologien.

Interner oder externer Speicher?

Interner Flash

Die meisten herkömmlichen General-Purpose-MCUs im unteren bis mittleren Leistungsbereich verwenden Embedded Flash (typischerweise weniger als 2 MB) als bevorzugten, nichtflüchtigen Speicher für Code. Diese integrierten MCUs eignen sich gut für zahlreiche IoT-Anwendungen in verschiedenen Marktsegmenten wie Industrie- oder Gebäudeautomatisierung, Medizintechnik, Haushaltsgeräte oder Smarthome. Embedded Flash bietet mehrere Vorteile wie geringere Latenz, niedrige Leistungsaufnahme oder hohe Performance und ermöglicht eine höher integrierte Lösung für einfachere, platzbeschränkte Anwendungen mit geringerer Designkomplexität. Mit Blick auf die Security zeichnen sich die MCUs mit Embedded Flash zudem dadurch aus, dass sie dank des internen Speichers keine zusätzliche Angriffsfläche bieten. Daher bleibt eine MCU mit integriertem Flash nach wie vor die bevorzugte Lösung für die meisten Anwendungen mit geringeren Leistungs- und Funktionsanforderungen.

Jobangebote+ passend zum Thema

Embedded Flash hat aber seinen Preis, ab einer bestimmten Speichergröße (z. B. über 2 MB) werden die Kosten zu hoch. Denn Embedded Flash ist teuer und erhöht die Komplexität sowie die Kosten der Fertigung der MCUs. Die zusätzlichen Prozessschritte, die für die Integration von Flash erforderlich sind, erhöhen die Siliziumkosten erheblich.

Zudem wechseln MCU-Hersteller im Zuge neuer Anwendungen mit höherer Leistung und Energieeffizienz zu fortschrittlicheren, kleineren Prozessgeometrien, wie 28/22 nm oder noch kleineren Strukturen. Mit diesen kleineren Strukturgrößen können wesentlich höhere Leistungen erreicht und mehr Funktionen auf dem Chip integriert werden. MCUs mit Taktraten von 400 MHz bis 1 GHz sind mittlerweile durchaus gängig, sie bieten Unterstützung für erweiterte Grafik-, Analog-, Connectivity- und Sicherheitsfunktionen sowie verbesserte Security-Features zum Schutz vor Daten-/IP-Diebstahl und -Manipulation. Während diese kleineren Prozessstrukturen die Leistungsanforderungen erfüllen, wird damit die Integration des Speichers in diese Bausteine aber zu einer Herausforderung, da sich Embedded Flash nicht gut skalieren lässt. Konkret: Die Flash-Zelle lässt sich nicht effizient unter 40 nm verkleinern, wodurch sie bei kleineren Prozessgeometrien weniger praktikabel oder teurer wird.

Kosten und technische Herausforderungen bei der Integration großer Flash-Speicher auf einem Chip zwingen Hersteller dazu, alternative Optionen für High-Performance-Anwendungen in Betracht zu ziehen.

Externer Speicher

Entsprechend werden neue Architekturen in Betracht gezogen, um diese Lücke zu schließen. Das heißt, dass zunehmend externer Flash-Speicher für anspruchsvollere und leistungsstärkere Anwendungen genutzt wird. Komplexere Anwendungsfälle wie High-End-Grafik, Audioverarbeitung oder maschinelles Lernen treiben diese Entwicklung voran. Dieser Trend wird außerdem durch einen starken Preisrückgang bei dedizierten Speichern begünstigt. Der Einsatz von externem Speicher ermöglicht die Erweiterung des Code- und Datenraums eines Embedded-Systems. Der externe Flash-Speicher wird dabei Teil des MCU-Speicherbereichs und kann somit direkt ausgelesen und für die Datenprotokollierung oder die Speicherung und Ausführung von Software verwendet werden.

Für Hersteller von IoT-Produkten bietet der Umstieg auf externe Flash-Speicher mehrere Vorteile, darunter die Flexibilität bei der Wahl der Speichergröße und die Zukunftssicherheit ihrer Designs. Wenn Entwickler mehr Funktionen hinzufügen, die einen größeren Speicher benötigen, ist es relativ einfach, einen kleineren Speicher durch einen größeren, pin-kompatiblen Speicherbaustein zu ersetzen. Außerdem können sie so einen einheitlichen Plattformansatz für ihre verschiedenen Designs verfolgen.

Zu den Nachteilen zählt die zusätzliche Latenz beim Zugriff auf den externen Speicher, die durch Quad/Octal-Speicher und einen sorgfältigen Einsatz von Caches verringert werden kann. Externer Flash erhöht aber auch die Leistungsaufnahme, und es entstehen zusätzliche Kosten. Darüber hinaus erhöht sich die Komplexität des Leiterplattendesigns, da zusätzliche Leiterbahnen notwendig sind und auf die Signalintegrität eine besondere Aufmerksamkeit gelegt werden muss.

MCU-Herstellern ermöglicht die Trennung von MCU und Speicher den Übergang zu kleineren Prozessknoten mit höherer Leistung, erweiterter Funktionalität, höherer Energieeffizienz und geringeren Kosten. Wie bereits erwähnt, ist Embedded-Speicher teuer und wird mit zunehmender Speicherkapazität unwirtschaftlich. Die meisten MCU-Hersteller integrieren mittlerweile Quad- oder Octal-SPI-Schnittstellen mit Unterstützung für »Execute-in-Place« (XiP), die eine nahtlose Verbindung mit NOR-Flash-Bausteinen ermöglichen. Einige MCUs unterstützen außerdem die Entschlüsselung im laufenden Betrieb (on the fly), sodass verschlüsselter Programm-Code in einem externen Flash gespeichert und sicher zur Ausführung geladen werden kann. Dieser Ansatz ermöglicht die hohe Leistung, die niedrige Leistungsaufnahme und die erweiterte Security, die für die Edge-Anwendungen von heute erforderlich sind (Bild 1).

Neben dem enormen Preisrückgang bei Standalone-Speichern gab es auch Fortschritte in der Speichertechnologie, die die Entwicklung hin zu externem Flash unterstützen. So nutzen externe Flash-Bausteine das Serial Peripheral Interface (SPI) für die Kommunikation mit der MCU und sind mit Quad- oder Octal-Schnittstellen mit einfacher oder doppelter Datenrate erhältlich. Damit erhöht sich die Bandbreite um das Vier- bzw. Achtfache. Die JEDEC-Spezifikation ermöglicht Frequenzen von bis zu 200 MHz, was eine Bandbreite von bis zu 400 Mbit/s erlaubt. Externe Speicher unterstützen die XiP-Funktionalität, die es ermöglicht, Code direkt aus dem externen Flash auszuführen, anstatt ihn in den internen SRAM zu kopieren und von dort auszuführen. Die Speicher unterstützen auch gleichzeitige Lese- und Schreibvorgänge (sogenanntes Read-While-Write oder RWW). Dadurch kann Code in einem Teil des Speichers aktualisiert werden, während Code in einem anderen Teil des Speichers ausgeführt wird. Serielle NOR-Flash-Speicher sind in verschiedenen Speichergrößen, Schnittstellen- und Gehäusevarianten erhältlich. Sie arbeiten typischerweise mit 1,8 oder 3,3 V und unterstützen 100.000 Schreibzyklen.

Herausforderungen mit externem Speicher und Lösungsansätze

Externe Speicher bieten viele Vorteile, aber sie weisen auch spezifische Herausforderungen auf. So gibt es zum Beispiel Bedenken hinsichtlich der mit externen Flash-Speichern verbundenen Latenz und ihrer Auswirkungen auf die Gesamtleistung. Diese Bandbreitenbeschränkung kann durch die Verwendung von Quad- oder Octal-SPI-Schnittstellen abgeschwächt werden. Damit lassen sich Daten über vier oder acht parallele Leitungen übertragen, im Gegensatz zu nur einer Leitung bei einer normalen SPI-Schnittstelle. Mit Double Data Rate (DDR) lässt sich der Durchsatz verdoppeln, weil Daten sowohl auf der steigenden als auch auf der fallenden Flanke des Taktsignals gesendet werden. Darüber hinaus unterstützen viele externe Flash-Speicher den Burst-Lesemodus für einen schnelleren Datenzugriff, was die Latenzzeiten ebenfalls verkürzt. Auch Caches können eingesetzt werden, um einige der Latenzeffekte abzuschwächen. Allerdings ist dafür ein sorgfältiges Software-Management erforderlich, sodass die Caches auch optimal genutzt werden können. Darüber hinaus können Systementwickler auch selbst einige Latenzprobleme lösen, indem sie den Code in den internen SRAM übertragen und dort ausführen.

Es gibt aber auch Bedenken, dass mit externem Flash die Leistungsaufnahme steigt. Die Hersteller von Flash-Speichern achten aber besonders auf die Optimierung der Leistungsaufnahme ihrer Bausteine. So senken sie die Leistungsaufnahme beispielsweise mit dem XiP-Modus, verschiedenen Energiesparmodi und schnellen Wake-up-Zeiten sowie mithilfe verschiedener I/O-Designtechniken für eine geringere Leistungsaufnahme.

Externe Speicher bergen einige Sicherheitsrisiken, denn ihr Einsatz schafft eine zusätzliche Angriffsfläche. Diese Schwachstelle kann von Hackern ausgenutzt werden und muss deshalb geschützt werden. Dies erfordert, dass MCU-Hersteller die Quad/Octal-SPI-Schnittstelle mit einer Ver-/Entschlüsselungsfunktion ausstatten. Damit lässt sich verschlüsselter Code sicher speichern und übertragen.

Externer Flash mit RA MCUs

Die MCUs der RA-Familie von Renesas verfügen über integrierten Flash-Speicher und mehrere Speicherschnittstellen zu externen Speichern, um maximale Flexibilität und Leistung zu bieten. Sie unterstützen entweder Quad- oder Octal-SPI-Schnittstellen für einen höheren Datendurchsatz, indem sie vier oder acht Datenleitungen anstelle der üblichen einen Datenleitung der SPI-Schnittstelle verwenden. Dies steigert die Leistung in Anwendungen, die schnelle Speicherzugriffe erfordern, wie z. B. Grafik, Audio oder Datenprotokollierung.

Alle Mikrocontroller der RA8-Serie sind mit einer Octal-SPI-Schnittstelle ausgestattet, die dem xSPI-Standard (eXpanded Serial Peripheral Interface) entspricht. Dieser Standard spezifiziert die serielle Schnittstelle zu nichtflüchtigen Speicherbausteinen und erlaubt hohe Übertragungsraten bei gleichzeitig reduziertem Signalbedarf. Zudem bietet er eine begrenzte Abwärtskompatibilität zu älteren SPI-Bausteinen.

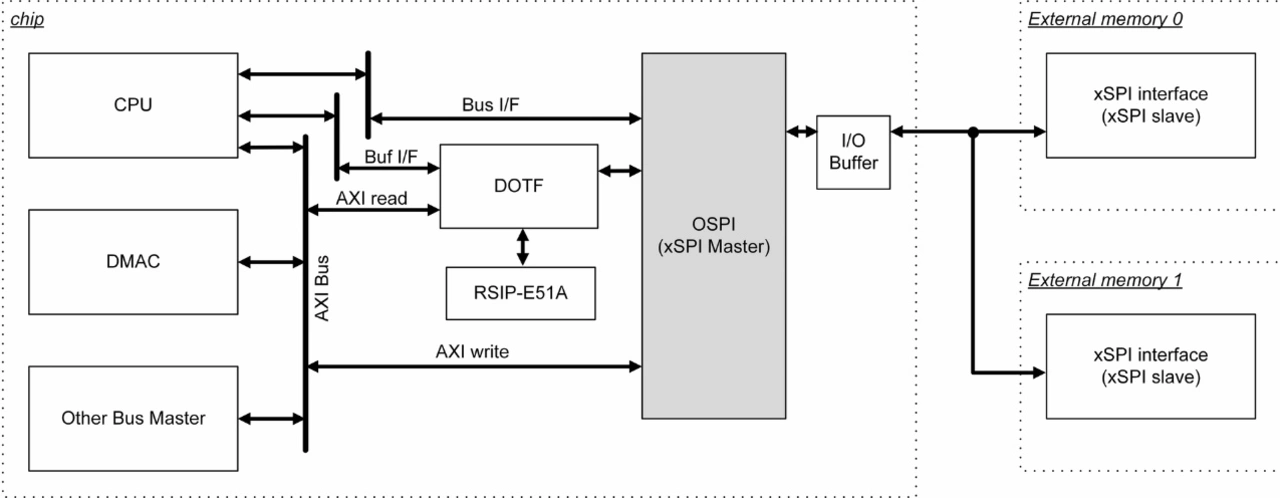

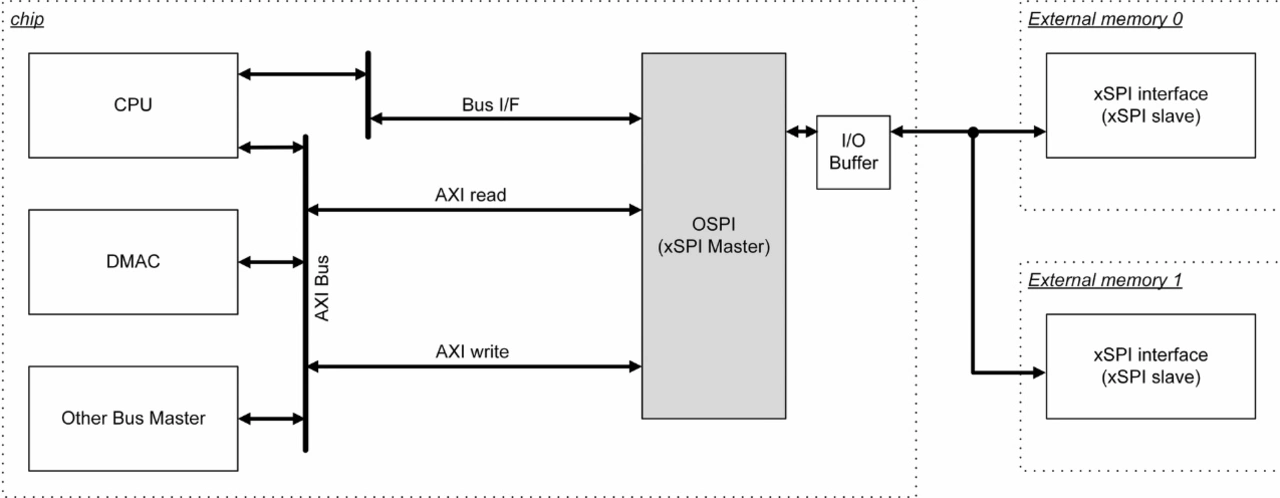

Die xSPI-Schnittstelle erfüllt die JEDEC-Standards JESD251 (Profile 1.0 und 2.0), JESD251-1 und JESD252. Damit lässt sich ein Rohdatendurchsatz von bis zu 200 MByte pro Sekunde erreichen. Bei einigen RA8-MCUs unterstützt die Octal-SPI-Schnittstelle auch Decryption-on-the-Fly (DOTF). Damit kann verschlüsselter Code, der in einem externen Flash-Speicher abgelegt ist, während des Ladens entschlüsselt und sicher zur Ausführung bereitgestellt werden. Die Abbildungen zeigen die Octal-SPI-Schnittstelle auf den RA8-MCUs mit und ohne DOTF. Zwei externe Speicher können per Chip-Select-Signale an die Octal-SPI-Schnittstelle angeschlossen werden, wie die Bilder 2 und 3 zeigen, sodass Entwickler maximale Flexibilität erhalten.

Die Octal-SPI-Schnittstelle auf RA8-MCUs unterstützt Execute-in-Place (XiP) und kann mit bis zu zwei Slaves über Chip-Select-Signale kommunizieren. Die unterstützten Modi sind:

- 1/4/8 Anschlüsse mit SDR/DDR (1S-1S-1S, 4S-4D-4D, 8D-8D-8D)

- 2/4 Anschlüsse mit SDR (1S-2S-2S, 2S-2S-2S, 1S-4S-4S, 4S-4S-4S)

Unterstützte Speichertypen sind Octal Flash und Octal RAM sowie HyperFlash und HyperRAM. Die Octal-SPI-Schnittstelle kann pro CS (Chip Select) einen Adressraum von bis zu 256 MB ansprechen. Sie bietet außerdem eine Prefetch-Funktion für Burst-Reads mit niedriger Latenz sowie den entsprechenden Puffer für Burst-Writes mit hohem Datendurchsatz.

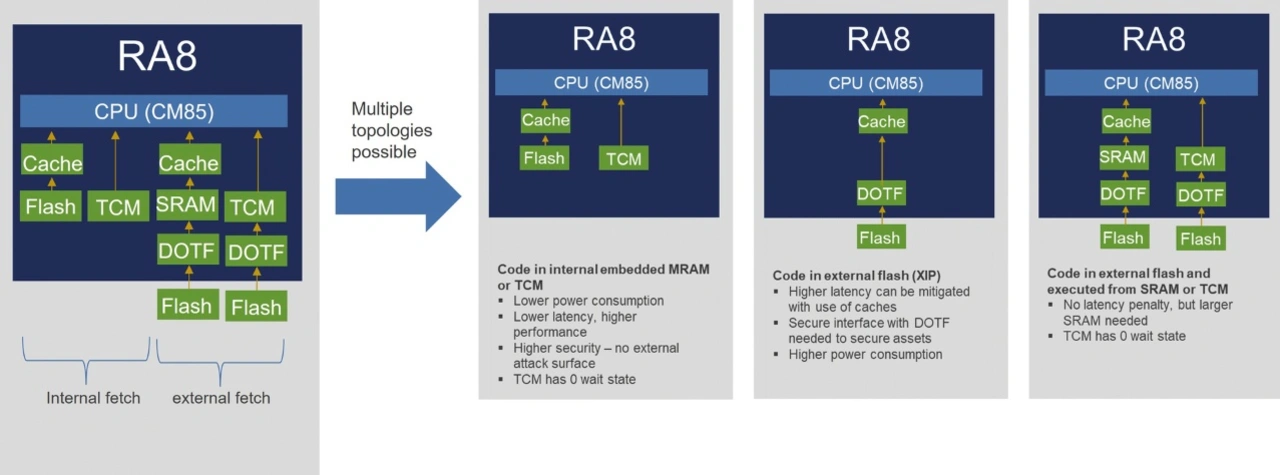

Zusätzlich zu internem Flash und externen Speicherschnittstellen enthalten die RA8-MCUs auch TCM (Tightly Coupled Memory) und I/D-Caches (Befehls- und Daten-Caches), die zur Leistungsoptimierung beitragen. Der TCM ist ein interner Speicher ohne Wartezyklen und bietet die niedrigste Latenz aller On-Chip-Speicher. Daher eignet er sich besonders gut für die zeitkritischsten Teile des Codes.

Speicher-Topologien

Die RA8-MCUs ermöglichen flexible Speicherkonfigurationen, die mit internen und externen Speichern und integrierten Speicherschnittstellen (Bild 4) realisiert werden können.

In der Standardkonfiguration wird der Code im Embedded Flash gespeichert und direkt daraus ausgeführt. Dies ermöglicht ein einfaches, leistungsfähiges, sicheres und energieeffizientes System mit geringer Latenz. Wächst die Größe des Codes über die Kapazität des Embedded-Flash-Speichers hinaus, sind externe Speicher notwendig.

In der zweiten Konfiguration liegt der Code in einem externen Flash-Speicher und wird dank XiP-Fähigkeit (Execute in Place) direkt von dort ausgeführt. Der Ansatz ist flexibel und skalierbar. Übersteigt die Codegröße die Kapazität des externen Speichers, kann dieser durch einen pin-kompatiblen Baustein mit höherer Speicherdichte ersetzt werden. Dies ermöglicht eine kostenoptimierte Lösung, die einfach skalierbar ist, ohne dass das Board neu entworfen werden muss. Nachteil: Die Leistungsaufnahme und die Latenzzeiten steigen leicht an, was sich negativ auf die Systemleistung auswirken kann.

Bei der dritten Konfiguration wird der Code in einem externen Flash-Speicher gespeichert und zur Ausführung in das interne SRAM oder TCM geladen. Dies ermöglicht die höchste Leistung, da der Code aus dem schnellen SRAM ausgeführt wird. Allerdings ist die Codegröße durch die SRAM-Größe begrenzt, und die Software-Komplexität steigt, wenn die Codegröße das verfügbare SRAM oder TCM überschreitet. Auch die Aufwachzeiten können sich verlängern, da der Code beim Shutdown des SRAM verloren geht und bei jedem Einschalten neu geladen werden muss.

Fazit

Während die meisten IoT-Anwendungen im unteren bis mittleren Leistungsbereich internen Flash-Speicher verwenden können, gibt es leistungsstärkere Anwendungen, die externe Flash-Speicher benötigen.

Die Entscheidung für eine Speicherarchitektur hängt von mehreren Faktoren ab, einschließlich Anwendungsanforderungen, benötigter Speichergröße, Systemarchitektur, gewünschter Leistungsaufnahme, Sicherheitsbedenken und zukünftigen Produkt-/Plattform-Roadmaps. Beide Optionen haben Vor- und Nachteile. Interne Flash-Speicher sind einfach und ermöglichen eine integrierte, sehr sichere Lösung, die für viele Anwendungen geeignet ist. Externe Flash-Speicher bieten Flexibilität, eine einfache Speichererweiterung und Skalierbarkeit für neue IoT- und Edge-KI-Anwendungen. Durch das Verständnis und die Abwägung der Vor- und Nachteile können Entwickler fundierte Entscheidungen treffen, die bestmöglich auf ihre Projektziele abgestimmt sind.