Anforderungen an IoT-Mikrocontroller

Energiesparend, schnell, sicher

Fortsetzung des Artikels von Teil 1

Eine programmierbare Architektur als Grundlage

Die Mikrocontroller PSoC 6 von Cypress Semiconductor bauen auf denselben programmierbaren Bausteinen auf wie andere Mitglieder der PSoC-Familie: Software-definierte digitale und analoge Peripherieblöcke, die der Anwender – normalerweise im Entwicklungswerkzeug PSoC Creator – so konfigurieren kann, dass sich eine enorme Zahl verschiedener Funktionen implementieren lässt. Die analoge Peripherie kann als analoge Eingangsstufe zum Anschluss von Sensoren konfiguriert werden. Mit der digitalen Peripherie lassen sich Kommunikationsschnittstellen, Timer/Zähler/PWM oder Logikfunktionen implementieren.

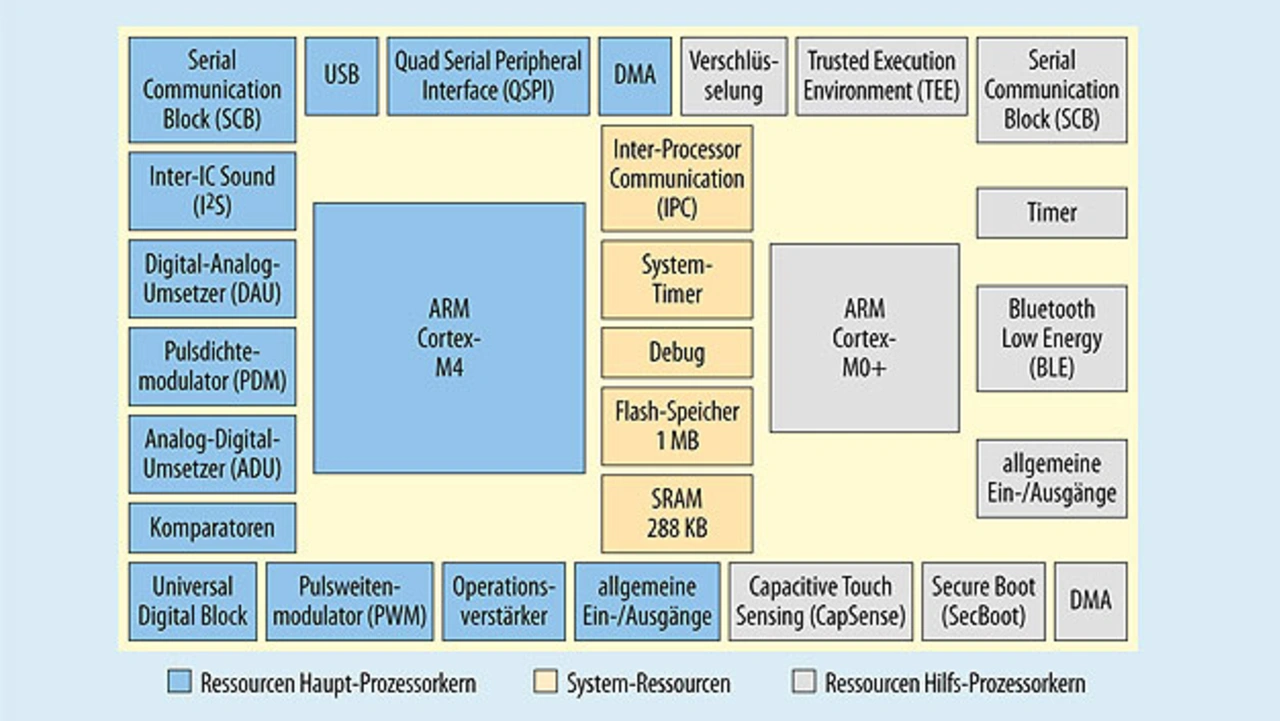

Bei der Mikrocontroller-Architektur PSoC 6 werden die konfigurierbaren Peripherieblöcke durch die grundlegenden Systemressourcen, die im Chip fest verschaltet sind, unterstützt. Dazu gehören

- Systemspeicher,

- ein Cortex-M-Prozessorkern von ARM,

- Ein-/Ausgänge und programmierbare Verbindungen.

Allgemein verbreitete Peripherie, z.B. eine USB-Schnittstelle und die kapazitive Berührungserkennung CapSense, sind ebenfalls in den PSoC-Schaltkreisen integriert.

Frühere ICs wie PSoC 4 und PSoC 5 werden in einer Vielzahl von Anwendungen eingesetzt und bieten dort folgende Vorteile:

- die Flexibilität einer programmierbaren Architektur, die es besonders einfach macht, Systemfunktionen an jedem Punkt des Entwicklungsprozesses zu ändern, ohne das Layout der Leiterplatte überarbeiten zu müssen

- die große Auswahl an leistungsfähigen analogen Schnittstellen und Funktionen

Mit PSoC 6 hat Cypress nun eigens einen Baustein für das IoT mit dem Ziel entwickelt, Fähigkeiten und Eigenschaften anzubieten, die besser sind als das, was den Anwendern von Mikrocontrollern bisher zur Verfügung steht. Diese grundlegende Überarbeitung der PSoC-Struktur hat bei der Prozesstechnik begonnen: PSoC 6 ist das erste PSoC, das in 40-nm-Fertigungstechnik für eine äußerst niedrige Energieaufnahme hergestellt wird.

Jobangebote+ passend zum Thema

Cypress führt mit PSoC 6 eine weitere Neuerung bei der Architektur ein: ein Dual-Core-Mikrocontroller mit einem Cortex-M4-Prozessorkern hoher Rechenleistung von ARM, der mit einer Taktfrequenz bis zu 150 MHz arbeitet, und einem energiesparenden zweiten Prozessorkern des Typs Cortex-M0+, ebenfalls von ARM (Bild 1). Die Implementierung dieser zwei Prozessorkerne im 40-nm-Prozess ermöglicht eine in dieser Klasse unübertroffene Leistungsfährigkeit bei niedrigem Energiebedarf. Der PSoC 6 bietet einen Low-Power-Active-Modus, in dem der Cortex-M4-Kern nur 22 µA/MHz und der Cortex-M0+-Kern sogar nur 15 µA/MHz aufnimmt. Bei Mikrocontrollern anderer Halbleiterhersteller, die ebenfalls auf dem Cortex-M4-Kern von ARM aufbauen, ist die Stromaufnahme im Betrieb gewöhnlich mehr als dreimal so hoch.

Die Leistungsvorteile dieser flexiblen Architektur reichen natürlich noch weiter, da die Systemfunktionen aufgeteilt werden können. So können beispielsweise in einem Funksensor die Funktionen der Sensorschnittstelle und der Sensorsteuerung, die nur eine geringe Rechenintensität haben, aber ständig laufen müssen, auf dem Cortex-M0+-Kern ausgeführt werden, während sich der leistungsstärkere Cortex-M4-Kern im Schlafmodus befindet. Dabei kann der Cortex-M4-Kern in regelmäßigen Abständen geweckt werden, um kurzzeitig rechenintensive Aufgaben, wie die Verarbeitung zwischengespeicherter Sen¬sordaten vor der Übertragung zum Cloud Server, auszuführen. PSoC 6 arbeitet zudem mit einer dynamischen Skalierung von Frequenz und Spannung, um Leistung und Durchsatz zu optimieren.

Diese Aufteilung der Funktionen ermöglicht es, hohe Rechenleistung und großen Funktionsumfang mit äußerst geringem Energiebedarf zu kombinieren.

Sicherer Speicher auf dem Chip

Sowohl Fortschritte in der Architektur als auch im Fertigungsprozess machen die Kombination aus Rechenleistung und niedriger Energieaufnahme möglich, die bei ständig aktiven Anwendungen in IoT-Endknoten benötigt wird. Das IoT verlangt außerdem Fähigkeiten zur Datensicherheit, um Daten, die Privatsphäre des Anwenders, Systeme und Netzwerke zu schützen.

Bei PSoC 6 dient hierzu ein „Trusted Execution Environment“ (TEE), das auf dem Chip mehrere gleichzeitig nutzbare, sichere Speicherbereiche für „Trusted Applications“ bietet. Das TEE stellt skalierbare, sichere Speicher- und Prozessorressourcen für die Implementierung mehrerer vom Benutzer definierter und voneinander unabhängiger Sicherheitsstrategien bereit, ohne dass hierzu externe sichere Speicher oder Sicherheitsbausteine benötigt werden.

PSoC 6 unterstützt zudem die in der Industrie verbreiteten kryptografischen Algorithmen, einschließlich ECC (Elliptic Curve Cryptography) und AES (Advanced Encryption Standard), in integrierten Hardware-Koprozessoren und verfügt über einen sicheren internen Speicher für Firmware, Anwendungen und Sicherheitselemente wie kryptografische Schlüssel. Die sichere Speicherung wird durch eine Mikro-Schmelzsicherung (eFUSE) geschützt, die, wenn sie zerstört wird, den Debug-Anschluss sperrt, sodass der Inhalt des sicheren Speichers mit einem Debugger nicht ausgelesen werden kann.

Im PSoC 6 wurde darüber hinaus ein optionaler sicherer Boot-Prozess implementiert, bei dem das Image der Anwendung anhand eines im sicheren Speicher im Chip abgelegten Image authentifiziert wird.

Funkschnittstellen auf dem Chip

PSoC 6 erfüllt außerdem alle Anforderungen zur Kommunikation moderner IoT-Entwicklungen. Mit der Serie PSoC 63 kann der Anwender eine Komponente wählen, die für Funk oder leitungsbebundene Kommunikation optimiert ist und auf dem Chip eine USB-2.0-Schnittstelle bietet, oder eine Komponente, die für BLE optimiert ist und im Chip einen 2,4-GHz-HF-Transceiver enthält und den Standard BLE 5.0 unterstützt. Dieser IC mit BLE, der auch CapSense unterstützt und analoge Peripherie enthält, zu der zwei Operationsverstärker, zwei Komparatoren, ein 12-bit-A/D-Umsetzer und ein 12-bit-D/A-Umsetzer gehören, bietet Möglichkeiten, für die in früheren Entwicklungen vier ICs benötigt wurden: ein leistungsfähiger Mikrocontroller, ein BLE-HF-Chip, ein Sensor-Controller mit niedriger Leistungsaufnahme und ein weiterer Controller für die Berührungserkennung.

Ressourcen für Evaluierung und Entwicklung

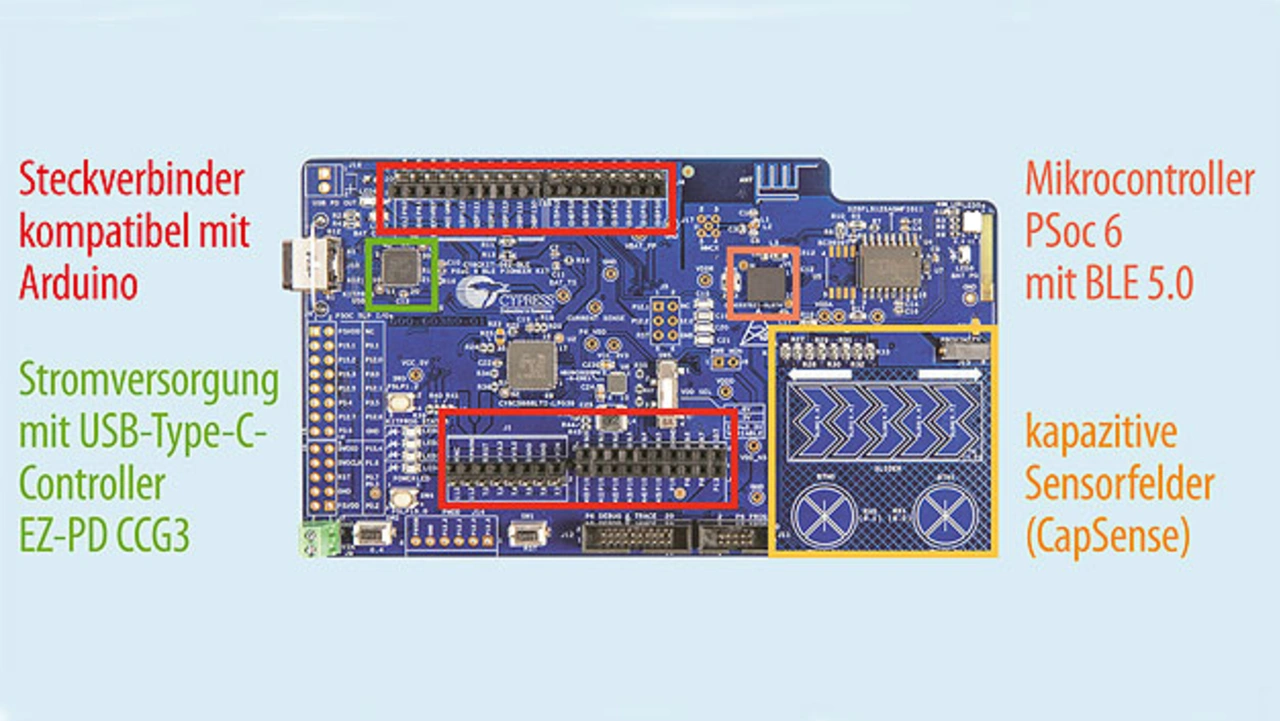

Die Kombination aus äußerst geringem Energiebedarf, hoher Prozessorleistung, Sicherheitsfunktionen und auf dem Chip integrierten Schnittstellen beim PSoC 6 ist damit ideal für die Anforderungen der IoT-Endknoten von morgen. Die Entwickler können diese Fähigkeiten mit dem PSoC 6 BLE Pioneer Kit [1] erkunden, das im Laufe des Jahres 2017 verfügbar sein wird. Das Modul (Bild 2) umfasst ein Dual-Core PSoC 6, BLE, Antenne, berührungsempfindliche Schieberegler, Tasten und einen Näherungssensor, einen USB-Typ-C-Controller mit entsprechender Buchse sowie Steckerleisten für Arduino Uno Shields.

Literatur

[1] PSoC 6: Purpose-built for the IoT. Cypress, PSoC 6 BLE Pioneer Kit CY8CKIT-062-BLE, www.cypress.com/event/psoc-6-purpose-built-iots.

Der Autor

| Michiyuki Yoneda |

|---|

ist als Senior Product Marketing Engineer im Bereich Mikrocontroller bei Cypress Semiconductor tätig. Er hat mehr als zehn Jahre Branchenerfahrung in Anwendungen und im Marketing und kennt sich mit der kapazitiven Touch-Sensorik und Mikrocontrollern für den Einsatz in Konsumgeräten und IoT-Geräten aus. Sein Studium an der Boston University, College of Engineering, hat er mit dem Bachelor abgeschlossen. |

michiyuki.yoneda@cypress.com

- Energiesparend, schnell, sicher

- Eine programmierbare Architektur als Grundlage