Validierung von Prototypen – Teil 1

Portierbare Stimuliermethode für Post Silicon Validation

Der Portable Stimulus Standard (PSS) wurde geschaffen, um Testzweck und Testverhalten für den Einsatz auf unterschiedlichen Zielplattformen zu spezifizieren. Im ersten von zwei Teilen wird gezeigt, wie ein PSS-basierter Traffic-Generator in einer SystemC-basierten Leistungsanalyse eingesetzt wird.

Verifizierungstechniken und -methoden wurden ständig weiterentwickelt, da die Anforderungen an den Entwurf immer komplexer wurden. Der Portable Stimulus Standard (PSS) ist die neuste Entwicklung in diesem Evolutionsprozess. Er wurde geschaffen, um die Herausforderungen an die Portabilität von Tests anzunehmen. Der neue PSS erlaubt die Erstellung des Testzwecks derart, dass dieser über unterschiedliche Zielplattformen immer wieder verwendet werden kann.

Zusammen mit dieser Portierbarkeit bieten die PSS-basierten Verifizierungstechniken auch Vorzüge bei der visuellen Testrepräsentation, dem Erstellen von Einschränkungen (Constraints), der Datenfluss-basierten Randomisierung sowie der Testqualität. Mit der Adaption von PSS-basierten Techniken gibt es nachfolgende Prozessänderungen in der Verifikation von SoCs, und es ist wichtig, deren Einfluss zu verstehen. In diesem Fachaufsatz werden Prozessänderungen anhand der Fallstudie einer Interconnect-Bus-Fabric untersucht, von der SystemC-basierten Leistungsanalyse bis hin zur Verifizierung und Validierung.

Jobangebote+ passend zum Thema

Einsatz von PSS im Entwicklungsprozess

Da IC-Entwürfe immer komplexer werden, werden Prozessänderungen wie SystemC-basierte Modellierung, Architekturexplorationen und High-Level-Synthese (HLS) neben den traditionellen Entwicklungs- und Integrationsabläufen immer üblicher. Diese Prozessänderungen erfordern wiederum, dass die Einhaltung der Anforderungen der IC-Entwicklung überprüft wird.

Unterschiedliche Entwicklungsteams, die in diesen Prozess eingebunden sind, nutzen unterschiedliche Plattformen und Sprachen, um diese Änderungen zu unterstützen. Aber, trotz all dieser Unterschiede, sind die Basisspezifikationen in jedem nachfolgenden Prozess gleich, was zu einer Menge an doppeltem Aufwand führt.

Das Team zur Entwicklung der Architektur erstellt eine virtuelle Plattform zur Untersuchung dieser Architektur und die Softwareentwicklung nutzt dazu eine SystemC- und TLM-basierte (Transaction Level Modelling) Modellierung. Das Komponenten-Design-Team entwickelt die Verilog-Komponenten auf Funktionsblockebene und integriert sie, entweder manuell oder mit einem automatischen Prozess, um ein System aufzubauen. Die Verifizierung auf IP-Ebene erfolgt üblicherweise mit der UVM-basierten (Universal Verification Methodology) Verifizierung, während auf Systemebene eine Kombination aus C- und UVM-basierten Methoden angewandt wird.

Die UVM-Umgebung erlaubt es, die Checker aus der IP-Ebene einfach in der Systemebene wiedereinzusetzen, allerdings wird der Teststimulus häufig in der Top-Ebene der UVM-Umgebung oder C neu geschrieben, um den Prozessor auf Chipebene laufen zu lassen.

Der Aufwand um Tests zu erstellen, die Start-up/Konfiguration und die grundlegende Arbeitsweise der Funktionsblöcke zu verifizieren wird für den Test der aktuellen Bausteine wiederholt, wenn neue Tests für die Testplattform erforderlich sind, oder diese auf einem Evaluierungs-Board ablaufen. Anschließend haben die Softwareteams erneut den Aufwand, die Softwaretreiber für das Kundeninterface zu schreiben.

Diese Duplizierungen des Aufwands der unterschiedlichen Teams, die verschiedene Programmiersprachen und Techniken verwenden, resultiert in häufigen falschen Fehlerreports und beeinflussen die Markteinführungszeit insgesamt signifikant. Es wird deshalb eine bessere Lösung benötigt, die es den Testprogram- mierern im gesamten Projekt erlaubt eine gemeinsame Sprache zu sprechen, und die es ermöglicht, einen Großteil der einfachen Tests zu funktionellen Verifizierung sowohl horizontal als auch vertikal nahtlos wiederzuverwenden. Diese Methode ist exakt das, was die PSS-basierten Verifikationstechniken in das Design einbringen.

Der PSS definiert eine neue Sprache zum Schreiben von Tests, die eine automatische Erstellung von Tests erlaubt, die darauf abzielen, aus einer einzigen Testquelle auf unterschiedliche Plattformen abzulaufen. Zusätzlich zur horizontalen Wiederverwendung (Simulierung, Emulation, Board-Ebene, Tester etc.), erlaubt die neue Programmiersprache auch die vertikale Wiederverwendung der Tests. Diese auf IP-Ebene entwickelten Tests können auf SoC-Ebene einfacher inte-griert und erneut verwendet werden.

Der portierbare Teststimulus arbeitet auf einer höheren Abstraktionsebene, die völlig unabhängig von der Art der Zielplattform ist. Diese Zielplattformen können dabei eine UVM-basierte Verifizierungsumgebung, eine C/C++-basierte sowie eine SoC-basierte Umgebung, eine auf C und Python basierte Post-Silicon-Evaluierungs-Plattform usw. sein.

Eine PSS-basierte Applikation bietet ausgezeichnete Möglichkeiten zur Erstellung von generischen Anwendungen, die verwendet werden können, den Testzweck auf unterschiedlichen Ebenen zu verifizieren. Die gleiche Möglichkeit hat man, wenn man eine Interconnect-Bus-Fabric in einem SoC mit mehreren Prozessoren einsetzt. Es gibt dabei verschiedene Ebenen, die man benötigt, um die Funktion und die Leistung zu verifizieren und zu evaluieren.

Die Interconnect-Bus-Fabric muss entsprechend den spezifischen Anforderungen des SoCs sorgfältig ausgesucht werden und es ist auch eine frühe Leistungsanalyse nötig, die mit Systemmodellen (typisch in C/SystemC) durchgeführt werden kann. Dies erfordert das Erstellen von Prüfungen, die diese Systemmodelle verifizieren können. Ist die Wahl der Konfiguration erfolgt und RTL generiert, müssen sie auf IP-Ebene verifiziert werden. Dies erfordert eine UVM-basierte Verifikation und UVM-Sequenzen, um das Ganze zu bestätigen. Anschließend wird das generierte RTL in die SoC-Systemebene integriert und muss auf SoC-Ebene verifiziert werden. Dies wird üblicherweise gemacht, indem man Tests in C/C++ zur Verifikation und Validierung codiert.

Alle diese Applikationen zur Verifizierung der Verbindungen können mit der Erstellung von wiederverwendbaren Tests gehandhabt werden, die PSS-basierte Techniken verwenden. Um dies zu erreichen, wurde ein PSS-Modell für einen generischen Traffic-Generator erstellt, der unterschiedliche Schreib- und Lesepattern für eine unterschiedliche Anzahl von Mastern kreieren kann. Dieser Traffic-Generator kann Datenverkehr mit unterschiedlicher Verteilung auf jeden Master erzeugen, sodass sowohl schnelle wie auch langsame Master emuliert werden können.

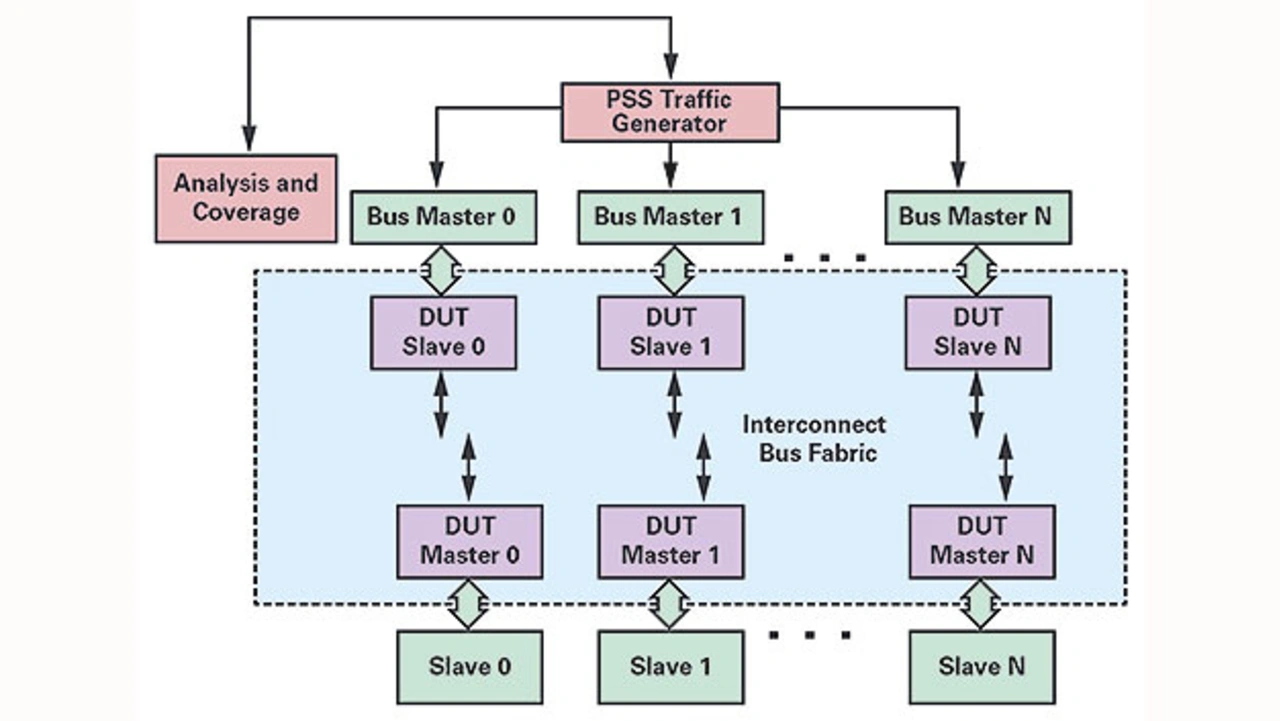

Der Entwicklungsprozess kann auch unabhängig steuern, welcher Master mit welcher Frequenz Datenverkehr erzeugt sowie ebenso fortlaufende und verzögerte Transaktionen. Bild 1 zeigt den Prozessablauf mit einem PSS-basierten Traffic-Generator. Die Funktionsblöcke in violetter Farbe repräsentieren den Interconnect-Bus mit den generischen Slaves und Mastern, wogegen die Blöcke in Grün die RTL (Register-Transfer Level) oder Verhaltensmodelle darstellen, die die Transaktionen auf dem Bus treiben.

Der PSS-basierte Traffic-Generator (dargestellt in Pink) integriert und steuert diese Funktionsblöcke, um Transaktionen zu treiben und zu sammeln. Der Traffic-Generator verwaltet verschiedene Anforderungen an die Generierung von Datenverkehr und erstellt Tests für unterschiedliche Ziele wie z.B. SystemC-basierte Applikationen sowie UVM- (Universal Verification Methodology) und C-basierte Tests. Jeder Prozess muss dabei bezüglich Integration und Testerstellung unterschiedlich gehandhabt werden, was in den folgenden Absätzen beschrieben wird.

- Portierbare Stimuliermethode für Post Silicon Validation

- System-C-basierte Leistungsanalyse des Interconnect-Busses