Designtools / FinFET-Design

Parasitärextraktion für fortgeschrittene FinFET-Technologien

Fortsetzung des Artikels von Teil 6

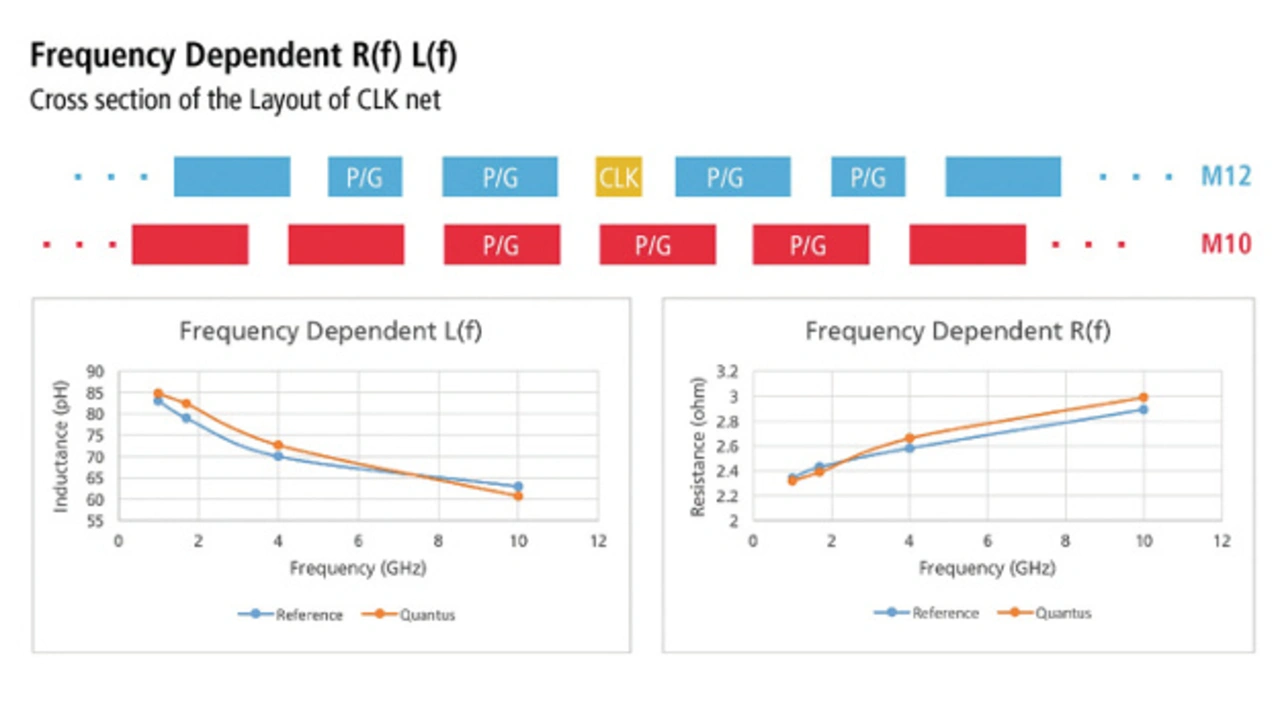

Induktivitäts-Extraktion bei digitalen Clock-Netzen

Clock-Netze (CLK) nutzen ein breites Leitungsrouting, um große Chipflächen abzudecken. Dies reduziert die Latenz und verbessert die Performanz. Normalerweise nutzen Hochfrequenzdesigns Routingstrukturen wie H-tree, Mesh oder Fish-bone bei CLK-Netzen. Neue Prozesstechnologien erreichen im Allgemeinen Taktfrequenzen von etwa 2 bis 3 GHz; damit verstärken immer steilere Taktflanken den Einfluss von Induktivitäten (Bild 4).

Jobangebote+ passend zum Thema

Diese verursachen Über- und Unterschwingen bei den Taktsignalen und verändern die Steilheiten und Formen der Signalflanken. Starke Puffer steigern die Flankensteilheiten, und damit das Überschwingen durch die Impedanzen. Diese Impedanzeffekte verschmieren die Haltezeit und können Fehlfunktionen im Chip bewirken.

Fazit

Der Umstieg von planaren auf nichtplanare Transistoren birgt viele Herausforderungen in Hinblick auf Genauigkeit und Performanz, die ein Parasitärextraktions-Werkzeug adressieren muss. Dabei sind nicht nur Probleme auf Bauteil-Ebene zu berücksichtigen, sondern auch die Verdrahtungsebenen genau zu behandeln. Außerdem ist die Genauigkeit der Parasitäreffekte in Zell-Bibliotheken und IP-Blöcken zu beachten, sodass die Implementierungs- und Verifikationszeit reduziert wird und das Tapeout im Zeitplan bleibt.

- Parasitärextraktion für fortgeschrittene FinFET-Technologien

- Herausforderungen für FinFET-Designs

- 3d- und 2,5d-Parasitärextraktions-Tools

- Ursachen der Performanzeinbußen

- Virtueller Metall-Fill

- Algorithmische Reduktion von Parasitärelementen

- Induktivitäts-Extraktion bei digitalen Clock-Netzen