Designtools / FinFET-Design

Parasitärextraktion für fortgeschrittene FinFET-Technologien

Fortsetzung des Artikels von Teil 4

Virtueller Metall-Fill

Praktisch jedes IC-Layout kennt Bereiche mit wenigen oder gar keinen Leiterbahnen. Diese müssen, zur Vermeidung elektrischer Performanz-Probleme im Design, mit Metall gefüllt werden. Dies wird als Dummy-Metal-Fill oder einfach nur Metal-Fill bezeichnet. Bei nicht-metallischer Füllebene heißt diese Dummy-Fill.

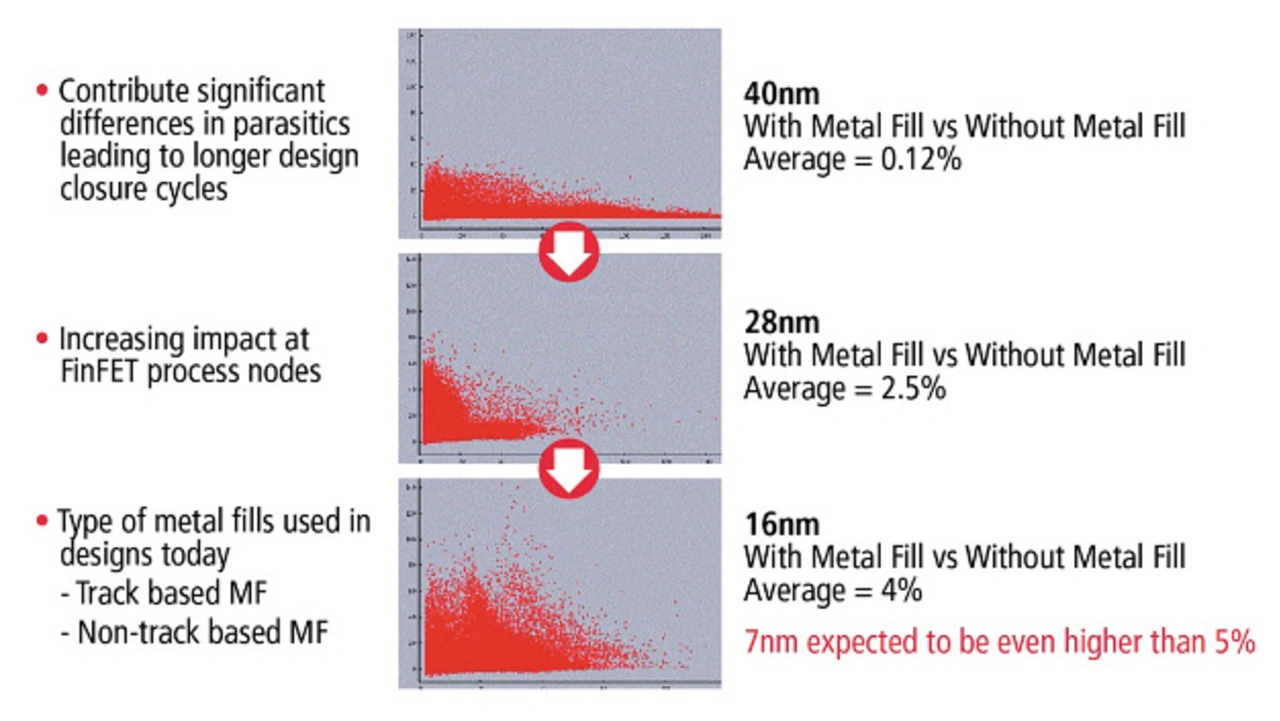

Oft wurde Metal-Fill erst sehr spät im Design-Zyklus hinzugefügt, nämlich erst nach dem abgeschlossenen Timing. Hierbei evtuell hinzugefügte Parasitärkapazitäten wurden daher einfach ignoriert. Diese Methodik ist für FinFET-Designs weder ausreichend noch empfohlen. Der Metal-Fill-Einfluss muss bereits während der Implementierung berücksichtigt und verstanden werden (Bild 3). Beim 40-nm-Prozessknoten betrug die in der Metallfüllung ursächliche Kapazitätsdifferenz etwa 1%. Das gestaltete sich in der Implementierung und im Signoff meist vernachlässigbar.

Jobangebote+ passend zum Thema

Bei 16-nm-FinFET-Designs ist dieser Einfluss auf mehr als 4% angewachsen. Bei 10 nm beziehungsweise 7 nm und weniger wird die Änderung vermutlich noch höher ausfallen. Deshalb wird dieser maßgebliche Einfluss auf die FinFET-Designs schon während der Implementierung berücksichtigt. Diese Methodik wirkt sich mit der zeitintensiven Signoff-Charakterisierung von Metal-Fill im GDS stark auf die Laufzeiten aus. Insbesonders, wenn mehrere Designänderungen (ECOs) in der Optimierungsphase durchgeführt werden müssen.

Zusammengefasst:

- Der Metal-Fill-Einfluss ist während der Implementierung und der Post-Routing-Optimierung zu berücksichtigen.

- Die Metal-Fill-Analyse muss in diesen Phasen schnell erfolgen, um unnötige ECOs zu vermeiden und die Durchlaufzeit bis zur Design-Closure zu reduzieren.

- Metal-Fill hat einen großen Einfluss auf längere Netze in FinFET-Designs.

Die Berücksichtigung der zusätzlichen Kapazität ist daher wesentlich: Sie könnte zu Lasten des Timings 20% oder mehr betragen.

- Parasitärextraktion für fortgeschrittene FinFET-Technologien

- Herausforderungen für FinFET-Designs

- 3d- und 2,5d-Parasitärextraktions-Tools

- Ursachen der Performanzeinbußen

- Virtueller Metall-Fill

- Algorithmische Reduktion von Parasitärelementen

- Induktivitäts-Extraktion bei digitalen Clock-Netzen