Designtools / FinFET-Design

Parasitärextraktion für fortgeschrittene FinFET-Technologien

Fortsetzung des Artikels von Teil 1

Herausforderungen für FinFET-Designs

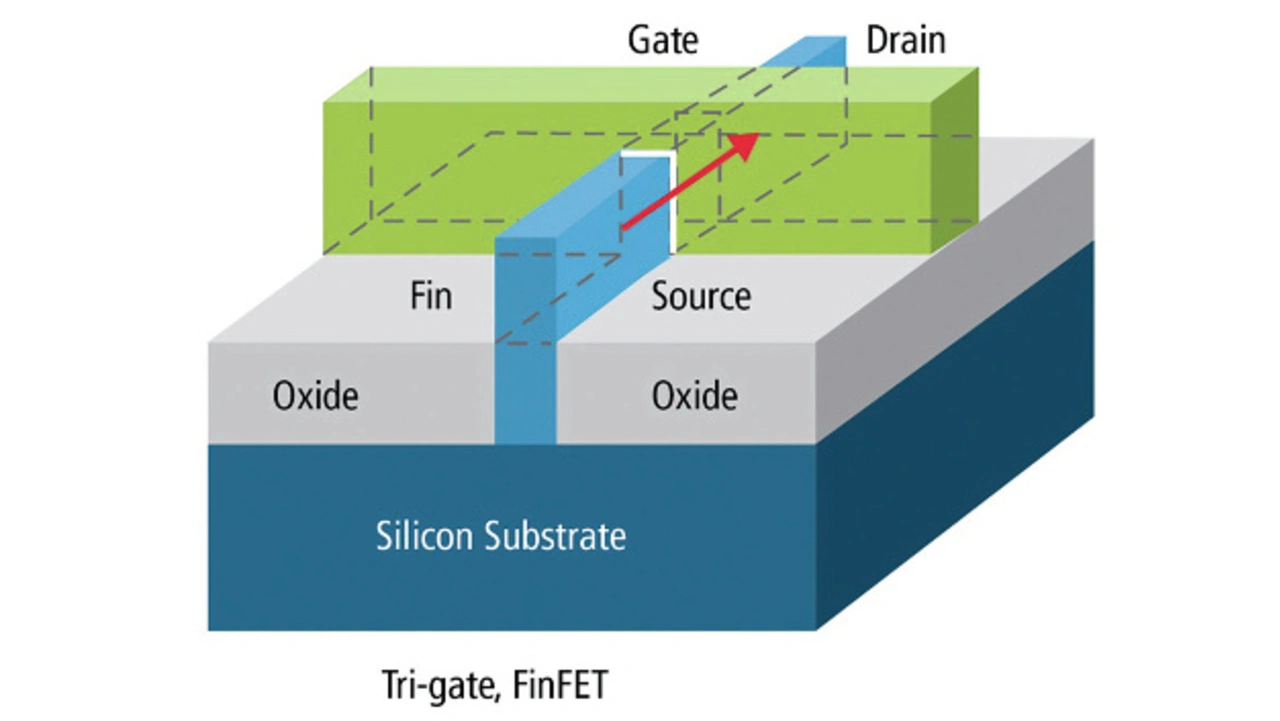

Mit FinFET-Technologien wird eine weitere Stufe der Designverbesserung integrierter Schaltungen in Bezug auf die Performanz und Leistungsaufnahme erreicht. Diese Vorteile bergen, besonders für die Parasitärextraktion, Herausforderungen, welche in zwei Kategorien eingeteilt werden:

- Erhöhung der Komplexität und

- aufwändigere Modellierung.

Nicht nur die dichteren Geometrien verursachen Probleme, sondern auch neue Design-Regeln, die mit jeder neuen Prozess-Technologie hinzukommen. Die Anzahl der Prozess Corners wächst rapide, ebenso wie die Parasitäreffekte, speziell durch Koppelkapazitäten und Widerstände (Bild 1). Solche Faktoren erhöhen die Designkomplexität und den Arbeitsaufwand. Mit der größeren Netzliste steigen die Extraktionslaufzeiten, und damit die Zeit für Post-Layout-Simulation und Charakterisierung von SoC-Designs (System-on-Chip). Dies gilt auch für die Laufzeiten der statischen Timing-Analyse bei Digital- und Custom-/Analog-Designs.

In der Modellierung sind Local-interconnect-Strukturen zu betrachten, außerdem sind Produktionseffekte zweiter und dritter Ordnung, hinreichend exakt zu berücksichtigen. Performanz und Turn-around-Zeiten sind zu entscheidenden Aspekten gewachsen. Ist die Genauigkeit dieser Schaltungen nicht zu gewährleisten, müssen zu Lasten der Performanz, zusätzliche Sicherheitsfaktoren eindesignt werden.

Die Anzahl der Prozess Corners stieg mit Einführung der MPT- (Multiple Patterning) und der DPT-Technologie (Double-Patterning) extrem. Die Technologien wurden bei 20 nm eingeführt und dann bei 16/14 nm und kleiner übernommen. Weiterhin nimmt die Anzahl der Transistoren stetig zu. Prozessknoten bei 20 nm und weniger kennen Designs mit mehr als 70 Millionen Netzen. Die höhere Corner-Anzahl und zunehmende Designgrößen steigern die Extraktionszeit typischerweise auf einen bis mehrere Tage.

Inzwischen sind für FinFET bis zu 155 mehr zu berücksichtigen als bei einem typischen Transistor im 28 nm Prozessknoten: Die größeren Netzlisten beeinflussen die Performanz der Postlayout-Analyse und erfordern kürzere Simulationslaufzeiten. Tools müssen drei verschiedene Widerstandstypen beim FinFET-Device unterscheiden: contact-, spread- sowie extension-Widerstände. Zusätzlich bewirkt die Dicke des 3D-Gates neue Kapazitäten. Von FinFET über Randkapazitäten bis zu Double Patterning und Weiterem wurden Modellierungsmöglichkeiten immer komplexer und erhöhten die Extraktionslaufzeit.

Weiterhin ist in der Modellierung die ausreichende Genauigkeit der Elektromigrations- und IR-Drop-Analyse (EM/IR) sicherzustellen. Mit der Einführung sehr komplexer Vias bei diesen Technologien wird eine präzise Extraktion notwendig: Andernfalls liefert die EM-Analyse eine Vielzahl falscher Ergebnisse, was die Auswertung erschwert und die Zeit bis zur Design-Closure verlängert.

Im Ergebnis: Extraktions- und Simulations-Laufzeiten bis hin zum Signoff nehmen stetig zu, die Zeitfenster für die Markteinführung des fertigen Produktes werden aber kürzer. Die Signoff-Schleife kann Prozesszeiten von sechs bis acht Wochen beanspruchen. Die Parasitärextraktion wird in diesem Flow kritisch. Die Extraktionslaufzeit skaliert mit Designgröße und -art, vollständige Extraktion moderner Prozessknoten kann selbst mit aktuellen Tools mehrere Tage dauern.

IC-Entwickler müssen diese neuen Problemen handhaben. Für manche Designs und Technologien sind vorhandene Flows und Tools noch akzeptabel, bei fortgeschrittenen Prozessknoten werden neue Lösungen notwendig. Unterschiedliche Extraktions-Engines in der Implementierung und im Signoff bewirken unter Umständen schlecht korrelierende Ergebnisse, zum Nachteil der Design-Closure. Die Verwendung konsistenter Extraktions-Engines an jeder Stelle im Flow - also in der Implementierung und im Signoff - ist entscheidend für eine Optimierung der Zeit bis zum finalen Signoff.

Jobangebote+ passend zum Thema

Den Anfang finden!

Foundries und Entwickler beginnen üblicherweise mit der Charakterisierung der Bibliotheken und IPs. Die Designs enthalten Standardzellenbibliotheken, SRAMs, Analog-Mixed-Signal- und Interface-IP. Von diesen, häufig in größeren SoCs wie Mixed-Signal-Designs eingesetzten Komponenten, ist höchste Genauigkeit gefordert. Wenn diese schon in der Basis verletzt ist, kann sich das auf den gesamten Chip auswirken.

Bei Prozesstechnologien um 20 nm und kleiner, besonders bei FinFET-Designs, entscheiden die genannten Herausforderungen mehr als je zuvor über eine genaue Vorhersage der Parasitärwerte. Sie müssen die Verhältnisse im realen Chip möglichst gut abbilden, um ein Aufaddieren der Fehler zu vermeiden.

- Parasitärextraktion für fortgeschrittene FinFET-Technologien

- Herausforderungen für FinFET-Designs

- 3d- und 2,5d-Parasitärextraktions-Tools

- Ursachen der Performanzeinbußen

- Virtueller Metall-Fill

- Algorithmische Reduktion von Parasitärelementen

- Induktivitäts-Extraktion bei digitalen Clock-Netzen