Designbeispiel

Entwicklungsschritte beim Aufbau eines IQ-Modulators

13. März 2014, 9:03 Uhr |

Von Dieter Rimmele

Diesen Artikel anhören

Fortsetzung des Artikels von Teil 3

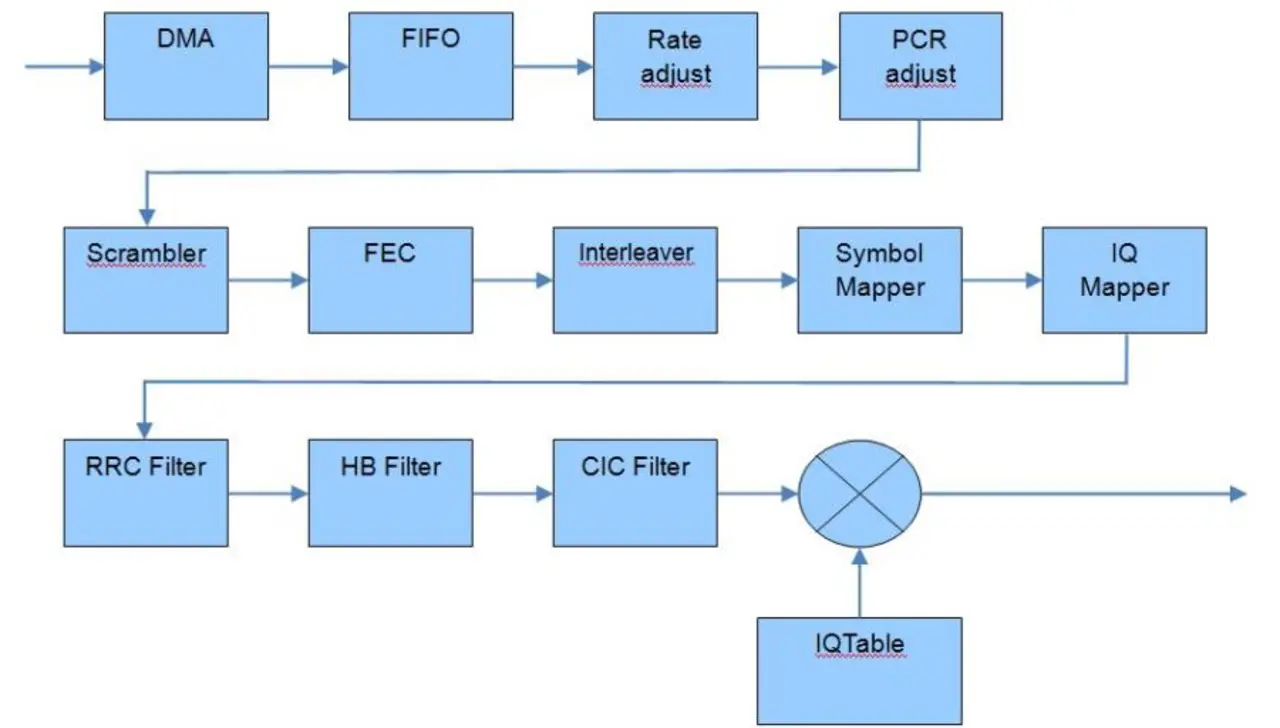

FPGA-Design, das den DVBC-Datenstrom generiert

Innerhalb des FPGAs wurden folgende Aufgaben gelöst:

1. PCI Express

- SerDes stellt die PCIE Verbindung her. Der Modulator wird über PCIE mit den Modulationsdaten versorgt.

- Entwicklung eines Linux und Windows Treibers

- DMA Controller

- Load Balancing, PCR Correction Buffer,

2. Digitale Signalaufbereitung

- Scrambler zur Energieverteilung / Vermeidung großer Spitzen..

- Forward Error Correction

- Interleaver zum Verteilen der Datenpakete auf mehrere Transportstreampakete, um Impulsfehler besser ausgleichen zu können.

- Symbol Mapper erlaubt QAM 16 bis QAM 256

- IQ Mapper zum Mapping der Symbolnummer auf I und auf Q

- SRRC Filter,

- HB-Filter, Half-Band-Filter für 2fach upscaling

- CIC-Filter

- Signaladdierer

3. Digital-Analog-Converter

- 32 LVDS Ports werden verwendet, um einen 2 x 16-Bit-DAC differentiell anzusteuern

- DC-Offset-Kompensation des DAC

- Interne Verarbeitung der DAC Daten mit 18 Bit - damit 6 db mehr Signalstärke

4. Schnittstellen zur Steuerung und Messung der analogen Kette

- I2C für den thermischen Sensor, "differential clock" und die RF-Power-Messung

- SPI für Mischer und VCOs

Jobangebote+ passend zum Thema

GLYN GmbH & Co. KG, Idstein

MACNICA ATD Europe GmbH, Ingolstadt

SPEA GmbH, Fernwald

- Entwicklungsschritte beim Aufbau eines IQ-Modulators

- Beschreibung des Analogteils der Modulatorkarte

- Weitere Hoch- und Tiefpassfilter erforderlich

- FPGA-Design, das den DVBC-Datenstrom generiert

- Entwicklung des Linux-Treibers