Designbeispiel

Entwicklungsschritte beim Aufbau eines IQ-Modulators

Fortsetzung des Artikels von Teil 1

Beschreibung des Analogteils der Modulatorkarte

Das digitale Summensignal aller zehn Transponder wird - siehe Bild 2 - auf zwei 16-Bit-Digital-nach-Analog-Wandler mit je 16 Bit geführt. Die Mittenfrequenzen der Transponder sind dabei zwischen 20 MHz und 92 MHz gewählt. Ein Teil der Modulation findet daher schon im FPGA statt.

Durch die Wahl der Trägerfrequenzen ab 20 MHz verliert man zwar etwas von der DAC-Bandbreite, hat jedoch den großen Vorteil, dass man keine Gleichstrom-Komponenten im Ausgangssignal hat und bei einer folgenden analogen IQ-Modulation den störenden Rest-Träger außerhalb eines Bandpassfilters platzieren kann.

Die Abtastfrequenz für den DAC beträgt 248,4 MHz wodurch eine theoretisch nutzbare Bandbreite von 124,2 MHz entsteht. Allerdings muss die Spiegelfrequenz (alles über 154 MHz) gut unterdrückt werden (also weniger als -40 dB), um später nicht als Störsignale weitere Transponder im Nutzband zu beeinflussen.

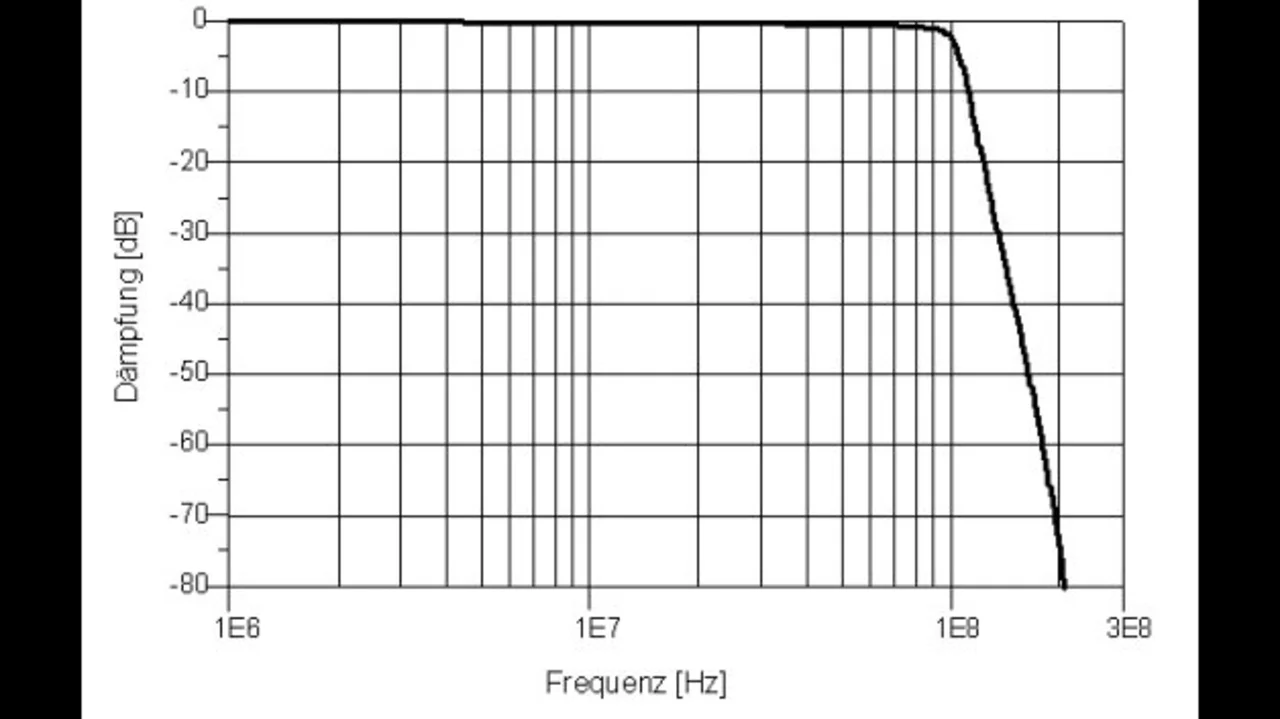

Aus diesem Grund wurde beschlossen nicht mehr als zehn Transponder gleichzeitig zu modellieren. Trotz dieser Beschränkungen muss der auf den DAC folgende Anti-Aliasing Tiefpassfilter exzellente Eigenschaften besitzen:

- Flacher Verlauf im Durchlassbereich mit minimaler Dämpfung bis zur Grenzfrequenz

- Große Dämpfung (> 40 dB) der Spiegelfrequenzen

- Best mögliche Unterdrückung der Abtastfrequenz und Ihrer Harmonischen.

- Geringe Toleranzen um im I und Q Pfad gleiche Gruppenlaufzeit zu erreichen.

Es wurde ein elliptischer Tiefpassfilter 7.Ordnung (Bild 3) entworfen, der diesen Anforderungen entspricht. Die Anforderungen an die Güte und Toleranz der Induktivitäten konnten dabei gut mit der Serie WE-KI der Fa. Würth Elektronik eiSos erreicht werden.

Durch die hohe Güte der Induktivitäten konnte eine Einfügungsdämpfung von max. 1 dB bei 95 MHz und so ein maximal flaches Ausgangssignal erreicht werden. Die Laufzeitunterschiede der beiden Kanäle bleiben < 0,2 % und die Spiegelfrequenzunterdrückung des IQ-Modulators bei ca. 45 dB. Ein nachfolgender Bandpassfilter säubert das Nutzband von 305 – 395 MHz. Es kann ein Signal-zu-Stör-Abstand von besser als 80 dB erreicht werden.

Diese Zwischenfrequenz kann nun gut weiter verarbeitet werden, indem sie auf eine weitere Zwischenfrequenz von 2200 bis 2300 MHz gemischt wird. Diese hohe ZF ist notwendig, um später das Nutzsignal in einen Bereich von 100 MHz – 860 MHz zu platzieren.

Jobangebote+ passend zum Thema

- Entwicklungsschritte beim Aufbau eines IQ-Modulators

- Beschreibung des Analogteils der Modulatorkarte

- Weitere Hoch- und Tiefpassfilter erforderlich

- FPGA-Design, das den DVBC-Datenstrom generiert

- Entwicklung des Linux-Treibers