Designbeispiel

Entwicklungsschritte beim Aufbau eines IQ-Modulators

Die fortschreitende Entwicklung bei FPGAs ermöglicht unter anderem die Entwicklung und Herstellung eines 80-MHz-IQ-Modulators für 100 MHz bis 868 MHz. Gezeigt wird dies im Folgenden am Beispiel eines DVB-C-Modulators von Digital Devices, der zum Beispiel für zehn 8-MHz-Transponder gemäß EN 300429 ausgelegt ist.

Für die Entwicklung eines IQ-Modulators (Bild 1) ist bei der Wahl des geeigneten FPGA-Bausteins die Anzahl der Multiplizierer entscheidender als die Anzahl der Logikzellen. Im vorliegenden Projekt fiel die Wahl deshalb auf einen ECP3 70 I8L mit 67K Look-up-Tables und 128 18x18-Multiplizierer. Die hohe Integrationsdichte des Modulators ermöglicht Abmessungen von 150 mm x 77 mm und kann damit auch in die meisten Low-Profile-PC-Gehäusen verbaut werden.

Um die Funktion auch bei höheren Umgebungstemperaturen zu ermöglichen, wurde in diesem Projekt die I8L-Variante gewählt, da diese 20 - 30 % weniger dynamischen Strom aufnimmt, was mit einer geringeren Eigenerwärmung einhergeht. Die Kühlung erfolgt passiv und benötigt nur einen geringen Luftstrom zur Kühlung. Alles in allem benötigt der Modulator weniger als 15 W.

Jobangebote+ passend zum Thema

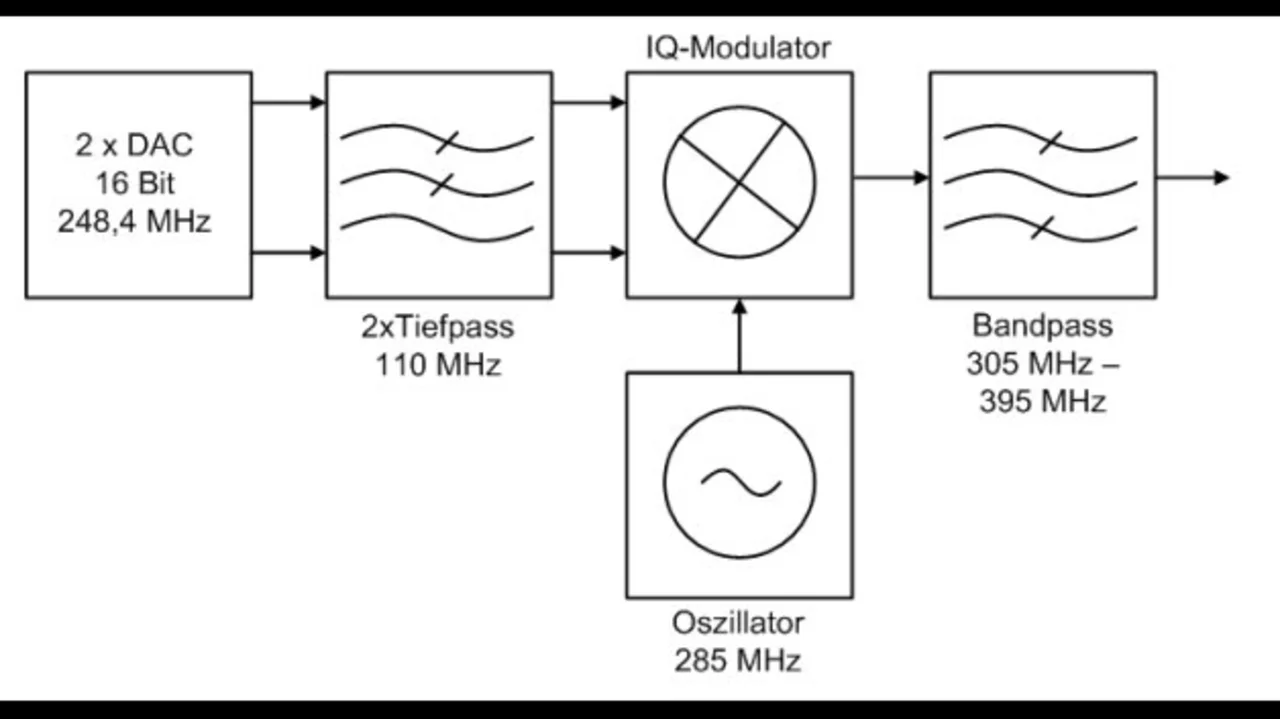

Der IQ-Modulator der Firma Digital Devices (Bild 2) besteht aus einem digitalen und einem analogen Teil. Im digitalen Teil wird jeder Transponder für sich erzeugt, auf die DAC-Frequenz von 248,4 MHz "upgesamplet", mit einer Trägerfrequenz von 20 MHz bis 92 MHz moduliert; nachfolgend werden alle zehn Transponder skaliert, zusammenaddiert und das Resultat wiederum mit einem 21-TAP-digitalen Equalizer sowie auf dem DAC ausgegeben. Dabei werden insgesamt pro Kanal zehn Stück 18-Bit-Multiplizierer benötigt. Der Equalizer ermöglicht einen Amplitudenausgleich im Frequenzgang des analogen Teils auf weniger als 1 dB.

Eine korrekte Auslegung der Analogkette ist nötig, um ein ideales Trade-off aus Signalstärke, SNR, Phase-Noise und Filtereigenschaften zu erreichen. Es wurde ein DAC mit 2 x 16 Bit Auflösung und 500 MSa gewählt, da dieser eine einfache Einstellung der Clock Phase erlaubt. 500 MSa erlauben außerdem ein Oversampling.

- Entwicklungsschritte beim Aufbau eines IQ-Modulators

- Beschreibung des Analogteils der Modulatorkarte

- Weitere Hoch- und Tiefpassfilter erforderlich

- FPGA-Design, das den DVBC-Datenstrom generiert

- Entwicklung des Linux-Treibers