NXP Semiconductors

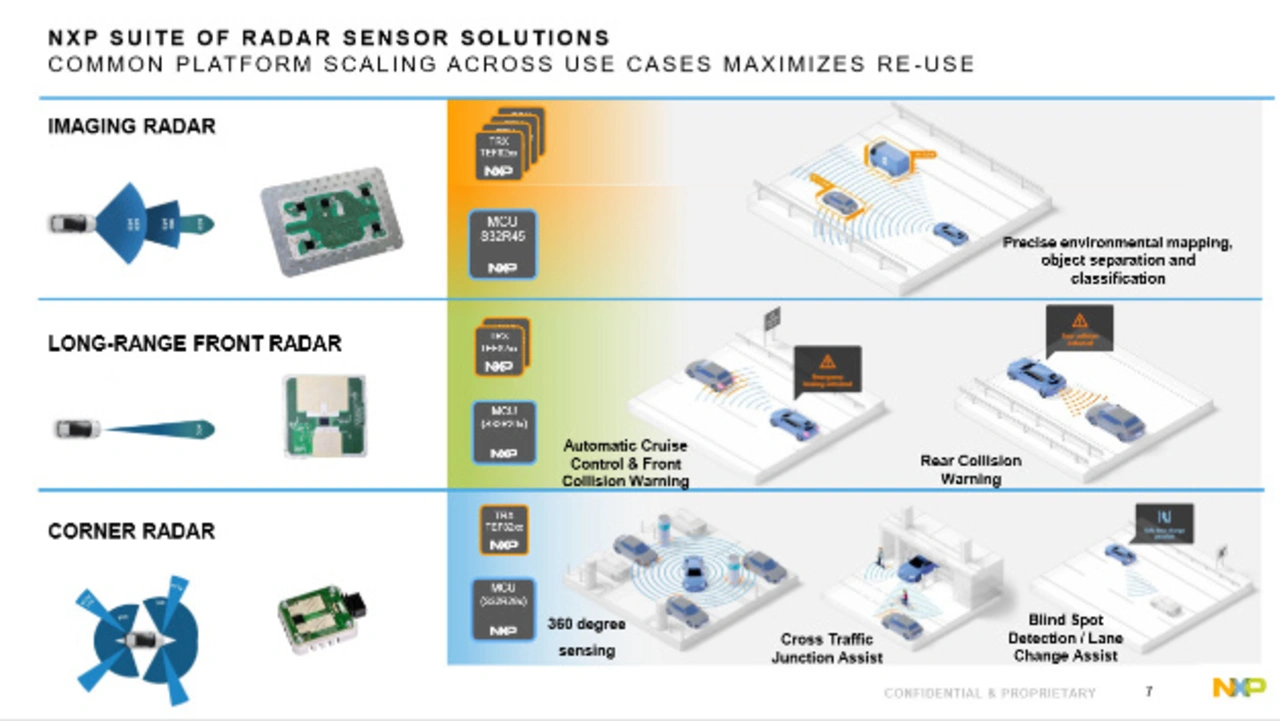

Vom Corner-Radar bis hin zu 4D-Imaging-Radar

Fortsetzung des Artikels von Teil 1

Neuer Transceiver, neue MCUs

Um diesem Anspruch gerecht zu werden, erweitert NXP sein Produktspektrum um einen neuen Transceiver und zwei neue Controller. Der neue TEF82xx-Transceiver ist laut Feulner der erste Automotive-Transceiver auf Basis eines 40-nm-RFCMOS-Prozesses. Dieser Prozess ermögliche eine höhere Leistung, eine größere Reichweite, eine bessere Auflösung von Objekten und bessere Skalierbarkeit für die unterschiedlichen Anwendungsfälle. Feulner: »Die zweite Generation von RFCMOS-Radar-Transceivern ist skalierbar, um den gesamten Anforderungsbereich abdecken zu können, vom einfachen NCAP-Sensor bis hin zum hochperformanten Imaging-Radar.« Die FMCW-Radar-Transceiver (Frequency-Modulated Continuous Wave - frequenzmoduliertes Dauerstrichradar) decken das vollständige Radarfrequenzband von 76 bis 81 GHz ab (verfügbare Bandbreite 4 GHz) und unterstützen Short-, Medium- und Long-Range-Radaranwendungen, einschließlich kaskadierter Imaging-Radar-Anwendungen. Die Transceiver verfügen über drei Sendekanäle, vier Empfangskanäle, einen A/D-Wandler, einen 6-Bit-Phasendreher, einer PLL und einem VCO (spannungsgesteuerter Oszillator) mit geringem Phasenrauschen. TEF82xx ist ISO26262-konform (ASIL B) und voll kompatibel mit den Radar-Mikrocontrollern S32R29x und S32R45x von NXP. Die HF-Performance ist mit 13,5 dBm (Pout) angegeben, die Rauschzahl mit 11,5 dB und das Phasenrauschen mit -95 dBc/Hz bei 1 MHz. Die Leistungsaufnahme liegt bei 1,5 W für zwei Sendekanäle und einem Tastverhältnis von 50 Prozent. Feulner: »Die Transceiver unterstützen einen MIMO-Betrieb und sind für eine schnelle Chirp-Modulation optimiert.«

Dazu kommen die neuen S32R-Radarprozessoren, laut Feulner auch in diesem Fall ein Novum in der Industrie. Denn dabei handelt es sich um die ersten Automotive-Radarprozessoren auf Basis eines 16-nm-FinFet-Prozesses. Feulner: »Die Prozessoren zeichnen sich im Markt durch das beste Verhältnis zwischen Rechenleistung pro Watt aus und ermöglichen neue Anwendungsfälle.« Wobei Feulner noch darauf hinweist, dass die hohe Rechenleistung nicht nur auf der Prozesstechnologie beruht, sondern auch auf proprietäre Beschleuniger, die NXP in die Chips integriert hat.

Beim neuen S32R294 liegt die Leistungsaufnahme im Vergleich zum S32R274 um die Hälfte niedriger, die Bausteine sind aber Code-kompatibel. Darüber hinaus erlauben die Automotive-Bausteine eine bessere Skalierbarkeit gegenüber den früheren Varianten. NXP hat die Controller mit zwei e200z7-32-Bit-Cores der Power-Architektur (bis zu 500 MHz) und zwei dedizierten Safety-Prozessoren (e200z4-Cores) in einer Lockstep-Konfiguration (bis zu 250 MHz) ausgestattet. Die Controller verfügen über bis zu 5,5 MB SRAM, ein MIPI CSI-2-Interface sowie das Security-Modul CSE3, das auch OTA-Anforderungen genügt. Darüber hinaus hat NXP die Controller mit den Beschleunigern STP (Signal Processing Toolbox) und CTE (Cross Timing Engine) für die Verarbeitung der Radarsignale ausgestattet. Die STP-Version der neuen Controller soll im Vergleich zur S32R274-Variante bei FFTs eine doppelt so hohe Performance (bei 430 MHz) aufweisen. Feulner: »Die neuen Controller sind für Corner-und Front-Radar-Anwendungen optimiert, bieten aber Leistungsreserven, der auch einen Multimode-Betrieb beispielsweise für Funktionen wie Cross Traffic Alert und Blindspotdetection. Mit ihnen lassen sich auch kaskadierte Anwendungen mit bis zu zwei Transceivern realisieren.«

»Der S32R45 ist unser Flaggschiff, er erreicht im Markt die höchstmögliche Leistung bei der Signalverarbeitung und ermöglicht damit das 4D-Imaging-Radar«, so Feulner. Der Prozessor basiert auf vier Cortex-A53-Cores (800 MHz) und drei Cortex-M7-Lockstep-Paare (400 MHz). An Beschleunigern sind die SPT-Variante 3.1 mit DSP-Erweiterung und Multi-Threading sowie der LAX (Linear Algebra Accelerator) integriert, der DoA-Algorithmen (DoA: Directorion of Arrival) im Vergleich zu einem Cortex-A53 um den Faktor 64 beschleunigt. Dazu kommen vier MIPI CSI2, 8 MB SRAM (mit ECC), eine HSE (Hardware Security Engine) und diverse Schnittstellen (PCIe, Ethernet und CAN). Feulner: »Die optimierten Prozessoren erlauben es, Kosten und Leistungsaufnahme im Vergleich zu einer FPGA-Implementierung um 50 Prozent zu senken.«

- Vom Corner-Radar bis hin zu 4D-Imaging-Radar

- Neuer Transceiver, neue MCUs

- K.o.-Schlag für Lidar?