Powermanagement-ICs

Mit Multi-Level-Wandlern schneller und effizienter laden

Fortsetzung des Artikels von Teil 1

Chipinterne sowie externe Verluste

Chipinterne Verluste

Tabelle 1 stellt die On-Chip-Verluste des 2-Level-Abwärtswandlers denen des 3-Level-Pendants gegenüber. Zu den On-Chip-Verlusten gehören die Durchlassverluste der FETs (PCOND), die Ladungsverluste beim Schalten (POSS und PGATE), die Rückwärtserholungsverluste (PQRR), die Verluste beim Ein- und Ausschalten des Gates (PIV) und die Verluste über die Body-Dioden während der Totzeit, in der beide Schalter ausgeschaltet sind (PDT). Unter der Annahme, dass CFLY bei VIN/2 symmetriert ist, müssen die FETs beim 3-Level-Wandler im Vergleich zu denen beim 2-Level-Wandler nur die halbe Spannung sperren.

|

Verluste |

2-Level-Wandler |

3-Level-Wandler |

P3L/P2L |

|---|---|---|---|

| PCOND |

IRMS2 · [D × RQ1 + (1 – D) · RQ2] |

IRMS2 · [D · (RQ1 + RQ3) + (1 – D) · (RQ2 + RQ4)] |

2 |

| PIV |

VIN · [IL(MAX) · toff(Q1-2) + IL(MIN) · ton(Q2-1)] / 2 · fSW |

VIN/ 2 · [IL(MAX) · (toff(Q1-2) + toff(Q3-4))+ IL(MIN) · (ton(Q2-1)+ ton(Q4-3))] / 2 · fSW |

1/2 |

| PDT |

VFWD · [IL(MAX) · tDT(Q1-2) + IL(MIN) · tDT(Q2-1)] · fSW |

VFWD · [IL(MAX) · (tDT(Q1-2) · tDT(Q3-4)) + IL(MIN) · (tDT(Q2-1) + tDT(Q4-3))] · fSW |

2 |

| POSS |

|

VIN/ 2 · fSW · (QOSS(Q1) + QOSS(Q3) + QOSS(Q2) + QOSS(Q4))/2 |

1/2 |

| PGATE |

VIN · fSW · (QG(Q1) + QG(Q2)) |

VIN · fSW · (QG(Q1) + QG(Q3) + QG(Q2) + QG(Q4)) |

1 |

| PQRR |

VIN · fSW · QQrr(Q2) |

VIN/ 2 · fSW v (QQrr(Q2) + QQrr(Q4)) |

Tabelle 1: Chipinterne Verluste beim 2-Level- und beim 3-Level-Abwärtswandler und Vergleich der Verlustanteile.

Tabelle 1: Chipinterne Verluste beim 2-Level- und beim 3-Level-Abwärtswandler und Vergleich der Verlustanteile.

Anhand dieser Annahmen zu den 2L- und 3L-Verlusten lassen sich die On-Chip-Verluste der beiden Topologien theoretisch vergleichen. Die folgenden Stichpunkte sind Highlights aus diesem theoretischen Vergleich:

- Die Schaltfrequenz fSW und die Welligkeit des Spulenstroms sind bei beiden Topologien identisch. Hieraus folgt, dass die Induktivität L3L nur ein Viertel von L2L beträgt (mehr hierzu im nächsten Abschnitt).

- Der High-Side-FET (HS) der 2-Level-Topologie verbraucht die gleiche Fläche wie beiden HS-FETs der 3-Level-Topologie. Die Nennspannung der 3-Level-FETs ist halb so groß wie die der 2-Level-FETs, sodass die Widerstände der FETs in der Summe jeweils gleich sind. Bei gleicher Fläche ist der gesamte On-Widerstand der FETs bei der 3-Level-Topologie also doppelt so hoch wie bei der 2-Level-Topologie.

- Wenn die 3-Level-FETs mit der halben Spannung der 2-Level-FETs beaufschlagt werden, aber die 3-Level-FETs mit denselben Spannungsspitzen dv/dt an VSW angesteuert werden, halbieren sich die Ein- und Ausschaltzeiten, sodass sich auch PIV halbiert.

- Wegen der gleich großen Flächen ist die insgesamt gespeicherte Ladungsmenge identisch. Tatsächlich ist die Ladungsmenge bei der 3-Level-Topologie sogar geringer, weil die Spannung an den FETs nur halb so hoch ist. Dies kann in einer einfachen Analyse jedoch vernachlässigt werden.

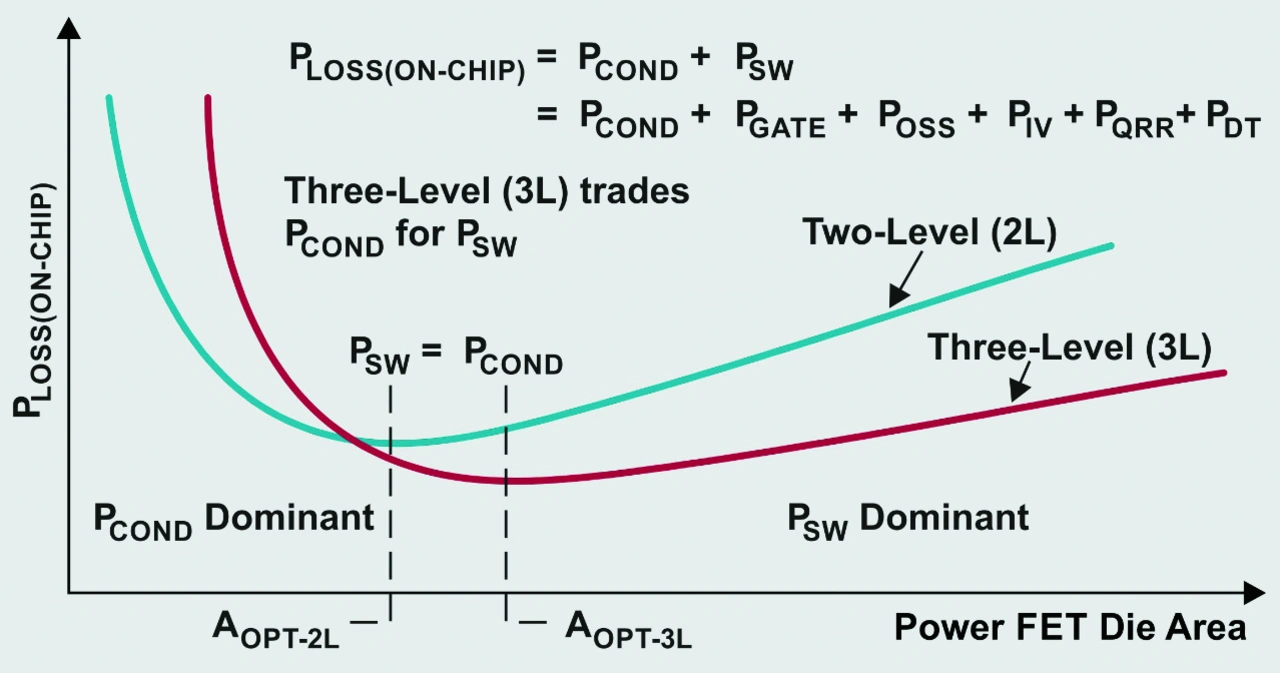

Wie in der Spalte ganz rechts in Tabelle 1 dargestellt, verdoppeln sich bei gleicher Chipfläche die Durchlass- und Totzeitverluste der 3-Level-Topologie. Da an den FETs in der 3-Level-Topologie jedoch nur die Hälfte der Eingangsspannung im Vergleich zur 2-Level-Topologie anliegt, halbieren sich die POSS- und PIV-Verluste. Durch eine größere FET-Fläche lassen sich die Durchlassverluste senken, bis die Schaltverluste zu dominieren beginnen (Bild 5). Die optimalen FET-Flächen (AOPT-2L, AOPT-3L) liegen dort, wo die Schaltverluste genauso groß sind wie die Durchlassverluste.

Externe Verluste

Die Off-Chip-Verluste resultieren aus den effektiven Serienwiderständen (ESR) des Eingangs- und des Ausgangskondensators, des fliegenden Kondensators und der Induktivität. Wählt man hier Keramikkondensatoren (MLCCs) mit sehr niedrigen ESR-Werten von unter 20 mΩ, so kann man diese Verluste nahezu vernachlässigen. Ebenso wie bei einem 2-Level-Wandler, werden auch die Ein- und Ausgangskondensatoren von 3-Level-Wandlern danach dimensioniert, welche Welligkeiten für den Eingangsstrom und die Ausgangsspannung hingenommen werden können.

Die Tatsache, dass CFLY mit Blick auf die akzeptablen Welligkeiten dimensioniert wird, ist entscheidend für die Funktion eines 3-Level-Wandlers. Damit CFLY bei Lastsprüngen, beim Anlaufen, bei geringer Last und bei einem Tastverhältnis D von 100 % stets auf VIN/2 bleibt, sind tatsächlich einige zusätzliche, proprietäre Schaltungen erforderlich, die in Bild 2 nicht dargestellt sind. Die Brummspannung von CFLY erreicht bei einem Tastverhältnis von 50 % ihr Maximum und nimmt direkt mit dem Laststrom zu. Der Wert von CFLY ist so zu wählen, dass ∆VC(FLY) weniger als 10 % von VIN/2 beträgt. Dadurch bleibt die Regelschleife stabil. Um eine lange Lebensdauer des Kondensators zu gewährleisten, sind seine Gehäuseabmessungen und seine RMS-Stromfestigkeit ausreichend groß zu wählen, um mit dem Temperaturanstieg zurechtzukommen.

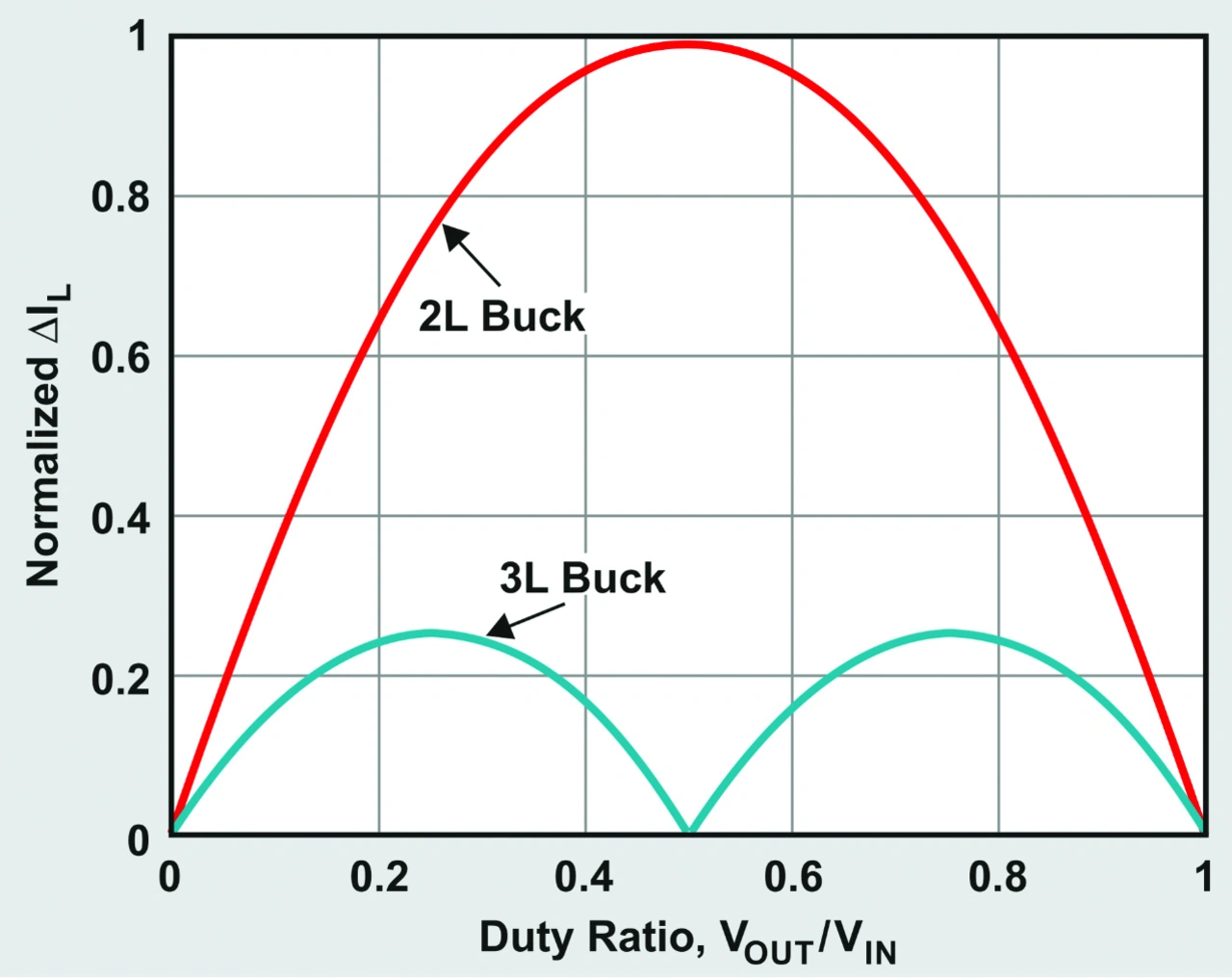

Die Verluste in der Induktivität setzen sich aus Kupferverlusten PDCR und den Kernverlusten PCORE zusammen. PDCR steigt mit dem Induktivitätswert, der wiederum von fSW bestimmt wird. Infolge der um 180° phasenversetzten Ansteuerung von Q3 und Q4 verdoppelt sich effektiv die Schaltfrequenz des Wandlers am Schaltknoten VSW. Da CFLY außerdem auf VIN/2 gehalten wird, halbiert sich beim 3-Level-Wandler ferner der magnetische Fluss in der Induktivität. Zusammen führt dies dazu, dass sich die Welligkeit des Spulenstroms auf ein Viertel verringert (bei unveränderter Induktivität und gleicher Schaltfrequenz fSW). Dies ist in Bild 6 klar zu sehen.

Für einen 3-Level-Wandler lässt sich der Wert der Induktivität folgendermaßen berechnen:

Die Gleichstromverluste lassen sich folgendermaßen bestimmen:

Diese letzte Gleichung bestätigt, dass sich die Welligkeit des Spulenstroms nur wenig auf die Kupferverluste PDCR auswirkt. Genauso wie schon beim 2-Level-Wandler verlangt auch der 3-Level-Wandler nach einer Induktivität mit niedrigerem Gleichstromwiderstand, um einen höheren Wirkungsgrad zu erreichen. Wie bereits erläutert, verringert die 3-Level-Topologie prinzipbedingt die Welligkeit des Spulenstroms auf ein Viertel. Kann die Applikation mit der gleichen Welligkeit des Spulenstroms und der daraus resultierende Welligkeit der Ausgangsspannung einer vergleichbaren 2-Level-Wandlers bei gleicher Schaltfrequenz leben, dann kann eine Spule mit einem Viertel der Induktivität eingesetzt werden, was deutlich geringere Abmessungen ergibt.

Geht man davon aus, dass der DCR-Wert einer Spule proportional zu ihrem Induktivitätswert ist, so betragen die Verluste in der Spule des 3-Level-Wandlers nur ein Viertel von jenen des 2-Level-Wandlers. Das kleinere Gehäuse sorgt hier für geringere Abmessungen der Gesamtlösung, und der niedrigere DCR-Wert ergibt einen höheren Wirkungsgrad. Bei gleichem thermischem Budget kann der 3-Level-Wandler somit trotz kleinerer Fläche einen höheren Ausgangsstrom liefern als eine 2-Level-Lösung, die Leistungsdichte ist also höher.

- Mit Multi-Level-Wandlern schneller und effizienter laden

- Chipinterne sowie externe Verluste

- Vergleich der Ladelösungen