Die nächste NAND-Flash-Generation

Trench-Cell- statt Gate-All-Around-Architektur

Fortsetzung des Artikels von Teil 1

Einführung der 3D-Trench-Cell-Architektur 2030

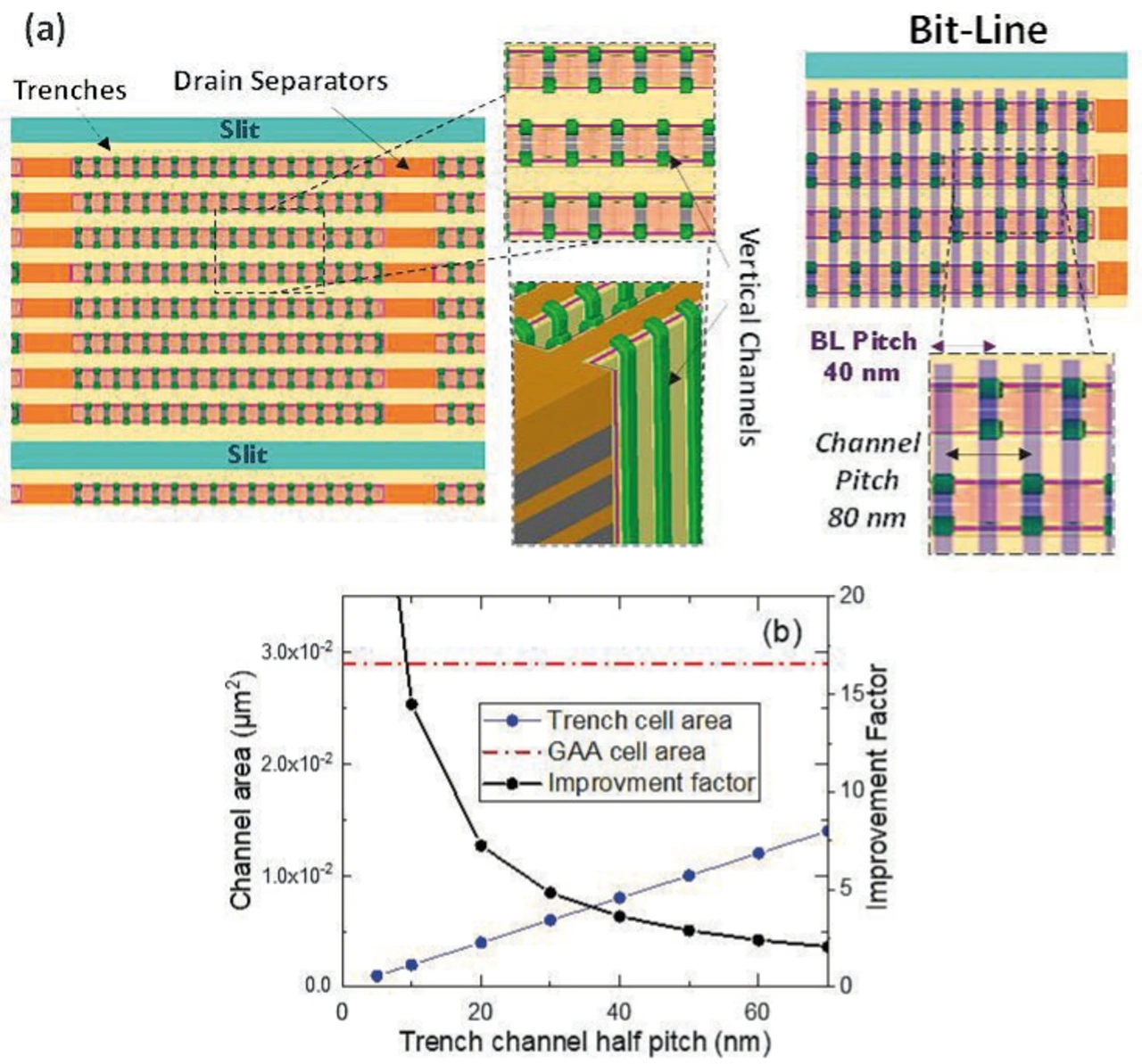

Im Jahr 2030, nachdem die Skalierung von GAA-NAND-Flash an ihr Ende gekommen sein wird, sieht imec die Einführung einer neuen Architektur zur Verbindung der Ladungsfallen-Zellen vor: die Trench-Cell-Architektur. Mit dieser Architektur verabschiedet sich der 3D-NAND von der runden GAA-Speicherzellengeometrie. Stattdessen werden die Zellen an der Seitenwand eines Grabens implementiert – ähnlich einer planaren Konfiguration, die auf die Seite gekippt wird – mit zwei Transistoren an gegenüberliegenden Wänden des Grabens.

Diese NAND-Flash-Zellenarchitektur der nächsten Generation führt nicht nur zu dem erforderlichen Sprung der Bit-Speicherdichte, sondern auch zu reduzierten Fertigungskosten. Wie bei der 2D-Planar-Konfiguration ist das Gate jedoch nicht mehr vollständig um den Kanal gewickelt. Daher befürchten die Speicherhersteller ein unzureichendes Programm-/Löschfenster.

Programmier- und Löschverhalten von Trench- und GAA-Zellarchitekturen

Auf dem IEEE International Memory Workshop 2023 (2023 IMW) präsentierte imec einen experimentellen Vergleich des Speicherbetriebs einer Trench-Zelle mit dem einer GAA-Speicherzelle. Beide NAND-Flash-Varianten wurden auf demselben Wafer prozessiert, nämlich einem selbst entwickelten 3D-NAND-Testträger mit Poly-Si-Gate und drei Wortleitungsschichten. Anstelle von zylindrischen Löchern wurden für die Trench-Struktur Trench-Features (300 nm breit und 1 µm lang) in den Word-Plane-Stack geätzt. Drei vertikale, flache Poly-Si-Kanäle (mit 50–200 nm Kanalbreite) wurden entlang der Seitenwände des Grabens formiert, und Source/Drain-Übergänge werden hergestellt.

Ohne Optimierung schneiden die Trench-Zellen nicht so gut ab wie die GAA-Zellen. Sie haben eine nicht ideale Programmier- und Löscheffizienz, was sich in den Steigungen und dem Beginn der inkrementellen Schrittpuls-Programmier- (ISPP) bzw. Löschkurven (ISPE) widerspiegelt. Daraus ergibt sich ein kleineres Programm-/Löschfenster. Auf der Löschseite zeigen die ISPE-Kurven ebenfalls eine Verschlechterung des Sättigungsniveaus beim Löschen.

Jobangebote+ passend zum Thema

Auf dem Weg zu einem 5-V-Speicherfenster

Das schlechte Speicherfenster lässt sich dadurch erklären, dass der krümmungsinduzierte Feldeffekt fehlt, der bei den GAAs die Ladungsträgerinjektion in die Sperrschicht erhöht. Um dieses Manko zu beheben, hat das imec-Team einen innovativen Weg gefunden: die Verringerung der Kanalbreite des Trench-Bauelements. Dadurch müssten sich die gekrümmten Bereiche mit hoher Injektion, die sich an den Rändern des Kanals bilden, stärker auswirken. Mit anderen Worten: Bei einer stark reduzierten Kanalbreite beginnt die Trench-Zelle aus geometrischer Sicht einer GAA-Zelle zu ähneln.

Andererseits wird die Verschlechterung des Sättigungsniveaus beim Löschen hauptsächlich durch die parasitäre Elektroneninjektion vom Gate aus bestimmt. Dies kann durch eine sorgfältige Konstruktion des Gate-Stapels und die Integration eines Metall-Gates unterdrückt werden.

imec hat experimentell gezeigt, dass die Kombination von Trench-Bauelementen mit skalierter Kanalbreite (bis zu 30 nm) und den folgenden Maßnahmen den Speicherbetrieb deutlich verbessert:

- Einsatz von alternativen High-k-Liner-Material (wie ZrO2 oder HfO2 anstelle von Al2O3)

- konstruiertes Tunneloxid

- Integration eines Metall-Gates

Für die meisten der untersuchten Bedingungen konnte ein Speicherfenster von bis zu 5 V nachgewiesen werden, was eine deutliche Verbesserung gegenüber 2 V darstellt – und das ohne Beeinträchtigung der Speicherung und des Zyklusverhaltens. Derzeit arbeitet das Team an einer weiteren Verbesserung des Programm- und Löschvorgangs.

Ultrahohe Bit-Speicherdichte

Nach der Demonstration einer Trench-Speicherzelle mit guten Speichereigenschaften besteht der nächste Schritt in der Untersuchung potenzieller industrietauglicher Integrationsverfahren, um eine größere Anzahl von Schichten zu stapeln. Es wird erwartet, dass ein solcher Prozessablauf dem GAA-Prozessablauf ähnelt, wobei ein zusätzliches Modul hinzukommt: das Ätzen der vertikalen, flachen Kanalstreifen an der Seite des Grabens. Unter der Voraussetzung, dass eine Prozesslösung für diesen anspruchsvollen Ätzschritt gefunden werden kann, schlug imec eine Emulation eines 3D-Graben-Prozesses mit Gräben im Abstand von 220 nm vor, wobei jeder Graben 100 nm breit und etwa 1 µm lang ist. Um eine hohe Bitdichte zu gewährleisten, wird der Fluss durch das Ätzen von 25 nm breiten Kanalstreifen mit einem Abstand von 80 nm vervollständigt.

Fazit: Auf der Grundlage dieser Ergebnisse kann die 3D-Trench-Cell-Architektur als potenzieller Durchbruch für künftige 3D-NAND-Flash-Speicher mit Bit-Speicherdichten von weit über 100 Gbit/mm2 angesehen werden.

- Trench-Cell- statt Gate-All-Around-Architektur

- Einführung der 3D-Trench-Cell-Architektur 2030