imec

Neue SOT-MRAM-Architektur beseitigt bisherige Probleme

Das imec hat auf der letzten IEDM 2022 eine neue SOT-MRAM-Architektur gezeigt, mit der das Forschungsinstitut die bisherigen Probleme von SOT-MRAMs beseitigt.

SOT-MRAM ist ein nichtflüchtiger Speicher mit vielversprechenden Eigenschaften für Embedded-Memory-Anwendungen, z.B. als L3-Cache (und darüber) in HPC- (High Performance Computing) oder mobilen Anwendungen. Heute werden diese Art der Aufgaben typischerweise von ultraschnellem SRAM übernommen. Allerdings stößt die Skalierung der SRAM-Speicherzellen an ihre Grenzen, denn mit kleineren Strukturgrößen steigt die Verlustleistung - ein Problem, wenn es um eine geringe Stromaufnahme im Standby-Modus geht – und es treten zunehmend Zuverlässigkeitsprobleme auf. Nichtflüchtige Speicher wie MRAM haben nicht nur das Potenzial, dass damit kleinere Bitzellen realisiert werden können, dank der Tatsache, dass es sich dabei auch noch um einen nichtflüchtigen Speicher handelt, wäre damit auch das Problem der Leistungsaufnahme im Standby-Modus gelöst.

Jobangebote+ passend zum Thema

Die SOT-MRAM-Technologie ist aus der reiferen Spin-Transfer-Torque-MRAM-Technologie (STT-MRAM) heraus entstanden. SOT-MRAM eignet sich im Vergleich zu STT-MRAM aufgrund seines besseren Abschneidens beim Datenerhalt und aufgrund des schnelleren Umschaltens zwischen zwei binären Zuständen besser für Cache-Anwendungen.

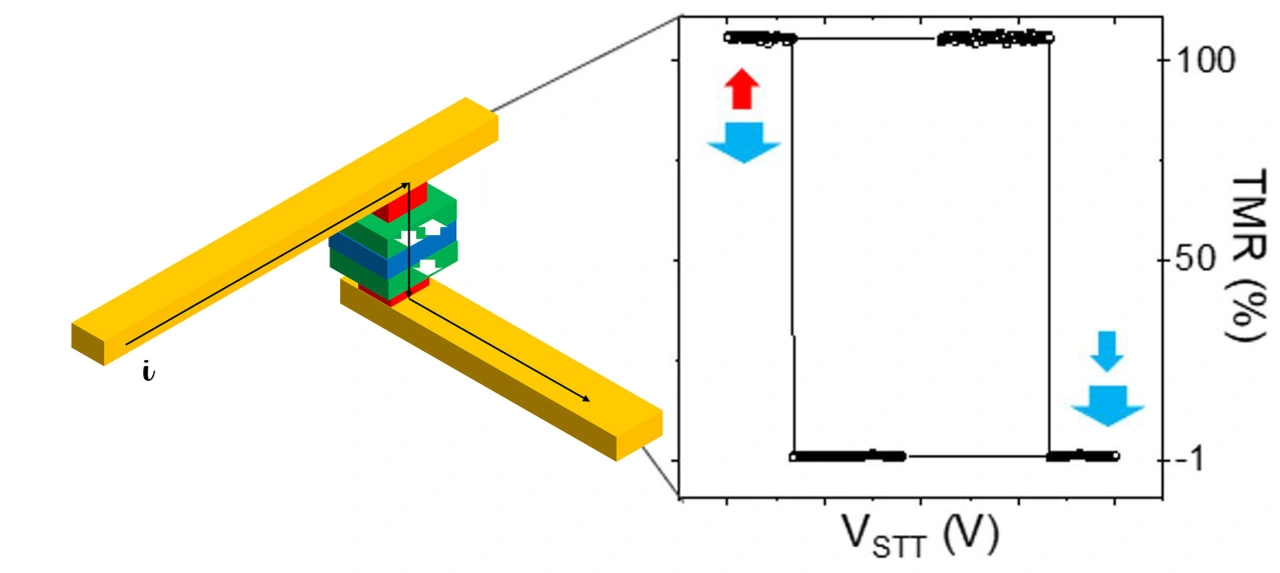

Herzstück bei beiden MRAM-Varianten ist ein magnetischer Tunnelübergang (MTJ). In diesem MTJ ist eine dünne dielektrische Schicht (MgO) zwischen einer ferromagnetischen Schicht (CoFeB) mit festgesetzten Magnetisierungsrichtung und einer ferromagnetischen Schicht (CoFeB), bei der die Orientierung geändert werden kann, eingebettet. Das Beschreiben der Speicherzelle erfolgt durch Umschalten der Magnetisierung der freien Schicht - der 'Speicherschicht' der MRAM-Bitzelle. Zum Lesen wird der »Magnetowiderstand« des MTJ gemessen, indem ein Strom durch den Übergang geleitet wird. Dieser Tunnel-Magnetwiderstand (TMR) kann hoch oder niedrig sein, je nach der relativen Orientierung der Magnetisierung in der freien und der festen Schicht (d.h. parallel (1) oder nicht-parallel (0)).

Unterschied zwischen SOT- und STT-MRAM

Der Hauptunterschied zwischen STT- und SOT-MRAM liegt darin, wie der Strom für das Schreiben injiziert wird. Während beim STT-MRAM der Strom senkrecht in die MTJ injiziert wird, erfolgt die Strominjektion bei SOT-MRAM in der Ebene, in einer angrenzenden SOT-Schicht - typischerweise ein Schwermetall wie Wolfram (W). Daher sind bei SOT-MRAM die Lese- und Schreibpfade entkoppelt, was die Beständigkeit und Lesestabilität der Speicherzellen erheblich verbessert. Wird der Strom in der Ebene injiziert, fallen auch die Schaltverzögerungen, die für den Betrieb von STT-MRAM charakteristisch sind, weg. Das imec hat bereits 2018 demonstriert, dass SOT-MRAM zuverlässig bis hinunter zu 210 ps schalten kann und das mit einer sehr guten Langlebigkeit (>5 x 10hoch10 Schaltzyklen) und einer Energieaufnahme von 300 pJ während des Betriebs.

- Neue SOT-MRAM-Architektur beseitigt bisherige Probleme

- SOT-MRAM hat aber seine eigenen Probleme

- Auf dem Weg zur industriellen Umsetzung