Generative künstliche Intelligenz

Den Strombedarf mit Leistungsmodulen reduzieren

Der Stromverbrauch im Bereich generative künstliche Intelligenz steigt kontinuierlich an. Warum verbraucht die Modellierung des menschlichen Gehirns so viel Strom und wie lässt sich dagegen ansteuern? Die Lösung ist eine vertikale Platzierung des Point-of-Load(PoL)-Wandlers auf dem Prozessorchip.

Das Gehirn eines Erwachsenen verbraucht etwa 0,3 kWh Energie pro Tag. Das typische moderne »Gehirn« eines künstlichen neuronalen Netzwerks konsumiert jedoch weitaus mehr. Für das Training großer generativer Sprach-KI-Modelle sind enorme Strommengen nötig. So hat das Training des GPT-3-Modells von OpenAI mit 175 Mrd. Parametern etwa 1,3 GWh an Energie erfordert. Bei einem Preis von 40 US-Dollar pro MWh – die ungefähren Kosten für Onshore-Windenergie – entspricht das allein 52.000 US-Dollar an Stromkosten. Es wird erwartet, dass die nächsten Generationen großer Sprachmodelle (Large Language Models, LLMs) bis zu einer Billion Parameter umfassen werden. Da die Anzahl der Parameter ein guter Indikator für die Trainingszeit und die Rechenzyklen ist, lässt sich leicht erkennen, wie sich die Energiekosten – und die Umweltauswirkungen – für das Training von künftigen GenAI-Modellen entwickeln werden.

Jobangebote+ passend zum Thema

Gründe für den immensen Stromhunger

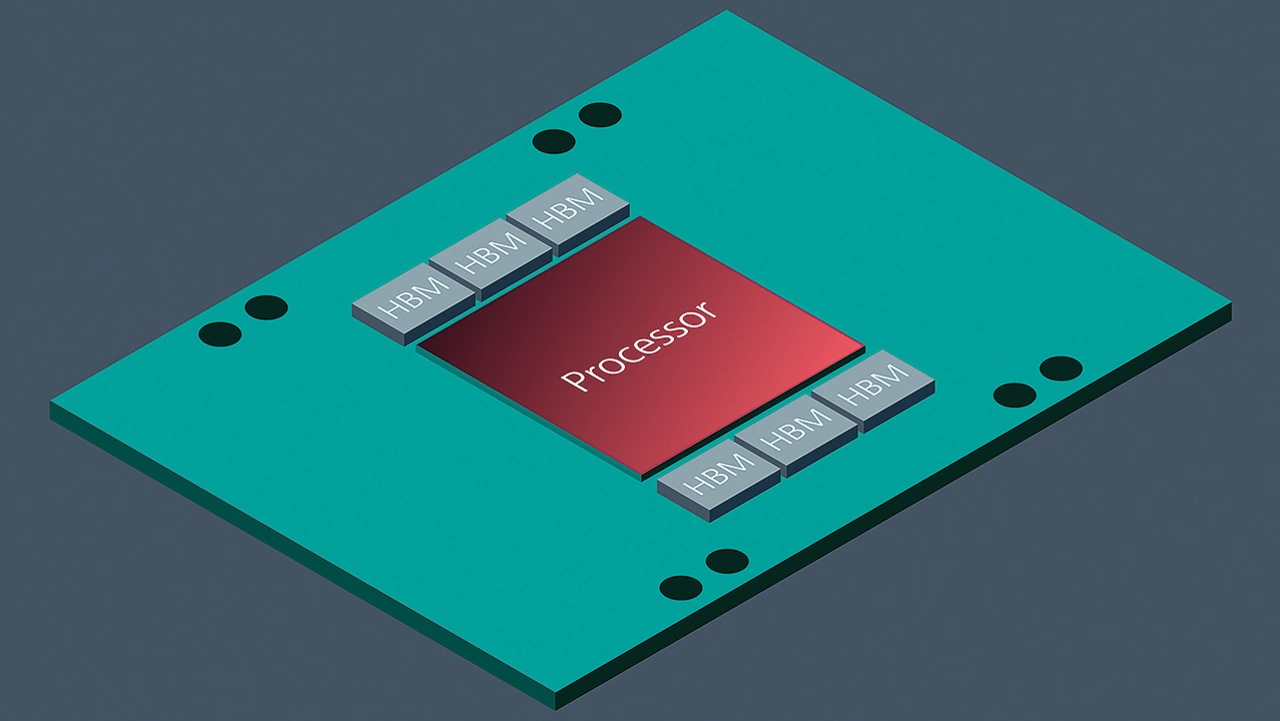

GenAI-Modelle werden auf Supercomputern mit Tausenden von Beschleunigungsmodulen (Accelerator Modules, AMs) trainiert. Diese basieren auf Chiplet-basierten Prozessoren, die aus einem massiv parallelen Mathematikprozessor und Hochgeschwindigkeitsspeichern (High Bandwidth Memories, HBMs) bestehen.

Die neueste Generation dieser Prozessoren hat eine kontinuierliche TDP (Thermal Design Power) von bis zu 1200 W (Bild 1). Der kurzfristige Spitzenleistungsaufnahme dieser Trainingsprozessoren kann bis zu 2000 W oder mehr betragen.

In diesen Chiplet-Arrays gibt es drei Strombereiche: Core, Speicher und Hilfsstromkreis. Die Core-Spannung bei der 4-nm-CMOS-Fertigungstechnologie, die zur Herstellung dieser 100B-Transistorchips verwendet wird, beträgt in etwa 0,65 V. Der kontinuierliche Strombedarf liegt leicht über 1000 A. Wie lässt sich dieser enorme Stromverbrauch und die dabei erzeugte Wärmemenge, bewältigen?

Ursachen für die Verlustleistung

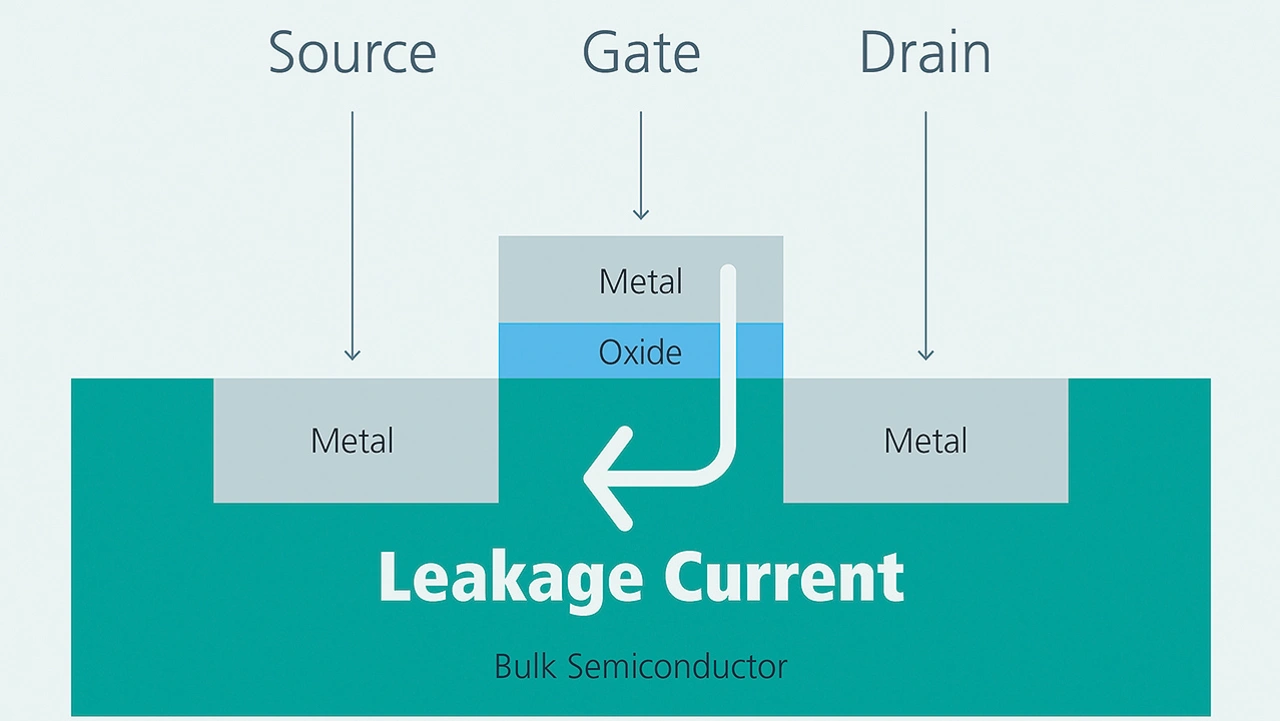

CMOS-Transistoren weisen zwei Verlustleistungsquellen auf: nicht schaltende, statische (PS) sowie schaltende, dynamische (PD) Verluste. Da sich die Transistorgröße mit aufeinanderfolgenden Generationen der Fotolithografie immer weiter verkleinert, wird der Oxid-Isolator des Transistor-Gate dünner und »unterschwelliger«. Hinzu kommen andere Arten von Leckströmen von Source zu Drain über das Gate-Oxid, multipliziert mit der Transistor-Schwellenspannung, was zum Hauptfaktor für die gesamte (PS + PD) Verlustleistung führt (Bild 2).

Statische Leckströme machen bei 4-nm-CMOS-Prozessoren mehr als 50 % des gesamten Prozessorstromverbrauchs aus. Dieser Trend wird sich mit kommenden Prozessortechnologien noch beschleunigen, was eine enorme technische Herausforderung für die Halbleiterindustrie darstellt. An sich sind diese riesigen Trainingsprozessoren – mit Abmessungen von circa 50 mm x 60 mm – kleine Heizungen, die eine Flüssigkeitskühlung benötigen, um einer Selbstzerstörung zu entgehen.

Reduzierung des Leistungsbedarfs

Seit Jahrzehnten werden Stromversorgungen für Computerprozessoren entwickelt, ohne dabei den dynamischen Leistungsbedarf besonders zu berücksichtigen. Bis vor Kurzem wurden Prozessoren mit Luftkühlung betrieben, die auf Wärmeleitung und Konvektion beruhten. Es wurden leistungsstärkere (und geräuschärmere) Lüfter entwickelt, und die TDP-Werte selbst der fortschrittlichsten CPUs lagen bei 200 W oder weniger. Der dynamische Strombedarf (aufgrund der algorithmischen Belastung) von CPUs und GPUs war vor 2020 begrenzt. Doch dieser Zustand änderte sich bereits um 2016 mit der Einführung von GPUs für KI-Modelltraining und maschinelle Lernanwendungen (Machine Learning, ML) mit TDPs von 300 bis 450 W.

Mit TDPs auf diesem Niveau und der Tatsache, dass Tausende von GPUs erforderlich sind, um neue große Sprach- und Deep-Learning-Modelle künstlicher neuronaler Netze zu trainieren, stieg das Bewusstsein für die Effizienz der Stromversorgung, für die Verluste auf der Leiterplatte (PCB) sowie für unerwünschte Versorgungsspannungsgradienten über große Chip-Flächen hinweg rapide an. Seit etwa 2016 haben sich die CMOS-Fertigungstechnologien zudem von 16-nm-Knoten zu 4-nm-Knoten weiterentwickelt, wobei die Versorgungsspannung der Core-Logik von etwa 0,8 VDD auf etwa 0,65 VDD gesunken ist. Dies stellt höhere Anforderungen an die präzise Stromregelung. Zu bedenken ist, dass Beschleunigungsmodule (AMs) für GenAI-Trainingsprozessoren jeweils etwa 30.000 US-Dollar kosten. Niemand möchte an AM-Ausfälle denken, die durch schlechte Stromversorgungskomponenten verursacht werden, da die fortschrittlichen Trainingsprozessoren für GenAI-Modelle nach wie vor sehr teuer sind.

Optimiertes Power Delivery Network

Ab 2017 wurden in den ersten Stromversorgungsmodulen der Hochstrom-GenAI-Prozessoren die Point-of-Load-Wandler (PoL) seitlich (neben) dem Prozessor platziert. Das Stromversorgungsnetz (Power Delivery Network, PDN) eines derart platzierten PoL-Wandlers hat eine hohe elektrische Impedanz, die aufgrund des spezifischen Widerstands von Kupfer und der Länge der Leiterbahnen auf der Leiterplatte bei 200 μΩ oder höher liegt. Da die Anforderungen an den Dauerstrom für GenAI-Trainingsprozessoren auf 1000 A steigen, führt dies zu einer Verlustleistung von 200 W in der Leiterplatte. Multipliziert man diesen Verlust mit den Tausenden von AMs, die in GenAI-Supercomputern für das LLM-Training erforderlich sind, wird dieser Verlust sehr erheblich – vor allem wenn man bedenkt, dass die AMs fast nie ausgeschaltet werden. GenAI-Beschleunigungsmodule in GenAI-Rechenzentren sind rund um die Uhr (24/7) für zehn Jahre oder länger in Betrieb.

In Anbetracht dieser Energieverschwendung haben Entwickler von KI-Rechnern damit begonnen, die PoL-Wandler direkt unter dem Prozessorpaket in einer vertikalen Stromversorgungsstruktur (Vertical Power Delivery, VPD) zu platzieren. In einem VPD-PDN kann die Impedanz 10 μΩ oder weniger betragen, was 10 W bei 1000 A Dauerstrom für den Core-Spannungsbereich bedeutet. Dies reduziert die Verlustleistung auf der Leiterplatte um 200 W – 10 W = 190 W (WPCB), wenn die PoL-Wandler nicht mehr seitlich, sondern vertikal platziert werden.

Bei der geschätzten Nachfrage für AMs in den kommenden Jahren – im Jahr 2024 waren es bereits mehr als 2,5 Mio. Einheiten – und vorsichtigen Kostenschätzungen für den Strompreis (40 US-Dollar pro MWh) führen diese 190 W Einsparung pro AM bis 2027 zu weltweiten Stromeinsparungen im TWh-Bereich, was Milliarden von Dollar an Betriebskosten und Millionen Tonnen an CO2-Emissionen einspart – und das auf unbegrenzte Zeit.

Factorized Power Architecture

Die Ära der generativen künstlichen Intelligenz steht uns bevor. Mit dieser Revolution in der Informationstechnologie erlebt die Elektronikindustrie eine rasante Entwicklung bei den Stromversorgungsarchitekturen für Prozessoren, die das Training generativer KI-Modelle übernehmen. Die Factorized-Point-of-Load-Wandler von Vicor (Factorized Power Architecture, FPA) tragen dazu bei, die Energieef- fizienz von GenAI-Prozessoren zu verbessern und den Stromkonsum von generativer KI besser mit den gesellschaftlichen Umwelt- und Naturschutzzielen in Einklang zu bringen.

Der Autor

Maury Wood

ist Vice President Strategic Marketing bei Vicor. Vor dieser Tätigkeit hatte er leitende Positionen bei Broadcom, NXP, Analog Devices und Cypress inne. Er hält einen Bachelor of Science in Elektrotechnik von der University of Michigan und absolvierte Aufbaustudiengänge an der Northeastern University, dem Babson College und dem MIT.