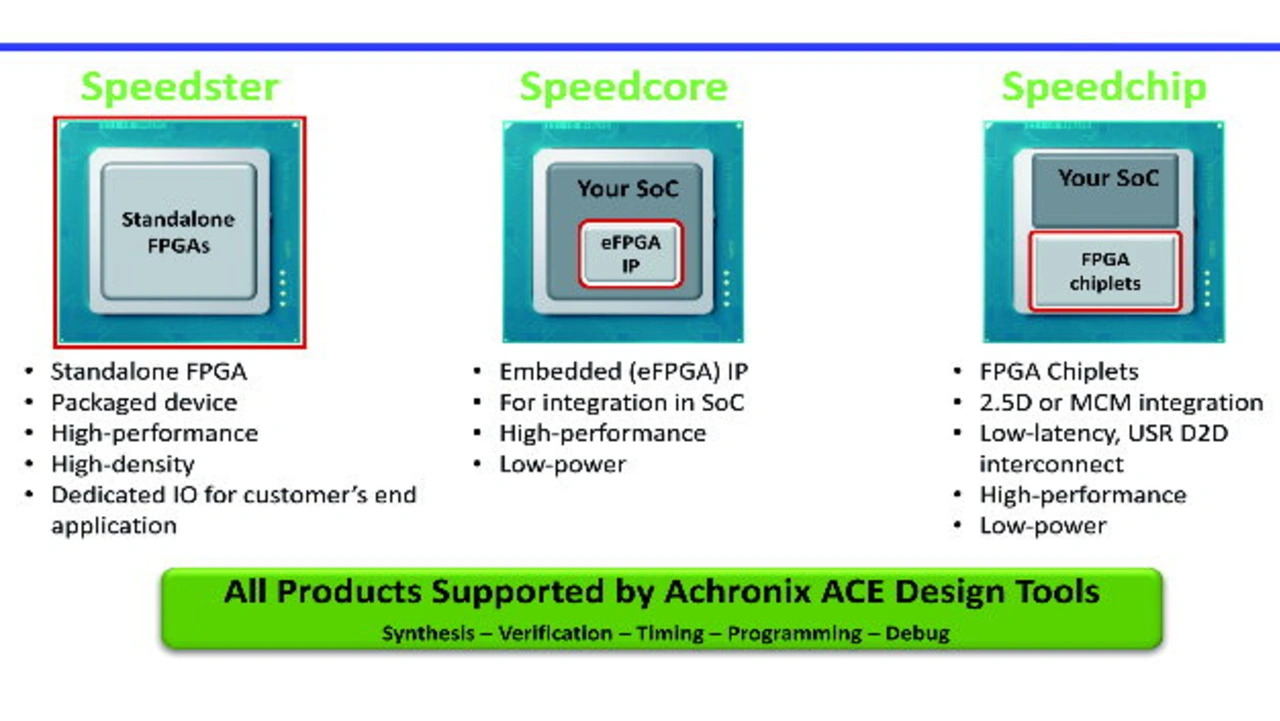

Achronix: FPGAs, eFPGAs und SiPs

Auf drei Gleisen ab durch die Decke

Fortsetzung des Artikels von Teil 1

Speedcore wird Erfolgsgeschichte...

Als Speedcore auf den Markt gebracht wurde, hieß es, dass die meisten Kunden dafür Systemhersteller sind. Aber es dürfte doch auch viele Halbleiterhersteller geben, die daran interessiert sind?

Ja, die sind ebenfalls daran interessiert, aber ich kann derzeit keine Namen nennen. Aber ganz klar: Wir haben mittlerweile auch Halbleiterunternehmen als Kunden.

Wo wird Speedcore am häufigsten eingesetzt?

Derzeit am meisten im Computing- und Wireless-Networking-Bereich. Aber wir sehen auch Vorteile in Speichersystemen, also den „Smart Storages“. Auch hier könnte eFPGA sehr interessant sein, aber das ist noch in einer frühen Phase. Weitere sehr wichtige Anwendungen finden sich selbstverständlich auch im KI-Umfeld.

Speedcore wird also eine Erfolgsgeschichte?

Ja. Anfang der 80er waren Gate-Arrays nur mit Logik ausgestattet. Im Laufe der Zeit wurden immer mehr Funktionen integriert. Das Gleiche gilt für PLDs. Wenn man die modernen SoCs also mit modernen FPGAs vergleicht, zeigen sich viele Ähnlichkeiten. Aber in einem Punkt unterscheiden sie sich: Man findet auf den SoCs kein FPGA als Building-Block.

Warum?

Aus wirtschaftlichen Gründen. Aber mit der Entwicklung auf der Fertigungsseite ist dieser Grund hinfällig. Früher war bei größeren Prozessstrukturen die Fläche, die ein eFPGA einnimmt, einfach zu groß und damit zu teuer.

Deshalb ist IBM mit seinem eFPGA bei 90 nm ja auch gescheitert …

Genau, mit 90 nm war die Fläche viel zu groß. Keiner wollte 100 Dollar an Zusatzkosten für sein ASIC bezahlen, nur um einen monolithisch integrierten FPGA-Block zu bekommen. Aber die Gesamtkosten für ein ASIC steigen und die Zusatzkosten für ein eFPGA sinken. Jetzt ist der Schnittpunkt erreicht, ab dem es sich lohnt, das eFPGA zu nutzen, um das ASIC zukunftssicher zu machen. Jetzt lassen sich neue Funktionen hinzufügen, etwa für einen neuen Verschlüsselungsalgorithmus oder für einen neuen Kompressionsstandard.

Wo liegt der Schnittpunkt?

Der Schnittpunkt liegt bei 22 nm. Das heißt, wir haben ihn schon überschritten, also es ist nicht mehr die Frage, ob eFPGA eingesetzt werden kann, sondern nur noch wann man es macht.

Speedster22i ist seit Ende 2013 in der Produktion. Wie sehen die Pläne für die Weiterentwicklung aus?

Auf Basis der 16-nm-Prozesstechnik bieten wir Speedcore und Speedchip an, aber keine Standalone-FPGAs. In der nächsten Generation setzen wir auf 7 nm und basierend darauf wird es Standalone-FPGAs und Speedcore geben.

Warum der Sprung gleich auf 7 nm?

Ganz einfach: Die Kunden, die wir heute mit unseren 16-nm-Produkten beliefern, wollen 7 nm.

Jobangebote+ passend zum Thema

- Auf drei Gleisen ab durch die Decke

- Speedcore wird Erfolgsgeschichte...