Packaging

Stacked-MOSFET steigern Effizienz und Leistungsdichte

Fortsetzung des Artikels von Teil 1

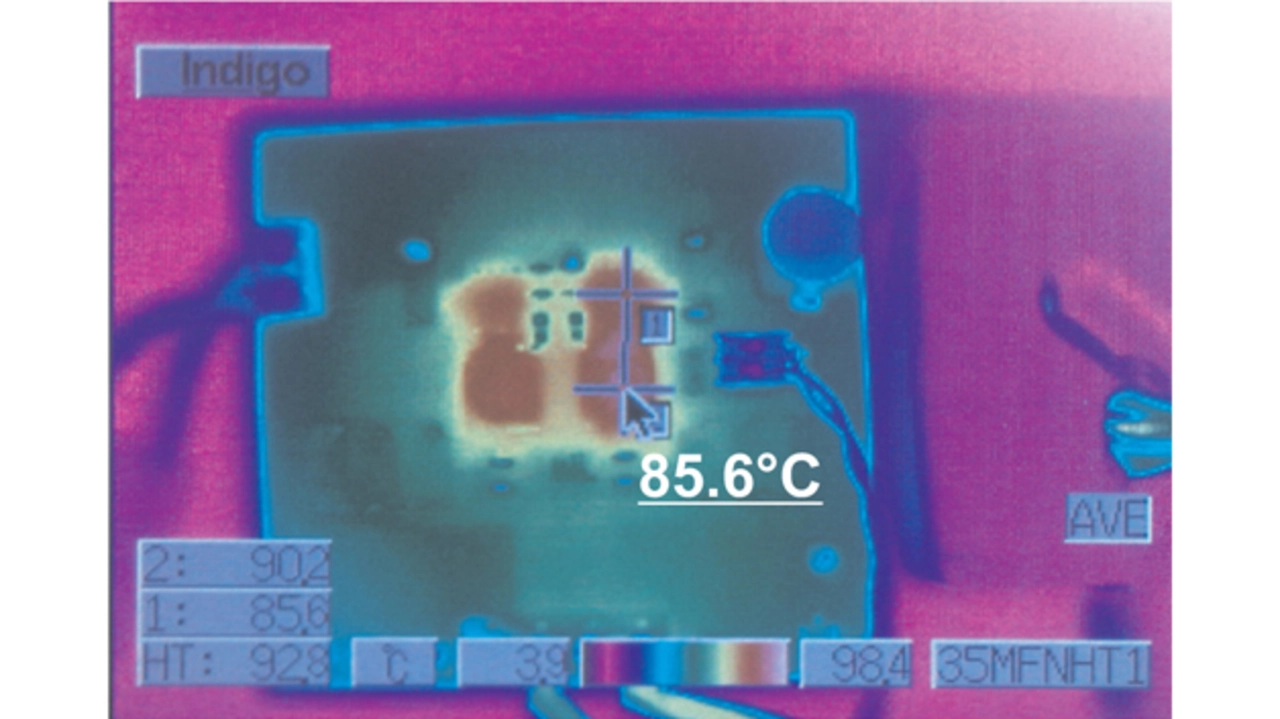

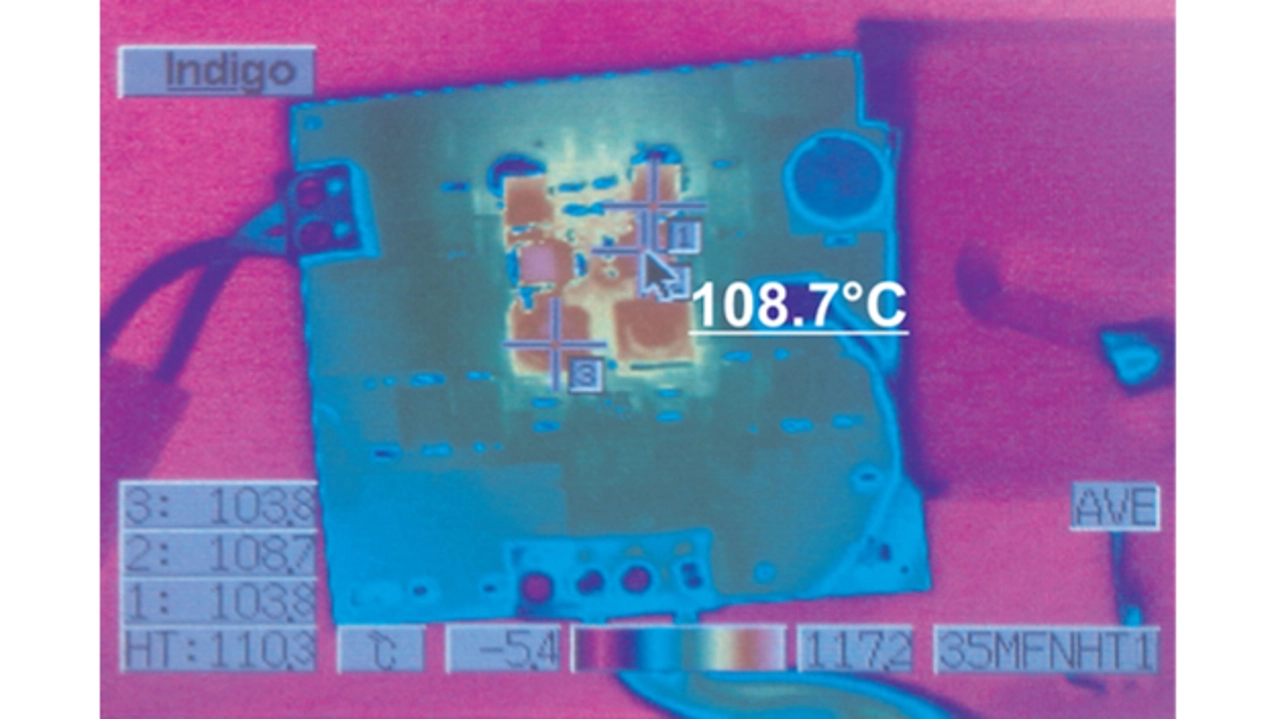

Niedrigere Betriebstemperatur

Die Verlustleistung eines Stacked-FET ist die Summe der Verlustleistungen des oberen und des unteren FET. Der Wärmewiderstand aber ist deutlich niedriger als bei diskreten FETs. Aus Bild 4 ist zu entnehmen, dass ein Stacked-FET-Schalter bei identischen Prüfbedingungen (Eingang 10 V; Ausgang 1,8 V/30 A; Schaltfrequenz 300 kHz) bei einer um 23 K niedrigeren Temperatur arbeitet. Während es der diskrete FET auf +108,7 °C bringt, erwärmen sich die Stacked-FET-Chips auf nur +85,6 °C.

Die große herausgeführte Metallfläche ist über zwölf thermische Durchkontaktierungen (Thermal Vias) mit der Massefläche der Leiterplatte verbunden. Dabei werden mehrere innenliegende Masseflächen verwendet, die es in modernen Multilayer-Leiterplatten üblicherweise gibt. Bei der Lösung mit diskreten FETs konzentriert sich die Wärme auf einer kleinen Fläche (Switching Plane), was die Verwendung mehrerer Vias aus Gründen der Signalintegrität verbietet.

Stacked-FET mit integriertem Treiber

Jobangebote+ passend zum Thema

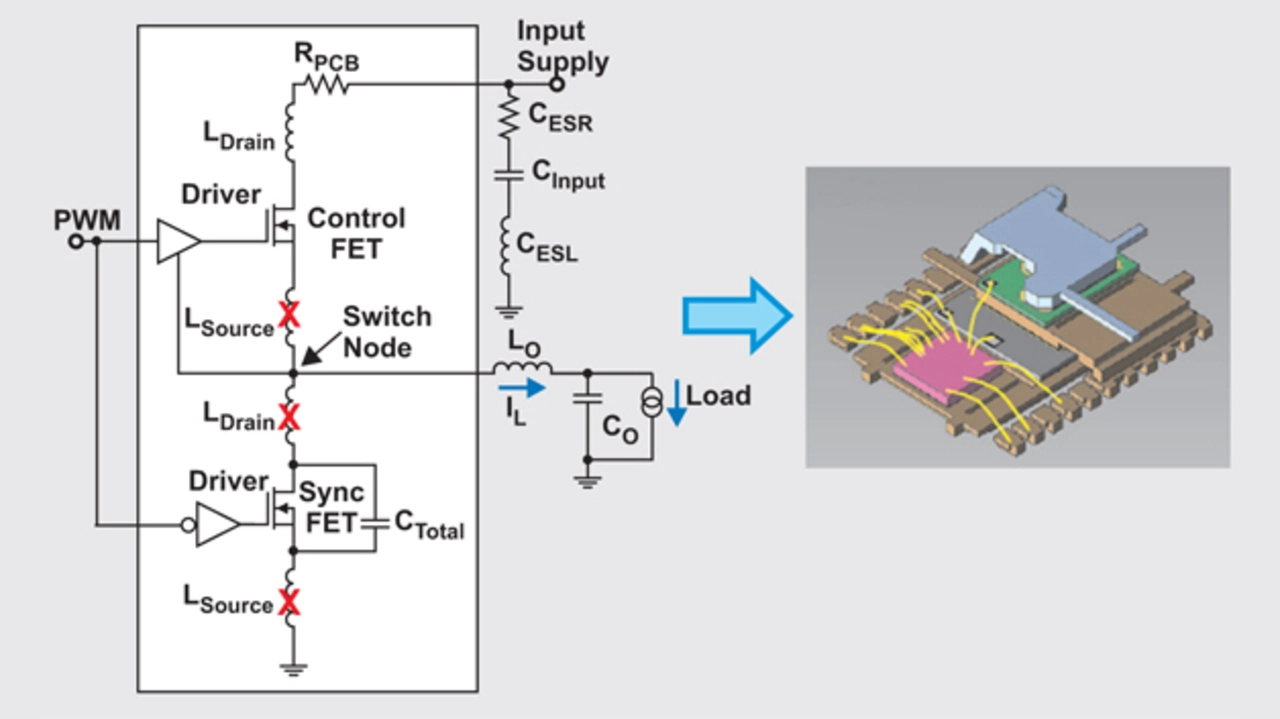

Um die technologischen Möglichkeiten noch weiter auszureizen, enthält der in Bild 5 gezeigte neue Baustein des Typs »CSD95372B« neben dem Stacked-FET-Schalter auch einen integrierten Treiber. Dabei behält das Gehäuse dieselbe Größe wie bei einem herkömmlichen FET (SO8 mit 5 x 6 mm Größe). Die reduzierte Distanz zwischen Treiber und FET senkt die parasitären Induktivitäten weiter und optimiert dadurch die Treibereigenschaften. Neben ihrer höheren Schaltgeschwindigkeit und ihrer niedrigeren Leitungsverluste kommt diese Lösung mit weniger Leiterplattenfläche aus, verbunden mit einem noch weiter gesteigerten Systemwirkungsgrad.

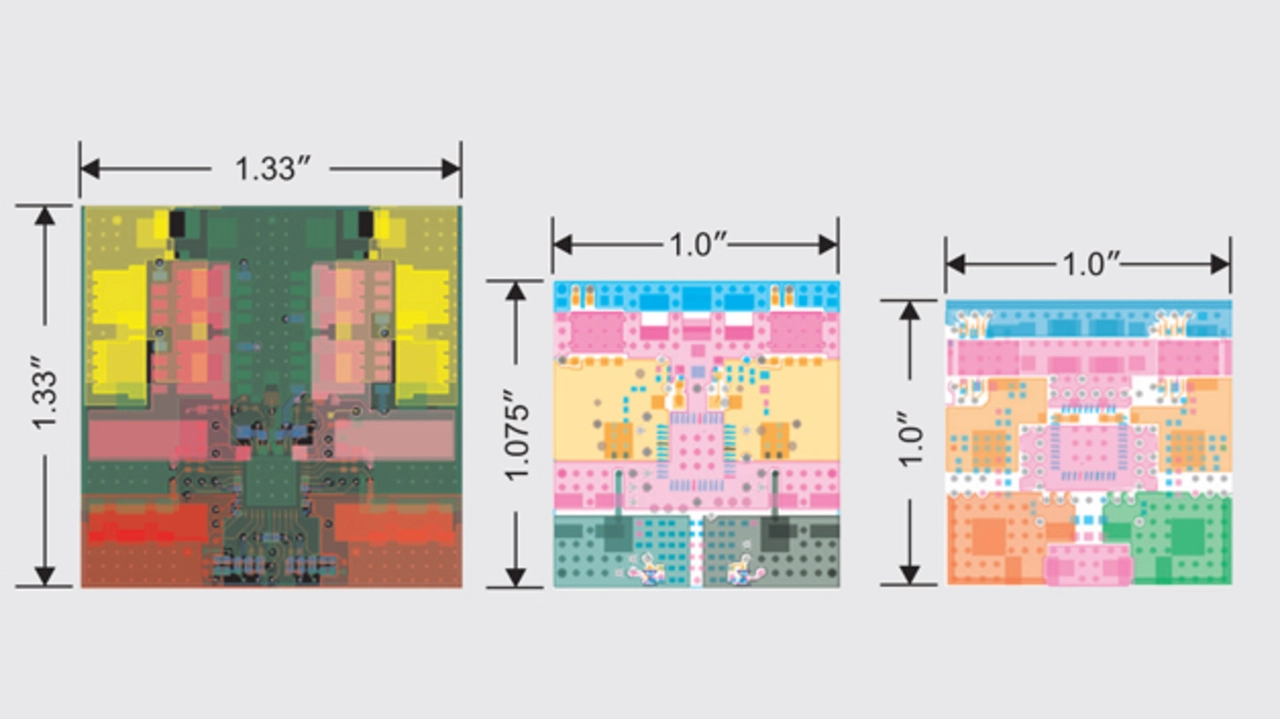

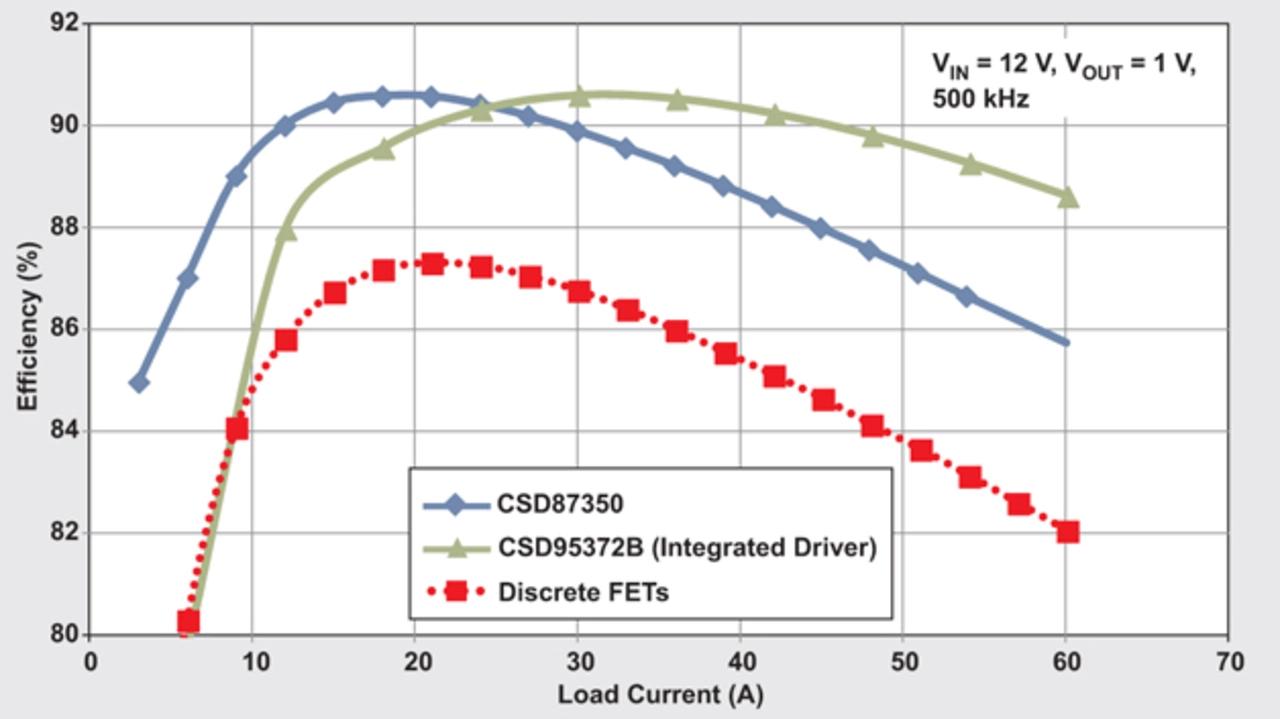

Zur Demonstration der Vorteile eines Stacked-FET mit integriertem Treiber wurde ein Design mit 1 V und 60 A herangezogen. Der Test erfolgte hier mit 12 V Eingangsspannung, 1 V Ausgangsspannung und einer Schaltfrequenz von 500 kHz. In der ursprünglichen Lösung kamen acht diskrete FETs zum Einsatz, die den Laststrom von 60 A lieferten. Wie Bild 6 zeigt, betrugen die Abmessungen dieser Lösung 33,8 mm x 33,8 mm.

In Bild 6b wurden die acht diskreten FETs durch zwei Stacked-FETs ersetzt, wodurch die Lösung nur noch 25,4 mm x 27,3 mm misst. Gegenüber der Variante mit diskreten FETs beläuft sich die Flächenersparnis auf 40 Prozent. Bild 6c zeigt die dritte Version, bei der zwei Stacked-FETs mit integriertem Treiber die acht diskreten FETs ersetzen. Die 25,4 mm x 25,4 mm große Lösung ist gegenüber der ursprünglichen Ausführung um 43 Prozent kleiner.

Testet man alle drei Varianten unter identischen Bedingungen, so bringt es die Lösung mit Stacked-FETs und integrierten Treiber auf den höchsten Wirkungsgrad von 88,6% (Bild 7) – das sind 6,6 Prozentpunkte mehr als bei der Lösung mit diskreten FETs und 2,9 Prozentpunkte mehr als bei der Stacked-FET-Lösung ohne integrierte Treiber (jeweils beim vollen Laststrom von 60 A).

- Stacked-MOSFET steigern Effizienz und Leistungsdichte

- Niedrigere Betriebstemperatur