ISSCC 2023

Teslas D1-Chip

Seit ein paar Jahren laden die Veranstalter der ISSCC ganz gezielt Firmen für Vorträge über einen von ihnen entwickelten Halbleiter ein, auch wenn der Chip schon vorgestellt wurde. Voraussetzung: Das Design muss besonders sein.

Dieses Mal war neben Intel, Nvidia und Syntiant auch Tesla mit seinem D1-Chip dabei.

Aber nicht nur das Design ist außergewöhnlich, die ISSCC-Veranstalter begründen ihre Entscheidung für Tesla beispielsweise auch damit, dass insbesondere die Automobilindustrie in Hinblick auf das autonome Fahren sehr stark an Hardware für maschinelles Lernen interessiert ist, und das sowohl für die Inferenzierung als auch für das Training. Darüber hinaus sind die Veranstalter überzeugt, dass die Tesla-Entwicklung einen klaren Trend markiert: Statt wie bisher für das Training der KI-Modelle auf Rechenzentren mit Unmengen von GPUs zu setzen, findet ein Wechsel hin zu hoch optimierten ASICs statt, um dadurch die Rechenleistung und die Energieeffizienz zu erhöhen.

Tesla hatte bereits 2019 angefangen, über »Dojo« zu sprechen. Das Unternehmen nutzt seit Jahren leistungsstarke Rechenzentren für das Training seiner KI-Modelle – bisher auf Basis von Nvidia-GPUs. Tesla wollte aber mehr und hatte sich zum Ziel gesetzt, mit Dojo einen eigenen Supercomputer zu entwickeln. 2021 wurde das Unternehmen auf seinem AI Day dann konkret: Dojo sollte 2022 in Betrieb gehen (das hat nicht ganz geklappt), basierend auf einer eigenen ASIC-Entwicklung namens D1 – einem Prozessor, der speziell auf das Training von ML-Anwendungen optimiert ist. Die damals genannten Ziele formulierte Ganesh Venkataramanan, Senior Director Autopilot Hardware von Tesla, auf diesem Event. Laut seiner Aussage war es das Ziel war, mit Dojo dank spezieller Hardware im Vergleich zu den bisher genutzten Supercomputern auf Basis von Nvidia-Chips die Trainings-Leistung zu erhöhen, größere und komplexere Modelle verarbeiten zu können und das Ganze auch noch energieeffizient und kosteneffektiv.

Bei dem D1-Prozessor setzt Tesla auf eine verteilte Rechnerarchitektur, bei der die einzelnen Einheiten über ein 2D-Mesh-Netz verbunden sind. Und auch wenn der Ansatz ähnlich zu anderen ist, unterscheidet sich Tesla doch gewaltig von bisherigen Ansätzen. Denn Tesla hat bei seiner Entwicklung zwei Punkte in den Vordergrund gestellt: geringe Latenzzeit und die Bandbreite muss skalierbar sein, Venkataramanan formulierte es so: »Die Skalierung der Rechenleistung ist einfach, aber es ist sehr schwierig die Bandbreite zu erhöhen und die Latenzen zu reduzieren.«

Die kleinste Einheit in der verteilten Rechenarchitektur vom D1 ist ein Trainings-Knoten. In Hinblick darauf erklärte Venkataramanan, dass das Unternehmen bereits hier genau überlegt hat, wie so ein Trainings-Knoten auszusehen hat: Einerseits darf er nicht zu klein sein, weil er dann zwar schnell rechnen kann, aber der Aufwand zur Synchronisierung zu hoch wird, anderseits darf er auch nicht zu groß sein, weil dann die Implementierung in Hardware komplexer wird und es typischerweise zu Engpässen im Speicher kommt. Anhaltspunkt für die Größe eines Trainings-Knotens war die Frage, welche Distanz ein Signal bei einer hohen Taktfrequenz (2 GHz) überwinden kann. In diesen damit vorgegebenen Rahmen hat das Tesla-Team dann seinen Trainings-Knoten hineindesignt und damit erreicht, dass auf alle Fälle die höchste Bandbreite erreicht wurde, mit der dieser Knoten mit Daten gefüttert werden kann.

Tesla hat seine Trainings-Knoten mit folgenden vier Funktionsblöcken ausgestattet: ein 1,25 MB großes SRAM (ECC-geschützt), eine superskalare 64-Bit-CPU mit Multithreading (vier Threads, sodass Berechnungen und Datentransfers gleichzeitig möglich sind) und SIMD-Fähigkeiten, vier Matrix-Multiplikationseinheiten und eine Anbindung an das NoC (Switch Fabric). Die Trainings-Knoten unterstützen alle gängigen Datentypen wie FP32, BFP16, Int 8 bis INT 32, wobei Tesla auch einen neuen Datentyp namens CFP8 (Configurable Floating Point 8) eingeführt hat, plus einen eigenen Befehlssatz (ISA), der ebenfalls auf ML-Aufgaben optimiert ist. Jeder dieser Trainings-Knoten kommt auf eine Rechenleistung von 1024 GFLOPS mit den Datenformaten BF16/CFP8 bzw. 64 GFLOPS mit FP32 und kann in jede Richtung Daten mit einer Geschwindigkeit von 512 GB/s zu seinen Nachbar-Trainings-Knoten übertragen.

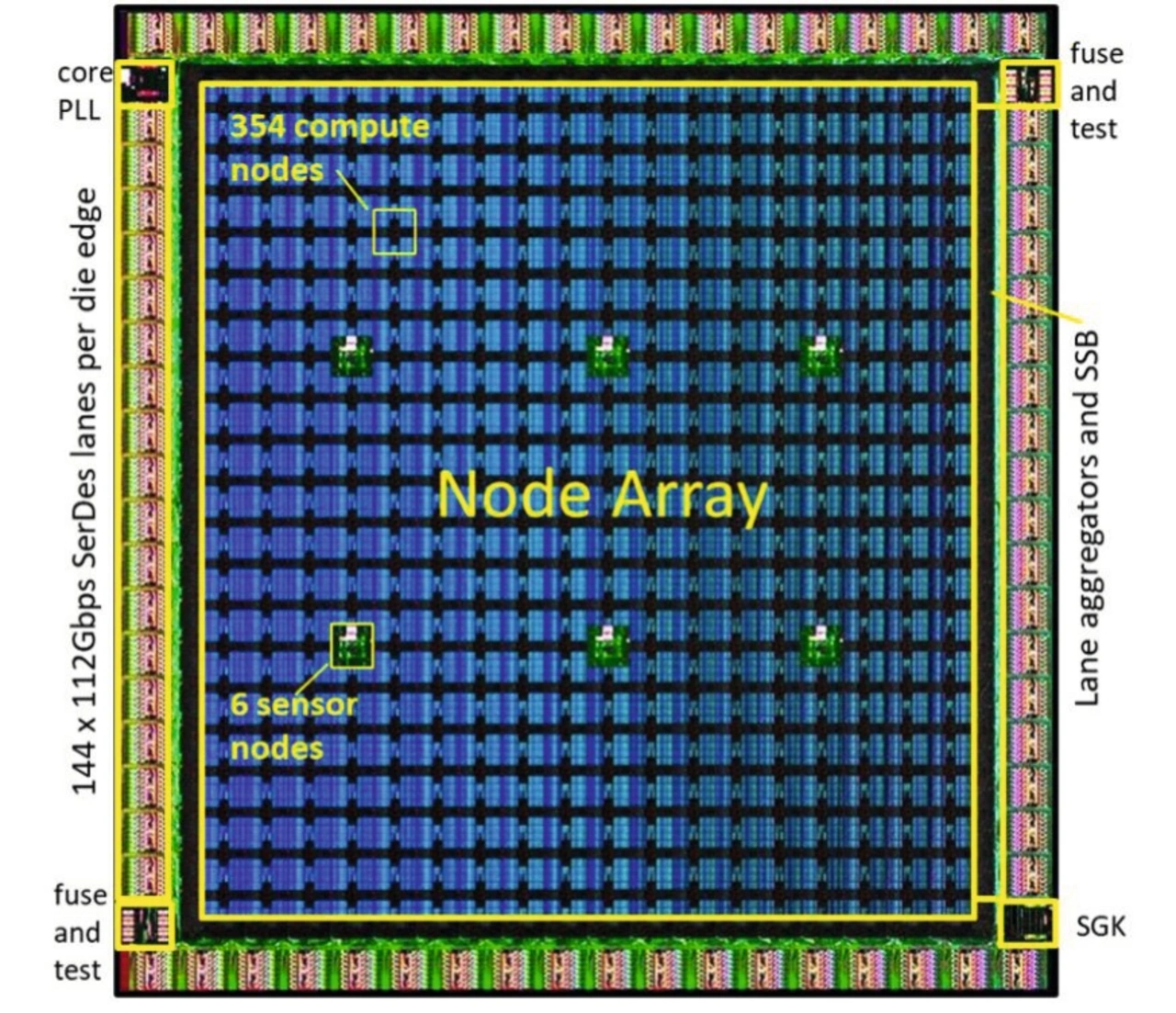

Pro D1-Chip sind 354 dieser Trainings-Knoten dank modularer Bauweise nebeneinandergesetzt, was eine Rechenleistung von 362 TFLOPs (BF16/CFP8) bzw. 22,6 TFLOPs (FP32) ergibt, die direktionale innerhalb des Chips ist mit 10 TB/s angegeben. Um dieses Rechen-Array hat Tesla einen Ring von Low-Power-SerDes-Anbindungen (576 Lanes @ 112 Gb) vorgesehen, sodass sich eine I/O-Bandbreite nach außen von 4 TB/s an jeder Seite des Chips ergibt. Der D1 wird mithilfe eines 7-nm-Prozesses von TSMC gefertigt und verfügt über 13 Kupfer-Lagen und einen Aluminium-RDL (Redistribution Layer). Auf dem D1-Chip sind 50 Mrd. Transistoren auf einer Fläche von 645 mm² integriert. Das TDP (Thermal Design Power) ist mit 400 W angegeben und sein Core-Takt liegt über 2 GHz. Venkataramanan: »100 Prozent der Chip-Fläche wird für das ML-Training und die Bandbreite verwendet, es gibt kein dunkles Silizium, kein Problem mit Legacy. Es ist eine Engine speziell für maschinelles Lernen.«

Noch eine Besonderheit des D1-Prozessors

Die Veranstalter der ISSCC wiesen noch auf einen weiteren Punkt hin, der das Tesla-Design besonders macht: Auf die Taktgenerierung. Tesla setzt nämlich nicht auf eine globale Taktverteilung, das Unternehmen nutzt eine wellenförmige Taktverteilung. Im Wesentlichen heißt das, dass in der oberen linken Ecke der Takt eingespeist wird und sich dann diagonal über das gesamte Array ausbreitet. Das heißt, dass ein Trainings-Knoten von seinem linken und oberen benachbarten Knoten ein Taktsignal erhält, diese zwei Takte zu einem rekombiniert und diesen einen Takt dann an seine zwei Nachbarknoten rechts und unten weitergibt. Die daraus resultierende Taktarchitektur ist somit lokal synchron, global aber mesochron. Damit ergeben sich zwei Vorteile: Zum einen kann sich Tesla den Aufwand sparen, den eine globale Taktverteilung mit sich bringt, sprich die Metalllagen für die Power-Distribution fallen weg und auch die Leistungsaufnahme, die damit verbunden ist. Zum anderen ermöglicht diese wellenförmige Taktverteilung eine natürliche di/dt-Abschwächung, sprich das Rauschen durch die Stromversorgung wird verringert.

Vom Chip zum System

Nachdem sich die D1-Chips problemlos ohne zusätzliche Glue-Logik mit anderen D1-Chips verbinden lassen, hat Tesla ein System mit 500.000 Trainings-Knoten in eine Recheneinheit (1500 D1-Chips) zusammengesetzt, und diese mit zwei selbst entwickelten Dojo-Interface-Prozessoren mit PCIe-Gen4-Schnittstellen versehen, die als Brücke zu den Host-Systemen fungieren. Um 25 dieser Recheneinheiten in einer Trainings-Kachel (Training Tile) zu integrieren, nutzt Tesla einen Fan-out-Wafer-Prozess, bei dem 25 ungehäuste ICs (Known Good Dies) auf einem Wafer so eng zusammengesetzt werden können, dass die Bandbreite zwischen den ICs erhalten bleibt.

Für dieses Training-Tile hat Tesla auch eigene Anschlussmöglichkeiten entwickelt, sodass auf jeder Seite eine Bandbreite von 9 TB/s zur Verfügung steht. Das heißt, dass ein Trainings-Tile auf eine Gesamtbandbreite nach außen in Höhe von 36 TB/s und eine Rechenleistung von 9 TFLOPs (BF16/CFP8) kommt. »Das ist vielleicht das größte organische Multi-Chip-Modul der Halbleiterindustrie«, erklärte Venkataramanan weiter. Auch bei der Stromversorgung dieser Trainings-Tiles ging Tesla eigene Wege und entwickelte ein kundenspezifisches Spannungsreglermodul, welches direkt mithilfe eines Reflow-Prozesses auf den Fan-out-Wafer aufgebracht wird.

Dazu kommt noch ein Gehäuse plus Kühlung, sodass ein komplettes Gesamtsystem mit 9 TFLOPs realisiert wurde. Tesla will in seinen künftigen Rechenzentren in zehn Schränken insgesamt 120 dieser Trainings-Tiles mit 3000 D1-Chips und über 1 Mio. Trainings-Knoten integrieren, und somit eine Rechenleistung von 1,1 ExaFLOPs (BF16/CFP8) erreichen.