Brainchip: 2. KI-Plattform

KI für »jedermann«

Fortsetzung des Artikels von Teil 1

Eine Plattform – skalierbar für viele Anwendungen

Die Plattform soll zunächst IP-Cores in drei Varianten umfassen: Akida-E mit bis zu vier Knoten und bis zu 200 GOPS, Akida-S mit zwei bis acht Knoten und bis zu 1 TOPS und die leistungsstärkste Variante, Akida-P (optional mit Vision Transformer), mit 8 bis 128 Knoten und bis zu 50 TOPS. Was heißt das für die Anwendungsmöglichkeit? Als mögliche Anwendungen nennt Nayampally für die kleinen IP-Cores (Akida-E) beispielsweise Vibrations- oder Anomalie-Erkennung. Nayampally weiter: »Diese Anwendungen sind nicht neu, sie laufen auf MCUs, aber das ist definitiv nicht energieeffizient.« Für die IP-Cores der mittleren Leistungsklasse wiederum geht es um Applikationen wie Gestenerkennung oder Objektklassifizierung, und mit den Akida-P-Cores lassen sich Anwendungen wie fortschrittliche Spracherkennung oder Vision-Transformer-Netze realisieren. Dementsprechend erklärt Nayampally weiter, dass Brainchip mit den IP-Cores folgende Märkte adressiert: Industrie, Automotive, Health/Wellness, Home/Consumer.

Akida kann viel, was andere nicht können

Dazu gehört beispielsweise, dass Brainchip mit seiner Akida-Plattform der zweiten Generation laut Nayampally mehrere Layer gleichzeitig bearbeiten kann, aber auch, dass die Architektur verschiedene Gewichtungen und Aktivierungen (8, 4, 2 und 1 bit) unterstützt. Dazu kommt noch, dass das vollkommen digitale, Event-basierte Design auf alle Prozesstechnologien der Foundries/IDMs mit einem Standard-Synthese-Design-Flow portiert werden kann. Darüber hinaus kann die Architektur alle Arten von Netzen verarbeiten, einschließlich CNNs, DNNs, Vision-Transformer, native SNNs und Sequenz-Vorhersage – und das extrem energieeffizient. Nayampally weiter: »Die IP-Cores sind eigenständige, in sich geschlossene Systeme, sodass ein Eingreifen der CPU typischerweise nicht notwendig ist.«

»Unsere IP-Cores unterstützen auch einen Ansatz, den wir Multi-Pass-Processing nennen. Der Vorteil davon besteht darin, falls ein Entwickler beispielsweise platzbeschränkt ist und dementsprechend nur eine geringe Anzahl von Rechenknoten implementieren kann, ist das mit unserer Hardware kein Problem, denn dann werden die Berechnungen mehr sequenziell und weniger parallel durchgeführt. Damit lassen sich die Siliziumfläche und die Leistungsaufnahme im SoC reduzieren, und das macht die Architektur extrem skalierbar«, so Nayampally. Das ist laut seiner Aussage für den Anwendungsentwickler vollkommen transparent, er muss sich um nichts kümmern, alle dafür notwendigen Aufgaben werden von der Software während der Laufzeit durchgeführt. »Damit können wir auch zukünftige Modelle unterstützen«, erklärt Nayampally weiter. Dass bei einer sequenziellen Verarbeitung die Laufzeit etwas länger wird, will Nayampally nicht verhehlen, aber sie steigt nur leicht an und nicht linear, wie man vielleicht erwarten würde.

In Hinblick auf den optionalen Vision-Transformer merkt er noch an, dass es sich dabei um einen kompletten Encoder-Block in Hardware handelt, der optional zwei bis zwölf Knoten umfasst, die Vorteile der »At-Memory-Berechnung« nutzt, vollkommen eigenständig ist und wie die TENNs durch den DMA-Controller gesteuert wird.

Jobangebote+ passend zum Thema

- KI für »jedermann«

- Eine Plattform – skalierbar für viele Anwendungen

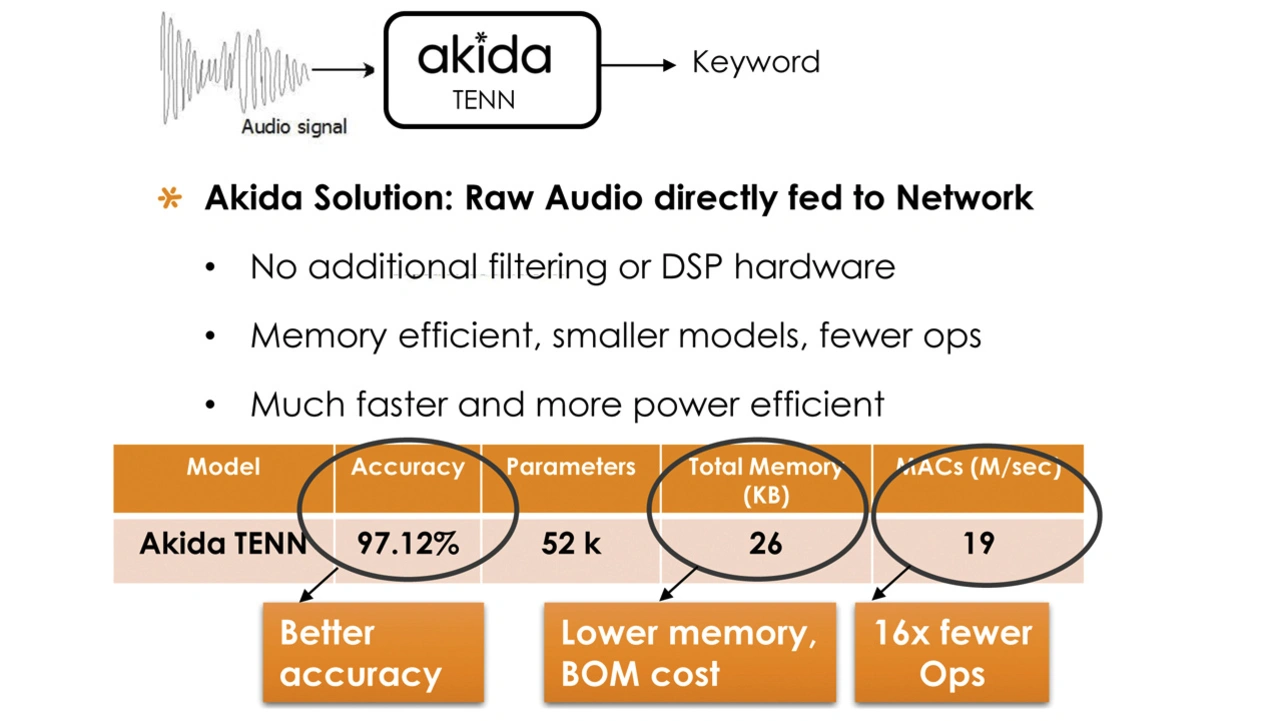

- Benchmark-Ergebnisse