ISSCC 2023

Europa kann auch digital

Europa hat zur diesjährigen ISSCC 27 Vorträge beigesteuert, also rund 14 Prozent aller vorgestellten Paper. Typischerweise ist Europa stark in Themen wie Power-Management, doch in diesem Jahr stach auch ein Paper zu einem digitalen Design hervor: ein heterogenes KI-SoC.

In der Session 22 »Heterogeneous ML Accelerators« gab es insgesamt neun Vorträge. Den Hintergrund dieser Session umschreibt das dafür zuständige Unterkomitee folgendermaßen: Tiefe neuronale Netze (DNNs) entwickeln sich ständig weiter und kommen in einem breiten Spektrum von Anwendungen zum Einsatz. DNNs bestehen mittlerweile aus unterschiedlichen Schichten wie Faltungsschichten oder Aufmerksamkeitsschichten, die sich in ihren Rechen- und Speicheranforderungen erheblich unterscheiden.

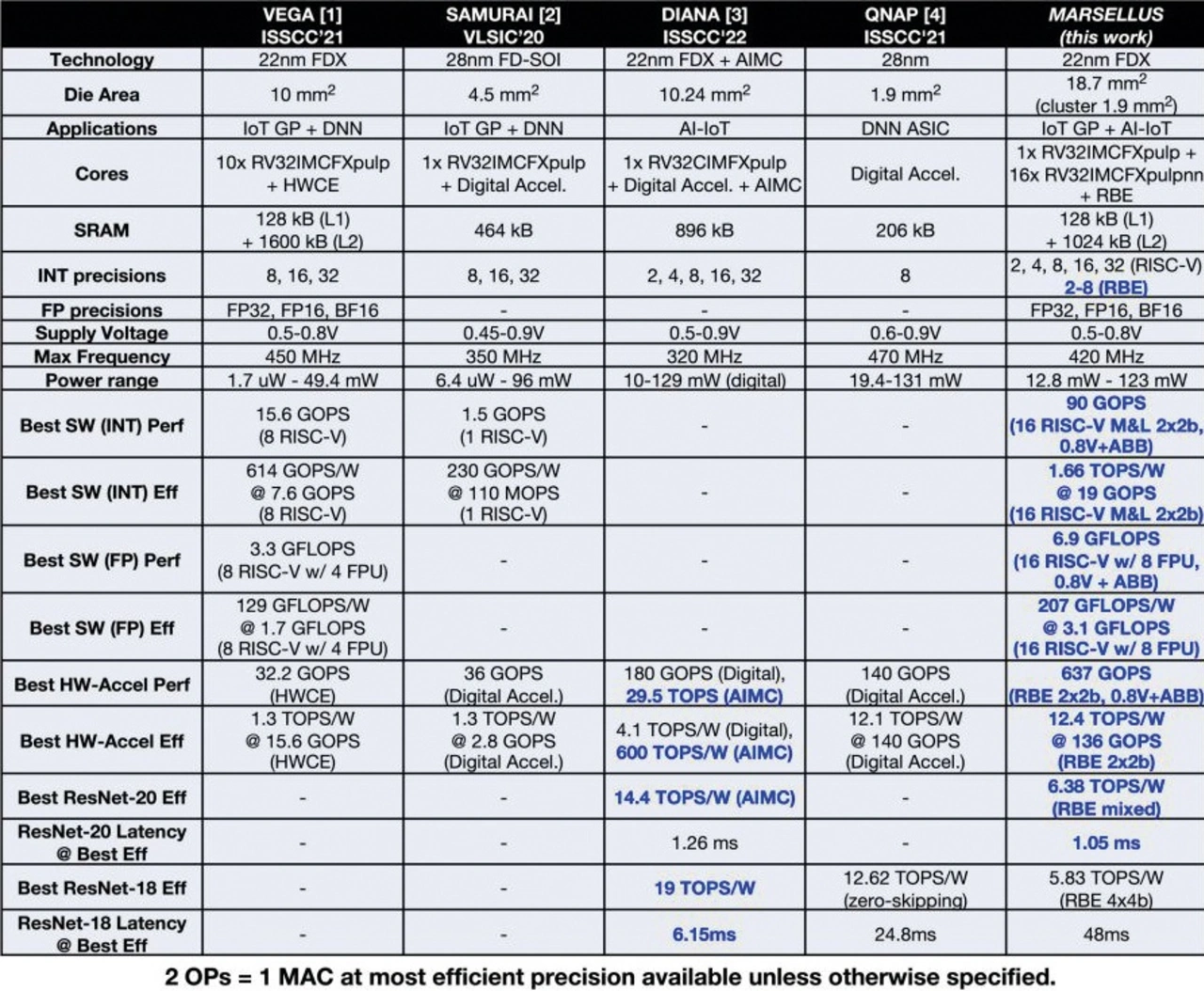

Daraus ergibt sich der Bedarf an heterogenen ML-Beschleunigern mit spezialisierten Kernen für unterschiedliche Aufgaben. Und aus Sicht der Experten des Unterkomitees hat eine europäische Entwicklung hier Ansätze verfolgt, die durchaus einzigartig und vielversprechend sind. Dabei handelt es sich um ein heterogenes KI-SoC für IoT-Anwendungen mit 12,4 TOPS/W bei 136 GOPS. Dieser Vortrag ist ein Gemeinschaftspapier der University of Bologna, ETH Zürich und Dolphin Design.

Die Verfasser des Vortrags betonen, dass KI-fähige SoCs in Anwendungen wie Augmented Reality, personalisierter Gesundheitsfürsorge oder Nanorobotik viele Aufgaben innerhalb eines relativ kleinen Leistungsbudgets von nur einigen Dutzend Milliwatt ausführen müssen. Diese Aufgaben umfassen sowohl rechenintensive Deep Neural Networks (DNNs), die in Hinblick auf die Präzision flexibel sind, aber auch Signalverarbeitungs- und Steuerungsaufgaben, die hochpräzise Fließkommazahlen erforderlich machen.

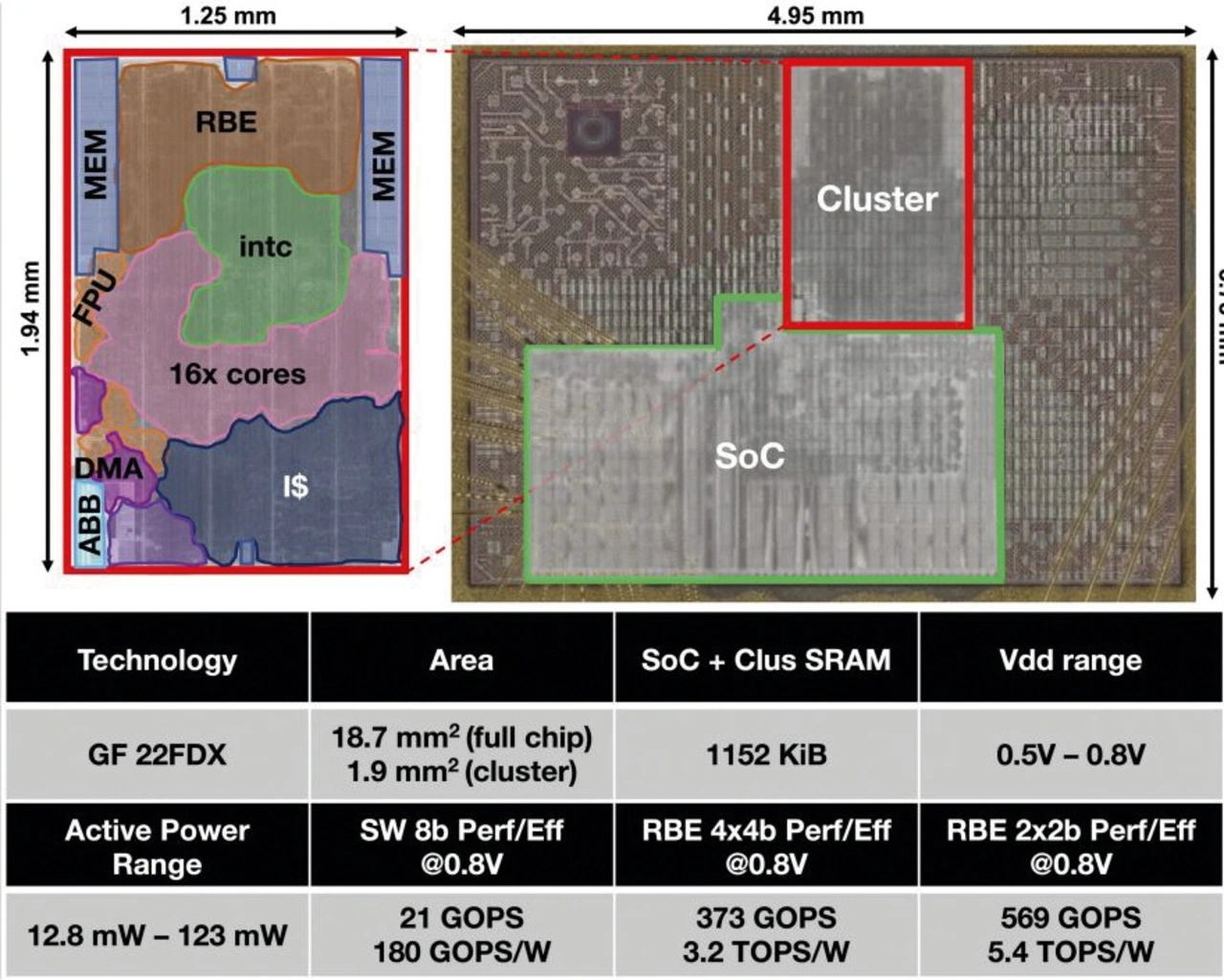

Daraus folgt, dass sich die Leistungs- und Energiebeschränkungen unterschiedlich stark auf die verschiedenen Anwendungen und sogar innerhalb verschiedener Phasen derselben Anwendung auswirken. Um hier Abhilfe zu schaffen, hat das Forscher-Team »Marsellus« entwickelt. Dabei handelt es sich um ein vollständig digitales, heterogenes KI-IoT-Endknoten-SoC, das GlobalFoundries mithilfe eines 22-nm-FDX-Prozesses (FDSOI-Technik) fertigt.

»Marsellus« zeichnet sich aus der Sicht der Entwickler durch drei entscheidende Ansätze aus, mit denen sich Rechenleistung und Leistungsaufnahme entsprechend den Anforderungen skalieren lassen:

- Ein General-Purpose-Cluster mit 16 RISC-V-DSP-Kernen, die auf die Ausführung einer Vielzahl von Workloads optimiert sind und mit »XpulpNN«-ISA-Erweiterungen für eine 4-bit- und 2-bit-Arithmetik ausgestattet sind. Die Erweiterungen unterstützen auch fusionierte MAC&Load-Operationen (M&L) und Gleitkommaberechnungen.

- Eine zwischen 2 und 8b rekonfigurierbare Binär-Engine (RBE), die 3×3- und 1×1-Faltungen in DNNs beschleunigt.

- Diverse On-Chip-Monitoring-Blöcke (OCM), die mit einem ABB-Generator (Adaptive Body-Bias) und einem Hardware-Regelkreis verbunden sind und eine On-the-Fly-Anpassung (im Lauf) der Transistorschwellenspannungen ermöglichen.

Jobangebote+ passend zum Thema

Marsellus nutzt drei verschiedene Power-Domänen: SOC, Always-on und Cluster. Die SOC-Domäne besteht aus einem Mikrocontroller mit einem speziellen RISC-V-Kern (RV32IMCFXpulp), einem autonomen I/O-DMA-Controller und einem 1 MB großen L2-Speicher (960 kB verschachtelt in vier SRAM-Banken + 64 kB zusammenhängend in zwei Bänken). Das KI-SoC verfügt über ein Boot-ROM und drei FLLs (Frequeny-Locked Loops) für den SoC-Kern, die Peripherals und das Cluster. Das Cluster ist eine Insel, die hinsichtlich der Frequenz/Leistung unabhängig ist und die mit 16 RV32IMCFXpulpNN-Prozessorkernen und der rekonfigurierbaren Binär-Engine (RBE) ausgestattet ist.

Die Cores und die RBE teilen sich dasselbe 128 kB große L1-SRAM (TCDM: Tightly Coupled Data-Memory). Der TCDM ist in 32 Bänken organisiert, auf das über ein Interconnect mit einer aggregierten Gesamtbandbreite von 400 Gbit/s bei 420 MHz mit 0-Wait-States zugegriffen werden kann. Das Cluster umfasst auch einen DMA-Controller mit einem Durchsatz von 64 bit/Zyklus (sowohl beim Lesen als auch beim Schreiben), der den Datentransfer zwischen L2- und L1-Caches übernimmt. Die RISC-V-Cores unterstützen dank der benutzerdefinierten ISA-Erweiterung »XpulpNN« auch kleine Bitbreiten (2, 4, 8 bit) sowie, wie bereits erwähnt, fusionierte M&L-Befehle.

M&L-beschleunigte Kernel erreichen eine Auslastung der MAC-Einheiten von bis zu 94 Prozent, das sind 67 Prozent mehr als bei Ansätzen, die nicht auf eine Fusionierung von M&L setzen. Jeder »XpulpNN-RISC-V-Core« braucht 78 kGE (kilo-gate equivalent), also 17,5 Prozent mehr Fläche als ein Basis-RISC-V-Core, aber diese Cores zeichnen sich durch eine Leistungssteigerung mit einem Faktor von bis zu 12,7 gegenüber anderen RISC-V-Kernen für kleine Bitbreiten aus. Die speziellen RISC-V-Kerne teilen sich außerdem acht FPUs, die die Formate »FP32«, »FP16« und »BF16« unterstützen.

Damit wollen die Forscher sicherstellen, dass auch Verarbeitungsaufgaben effizient unterstützt werden, die nicht umfassend quantisiert werden können.

Die RBE ist eine Beschleunigerschaltung für DNN-Faltungsschichten mit einem vereinheitlichen Datenpfad. Sie kann zur Laufzeit rekonfiguriert werden, und zwar einerseits in Hinblick auf die verschiedenen Modi (3×3- und 1×1-Faltungen), aber auch in Hinblick auf die Aktivierungs-/Gewichtungsgenauigkeiten (asymmetrisch 2 bis 8 bit). Die interne Hierarchie der RBE besteht aus 81 Blöcken und 324 sogenannten Binary Convolvers (BinConv), die sich jeweils aus 32 binären 1-bit-Multiplikatoren (Und-Gattern), einem Addierbaum und einem Skalierungsblock zusammensetzen. Die RBE unterstützt dank seiner Implementierung DNNs mit gemischter Genauigkeit, bei denen I (Input), O (Output) und W (Weights) beliebig auf einen Wert zwischen 2 und 8 bit gesetzt werden können.

Mit insgesamt 10368 1×1-bit-Produkten liefert das RBE einen Spitzendurchsatz von 1610 ops/Zyklus im 3×3-Modus mit W = 2, I = 2/4, O = 2/4. Der Datenpfad hat eine Komplexität von 605 kGE, was 92 Prozent des gesamten Beschleunigers (652 kGE) ausmacht. Der Rest verteilt sich auf Lade-/Speichereinheit (2 Prozent), Register-File (3 Prozent) und Programmierschnittstelle + Controller FSM (3 Prozent). Normalerweise arbeitet die RBE mit 4-bit-Eingangswerten unter Verwendung aller vier BinConvs pro Block.

- Europa kann auch digital

- Bis zu 97-fache Verbesserung in Hinblick auf die Energieeffizienz