Neuronale Netze

Höhere Effizienz dank spezifischer Modelle

Neuronale Netzwerke lassen sich kategorisieren als Satz von Algorithmen, die in gewissem Sinne ähnlich dem menschlichen Gehirn modelliert sind und durch die Einbeziehung neuer Daten »lernen« können. »Berechnungseffiziente« neuronale Netzwerkmodelle sind ein vielversprechender Ansatz.

Bei der Implementierung von Hardware-Beschleunigern für die Inferenz (Schlussfolgerung in KI-Systemen) spielt die Art der Speicherzugriffe eine wesentliche Rolle. Im Kontext der Inferenz bei Machine-Learning-Implementierungen (ML) ist genau zu berücksichtigen, wie die Gewichtungen, als auch die Zwischenwerte der Aktivierung gespeichert werden. In den letzten Jahren wurden dazu mehrere Verfahren mit unterschiedlichem Erfolg genutzt. Die Auswirkungen der dabei getroffenen architektonischen Entscheidungen sind erheblich:

Jobangebote+ passend zum Thema

![Schema der TPUv1-Architektur [1]. Schema der TPUv1-Architektur [1].](https://cdn.elektroniknet.de/thumbs/media_uploads/images/1610555822-279-worbxyhtd.jpg.1280x0.webp)

- Latenz: Speicherzugriffe auf die Caches L1, L2 und L3 zeigen eine relativ niedrige Latenz. Wenn die Gewichtungen und Aktivierungen im Zusammenhang mit der nächsten Graph-Operation zwischengespeichert werden, lässt sich ein vertretbares Maß an Effizienz aufrechterhalten. Wenn allerdings auf externe Daten im DDR-DRAM zuzugreifen ist, entsteht ein Pipeline-Stau – mit dem zu erwartenden Einfluss auf die Latenz und Effizienz.

- Leistungsaufnahme: Der Energieaufwand beim Zugriff auf externe Speicher liegt mindestens eine Größenordnung höher als beim Zugriff auf interne Speicher.

- Rechnerauslastung: Applikationen sind im Allgemeinen entweder rechen- oder speicherintensiv. Dies kann das Maß der GOPS/TOPS beeinflussen, die in einem bestimmten Inferenz-Paradigma erreichbar sind. In einigen Fällen kann dieser Einfluss sehr signifikant sein. Es kann also in einer Inferenz-Engine mit einer Spitzenrechenleistung von 10 TOPS durchaus eine »Real-World-Performance« beim Einsatz in ihrem spezifischen Netzwerk von nur 1 TOPS vorliegen.

- Um diesen Gedanken einen Schritt weiter zu entwickeln, sollte man die Energiekosten beim Zugriff auf das interne SRAM betrachten (auch als BRAM oder UltraRAM bezeichnet, wenn man mit Xilinx SoCs vertraut ist). In einem aktuellen FPGA von Xilinx liegen diese in der Größe einiger Picojoule, etwa zwei Größenordnungen unterhalb des Zugriffs auf ein externes DRAM.

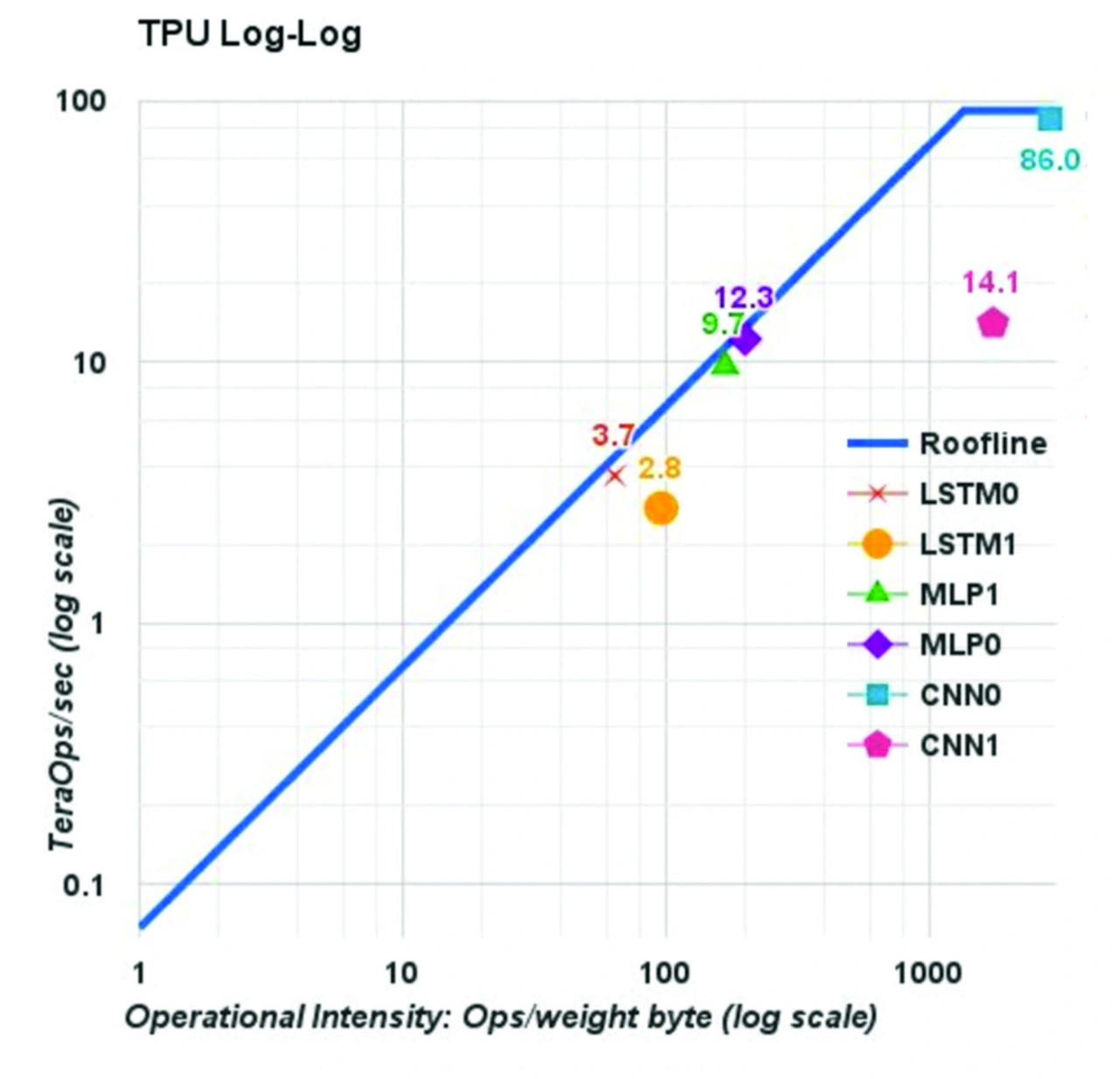

Als Beispiel für eine Architektur bietet sich die TPUv1 (Tensor Processing Unit) an (Bild 1). Die TPUv1 besteht aus einer MAC-Einheit (65.536 / INT8) zusammen mit 28 MByte Onchip-Speicher zum Ablegen von Zwischenwerten der Aktivierungen. Die Gewichtungen werden dabei aus einem externen DDR-DRAM geholt. Die theoretische Spitzenleistung der TPUv1 ist mit 92 TOPS angegeben [1].

Tensor Processing Unit (TPU)

Die TPU ist nur ein Beispiel für einen sehr verallgemeinerten Tensor-Beschleuniger, der einen komplexen Compiler für Graph-Operationen einsetzt. Die TPU realisierte eine sehr gute Effizienz beim Durchsatz spezifischer Workloads (CNN0 bei 86 TOPS). Allerdings ist das Verhältnis der Berechnungs- zur Speicher-Referenz für CNNs geringer als bei MLPs und LSTMs, und es ist ersichtlich, dass diese spezifischen Workloads Speicher-bezogen sind. CNN1 zeigt eine niedrigere Rechenleistung (14,1 TOPS) – als direkte Auswirkung von Pipeline-Staus, die entstehen, wenn neue Gewichtungen in die Matrix-Einheit geladen werden müssen (Bild 2).

Die Architektur eines neuronalen Netzes hat einen signifikanten Einfluss auf dessen Leistungsfähigkeit, und die Metrik der Spitzenleistung ist bei der Wahl einer Inferenz-Lösung nur von geringem Wert – außer es lassen sich hohe Wirkungsgrade für die spezifischen Workloads erzielen, die zu beschleunigen sind. Noch heute preisen viele SoC-, ASSP- und GPU-Hersteller ihre Performance Benchmarks für klassische Modelle zur Bildklassifizierung an, wie LeNet, AlexNet, VGG, GoogLeNet und ResNet. Doch die Anzahl der realen Anwendungsfälle für Aufgaben wie die Bildklassifizierung ist begrenzt, und in vielen Fällen werden solche Modelle nur zur funktionalen Back-End-Extraktion bei komplexeren Aufgaben wie Objekterkennung und Segmentierung eingesetzt.

Realistischere Beispiele für geeignete Modelle in realen Umgebungen sind die Objekterkennung und Segmentierung. Wie deckt sich das mit der Beobachtung,

dass man lange und genau suchen muss, ehe man offizielle IPS-Benchmarks für Netzwerke wie YOLOv3 und SSD findet? Und das trotz der Tatsache, dass viele Hableiterbausteine mit dem Schlagwort der »Top-10-Performance« vermarktet werden? Etwas locker formuliert, man kann davon ausgehen, dass dies kein Thema ist, wenn man einfach nur ein paar Fotos aus dem Cloud-Speicher mit dem Bild seiner Katze ausdrucken möchte (Bild 3).

Daher ist nicht verwunderlich, wenn viele Entwickler feststellen, dass ihr erster »Wurf« beim Design eines KI-basierten Produkts nicht die Anforderungen an die Leistungsfähigkeit erfüllt – was sie dazu zwingt, mitten im Designprozess auf eine andere Architektur zu wechseln. Das ist eine besondere Herausforderung, wenn dies den Umbau, sowohl der SOM-Baseboard-Hardware, als auch der Software bedingt. Dabei zeigt sich, dass ein Hauptmotiv bei der Wahl von FPGAs darin besteht, dass die Xilinx-Inferenzlösungen, anders als Wettbewerbskonzepte, direkt in ihrer Leistungsfähigkeit skalieren, und zwar um mehr als eine Größenordnung, wobei sie ihre Prozessor- und Inferenz-Beschleuniger-Architektur weiterhin beibehalten.

![Klassische gegenüber Kanal-bezogener Faltungs-Konnektivität [3]. Klassische gegenüber Kanal-bezogener Faltungs-Konnektivität [3].](https://cdn.elektroniknet.de/thumbs/media_uploads/images/1610557557-279-wor8736ko.jpg.1280x0.webp)

2017 präsentierte eine Forschergruppe von Google [2] eine neue Klasse von Modellen, die auf Mobilfunk-Applikationen zielte. Der Vorteil von MobileNet bestand in den beträchtlich reduzierten Rechenkosten bei gleichbleibend hoher Genauigkeit. Eine der in MobileNet realisierten Schlüsselinnovationen ist die Kanal-weise trennbare Faltung (Separable Depth-wise Convolution). Im Kontext der klassischen Faltung hat jeder Eingang einen Einfluss auf jeden Ausgangskanal. Wenn wir 100 Eingangskanäle und 100 Ausgangskanäle haben, gibt es 100 x 100 virtuelle Pfade. Allerdings teilt sich die Kanal-bezogene Faltung den Convolution Layer in 100 Gruppen auf, mit dem Ergebnis, dass es nur mehr 100 Pfade gibt. Jeder Eingangskanal ist also mit nur einem Ausgangskanal verbunden (Bild 4). Das erspart eine Menge an Rechenaufwand [3].

Verhältnis Rechner- zu Speicheraufwand

Ein Ergebnis dieser Betrachtung ist, dass für MobileNets das Verhältnis Rechner- zu Speicheraufwand reduziert ist – mit der Implikation, dass Speicherbandbreite und -latenz eine wichtigere Rolle spielen als die Erzielung eines hohen Durchsatzes.

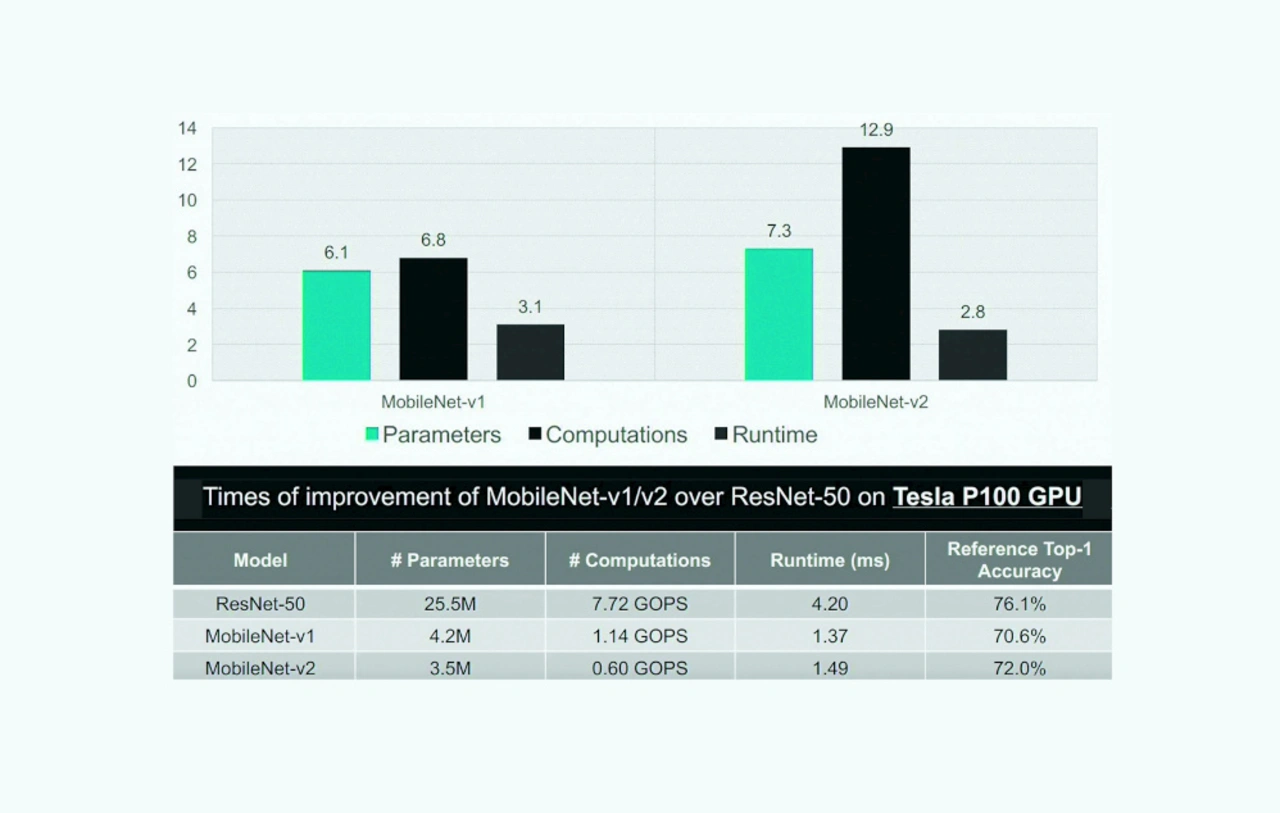

Unglücklicherweise sind recheneffiziente Netzwerke nicht unbedingt auch Hardware-freundlich. Idealerweise würde die Latenz in linearer Proportion zur Reduktion der Rechenleistung herunterskalieren. Doch es gibt nichts umsonst. Der Vergleich in Bild 5 belegt, dass die Workload der Berechnung für MobileNetv2 weniger als ein Zehntel der Workload von ResNet50 ausmacht. Allerdings folgt die Latenz nicht demselben Verlauf. In der Analyse nach Bild 5 ist klar ersichtlich, dass die Latenz nicht mit dem Faktor 12 proportional zur Reduktion Rechenleistung skaliert.

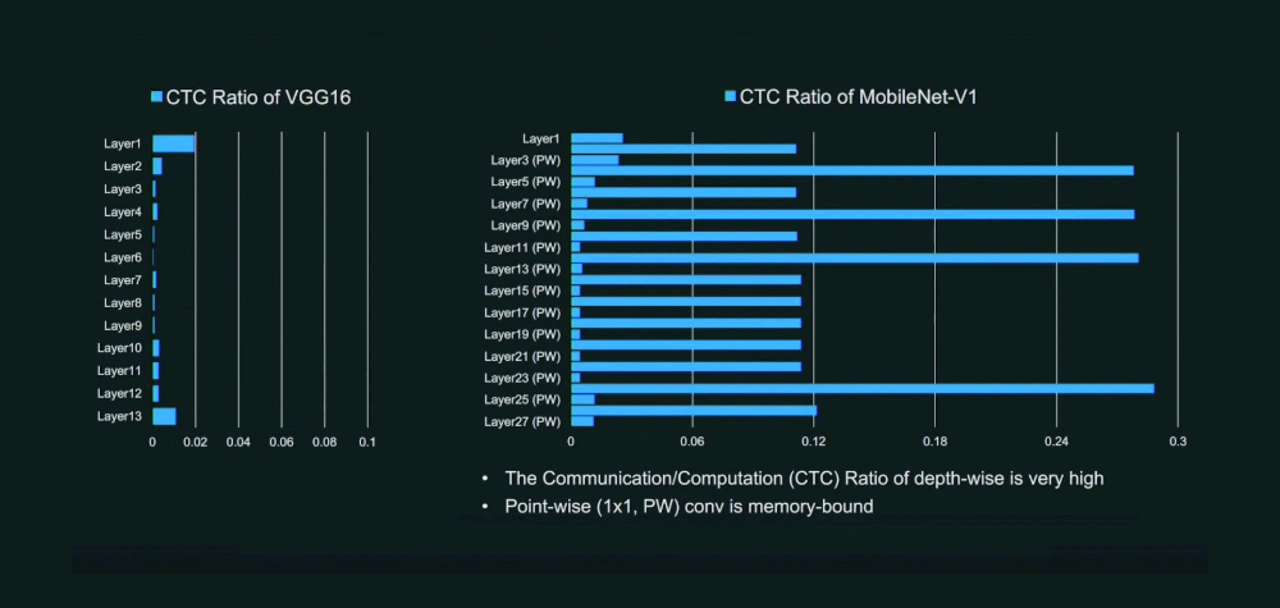

Wie lässt sich also dieses Problem lösen? Wenn man das Verhältnis der Off-Chip-Kommunikation gegenüber der Berechnung betrachtet, ist erkennbar, dass MobileNet im Vergleich zu VGG ein sehr unterschiedliches Profil aufweist. Im Fall der DWC-Layer sieht man, dass das Verhältnis 0,11 beträgt (Bild 6). Der Beschleuniger ist jetzt Speicher-gebunden und erzielt somit eine geringere Effizienz, da viele Elemente des PE-Arrays sich wie „Dark Server“ in einem Rechenzentrum verhalten, also Leistung und Chipfläche kosten, auch wenn sie keine nützliche Arbeit verrichten.

Deep Learning Processing Unit (DPU)

Als Xilinx die DPUv1 herausbrachte, war sie so ausgelegt, dass sie (wie andere Ops) die konventionelle Faltung beschleunigte. Konventionelle Faltung erfordert eine Kanal-bezogene Reduktion des Eingangssignals. Diese Reduktion ist optimal für die Hardware-Inferenz, da sie das Verhältnis der Berechnung gegenüber der Speicherung für die Gewichtung/Aktivierung erhöht. Bei der Betrachtung der Energiekosten für Berechnung versus Speicherung ist dies eine gute Sache. Das ist auch einer der Gründe dafür, dass der Einsatz von ResNet-basierten Netzwerken in Hochleistungsanwendungen so weit verbreitet ist – das Verhältnis des Berechnungs- zum Speicheraufwand ist bei ResNet höher als bei vielen historischen Backbones.

Kanal-bezogene Faltungen resultieren nicht in diesen typischen Reduktionen pro Kanal. Dafür wird die Speicher-Performance wesentlich wichtiger.

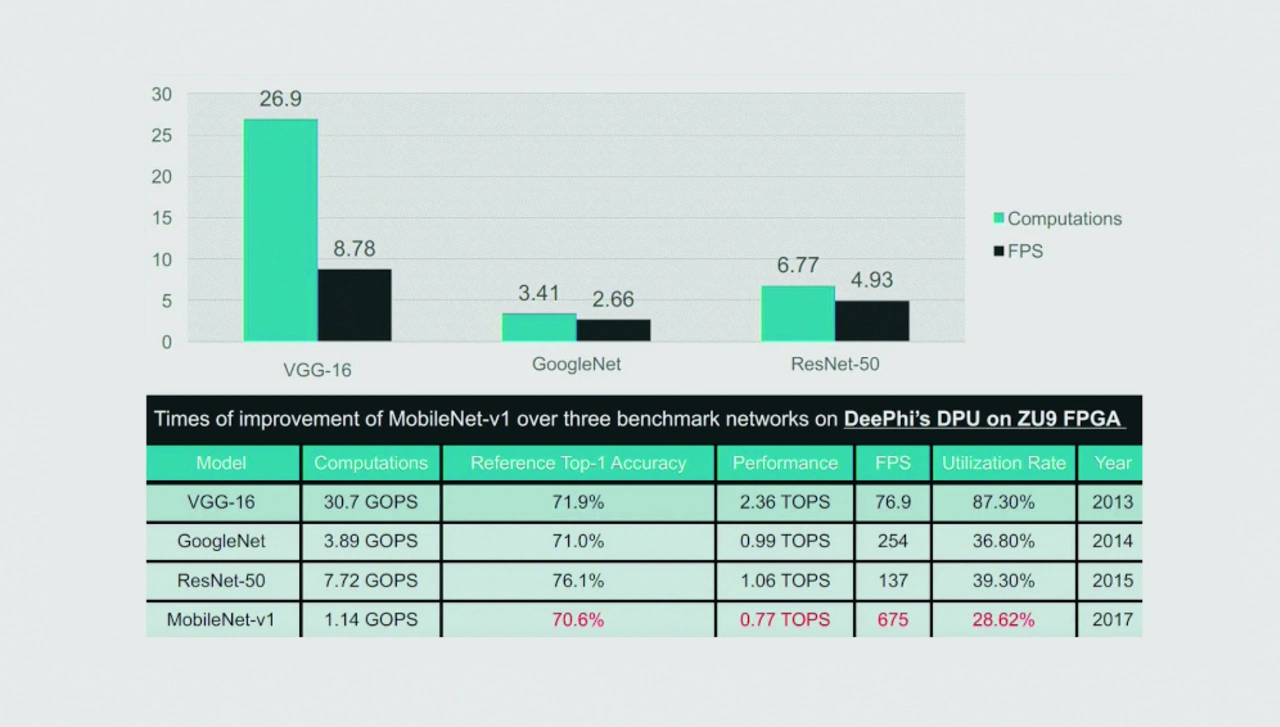

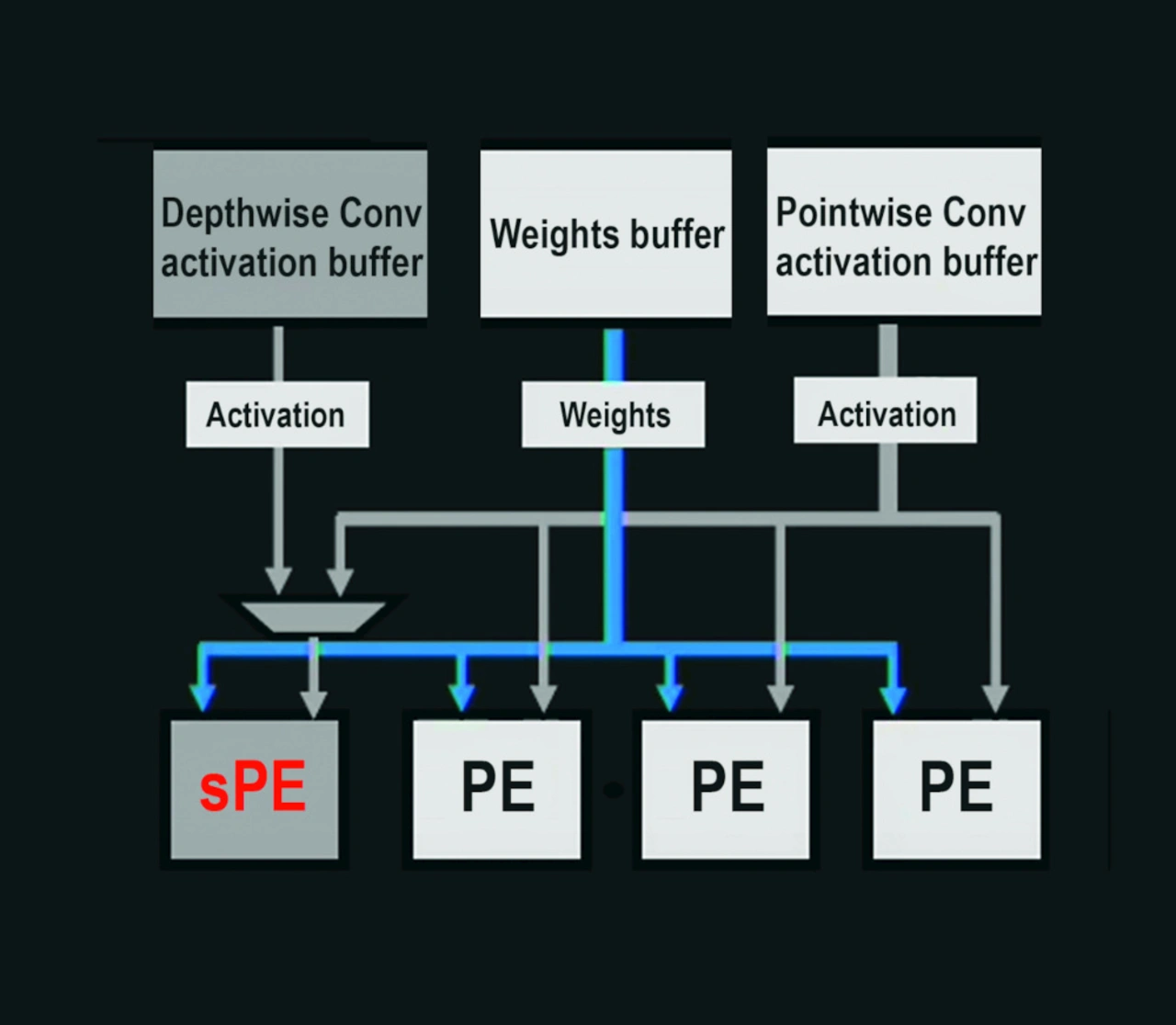

Für eine Inferenz fusioniert man typischerweise die DWC- mit der PWC-Faltung, legt die DWC-Aktivierungen im On-Chip-Speicher ab und startet gleich anschließend die 1x1-PWC. Im Kontext der Original DPU gab es keine spezialisierte Hardware-Unterstützung für DWCs, mit dem Ergebnis, dass der Wirkungsgrad nicht gerade ideal war (Bild 7) [3].

Um die DWC-Performance in der Hardware zu beschleunigen, wurde die Funktion der PEs (Processing Element) in der Xilinx DPU modifiziert und der DWC-Operator mit dem punktweisen CONV fusioniert. Nachdem ein Ausgangspixel in der ersten Schicht (Layer) verarbeitet wurde, wird die Aktivierung unmittelbar über die Pipeline an die 1x1-Faltung weitergeleitet (per On-Chip-BRAM-Speicher in der DPU), ohne sie in den DRAM zu schreiben. Mit diesem spezialisierten Verfahren lässt sich die Effizienz des MobileNet-Einsatzes auf der DPU wesentlich erhöhen (Bild 8) [3].

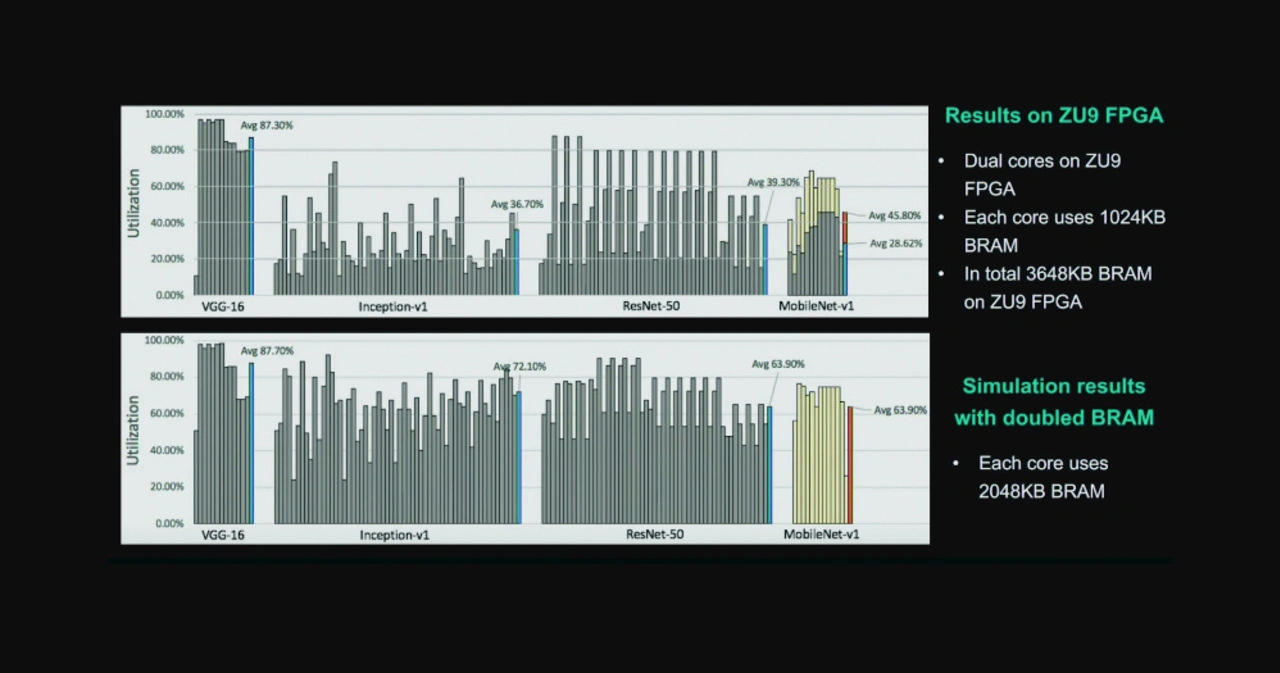

Mit dieser modifizierten DPUv2-Architektur ließ sich eine dramatische Verbesserung in der Effizienz der MNv1-Inferenz bewirken. Außerdem konnte, und zwar durch die Vergrößerung des On-Chip-Speichers, die Effizienz nochmals weiter gesteigert werden, sodass diese mit den ermittelten ResNet50-Ergebnissen gleichzieht. Und alles das wurde mit derselben CPU- und Hardware-Architektur erreicht (Bild 9) [3]. Es ist allgemein üblich, die Inferenz-Hardware und das Modell eines neuronalen Netzes getrennt voneinander zu optimieren. Man muss berücksichtigen, dass die Netzwerke im Allgemeinen mit GPUs trainiert werden, und am Edge SoCs oder GPUs mit absolut unterschiedlicher Architektur eingesetzt werden. Um die Gesamtleistung wirklich zu optimieren, ist die Hardware für effizient einsetzbare Modelle zu adaptieren, die nicht unbedingt Hardware-freundlich sind. Der Hauptvorteil der adaptierbaren Hardware in diesem Kontext besteht darin, dass die Ko-Evolution sowohl der Software, als auch der Hardware nach dem Tape-out fortgesetzt werden kann.

Verschlankung der Komplexität

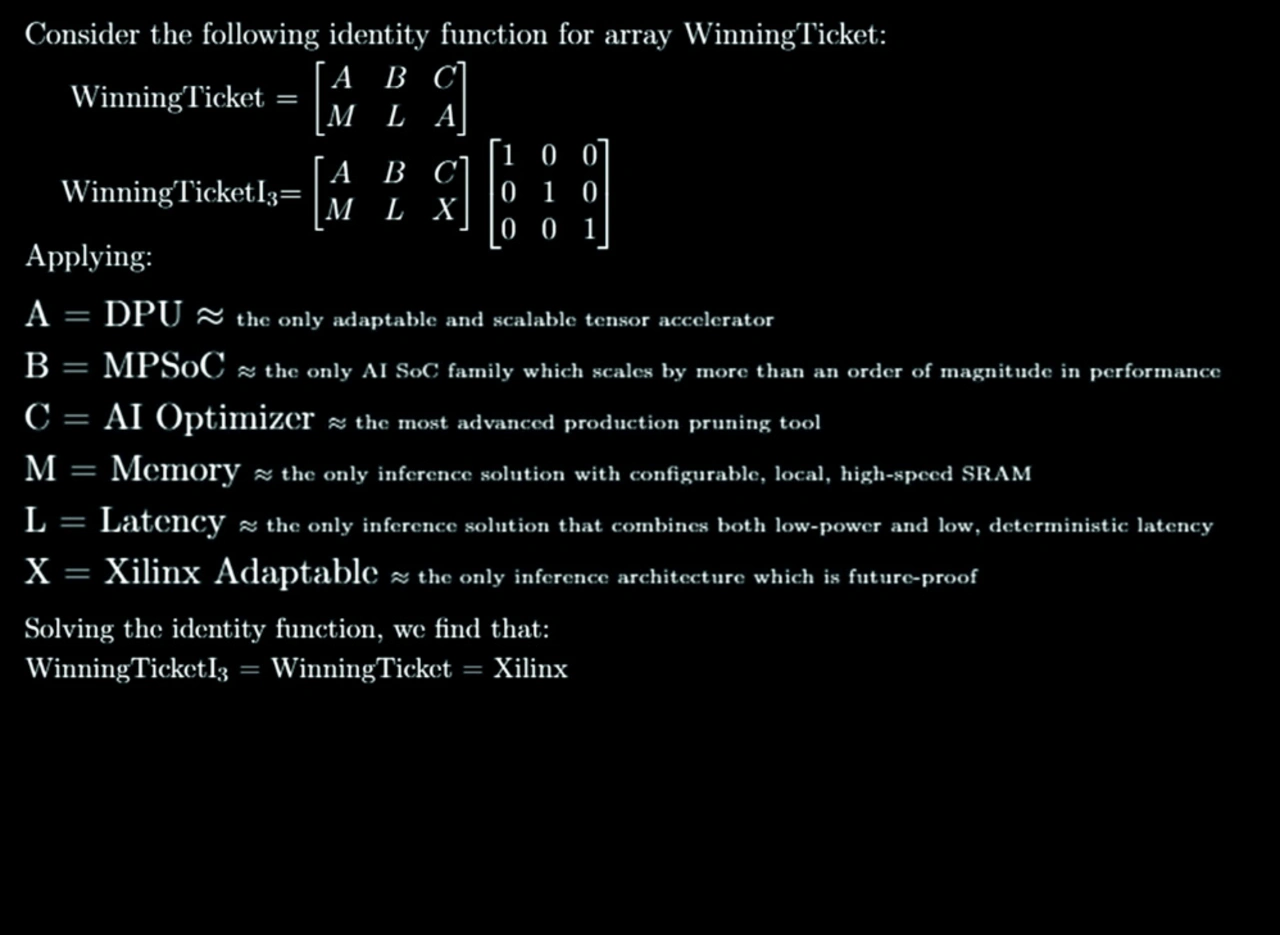

Um diesen Gedanken noch weiter zu entwickeln, bietet sich das grundlegende Paper mit dem Titel »The Lottery Ticket Hypothesis« von Frankle & Carbin [4] an.

In diesem Paper (einem von zweien, das auf dem ICLR2019 preisgekrönt wurde) stellen die Autoren die Hypothese auf, dass »dichte, zufällig initialisierte Feed-Forward-Netze Subnetze enthalten (als »Winning Tickets« bezeichnet), die – wenn man sie isoliert trainiert – eine Testgenauigkeit erreichen, die nach einer vergleichbaren Anzahl von (Trainings-) Iterationen mit dem Originalnetz vergleichbar sind.« Damit wird klar, dass es um die Zukunft der Netzwerkauslese weiterhin gut bestellt ist, und dass Verfahren wie AutoML bald den Platz der Winning Tickets im Verlauf der Entdeckung und Optimierung von Netzen einnehmen werden.

Ebenso ist wahr, dass die beste heutige Lösung zur Gewährleistung effizienter und hochgenauer Einsätze am Edge immer noch die Kanalauslese klassischer Backbones ist. Während diese Backbones im Einsatz vielleicht ineffizient sind, kann eine halbautomatische Kanalauslese solcher Backbones extrem effiziente Resultate liefern [5].

So wagt der Autor die Hypothese, dass Sie heute schon Ihr „Winning Ticket” ziehen können, indem Sie einfach eine Inferenz-Architektur wählen, die Ihr nächstes Design zukunftssicher macht (Bild 10). Damit haben Sie die Gewissheit, die Vorteile zukünftiger Netzwerk-Architekturen und Optimierungsstrategien zu nutzen, während Sie die Lebensdauer Ihres Produkts für Ihre Kunden ausdehnen. Nehmen Sie eine ZCU104 [6], laden Sie Vitis-AI [7] herunter, und starten Sie Ihre Reise in die Zukunft von KI.

Literatur

[1] TPUv1-Architektur: Jouppi et al. 2017, ftp/arxiv/ papers/1704/1704.04760.pdf" href="https://arxiv.org/ftp/arxiv/ papers/1704/1704.04760.pdf">https://arxiv.org/ftp/arxiv/

papers/1704/1704.04760.pdf

[2] »MobileNets: Efficient Convolutional Neural Networks for Mobile Vision Applications«: Howard et al, https://arxiv.org/pdf/1704.04861.pdf

[3] Hotchips HC30, Session 8: Song Yao, https://www.hotchips.org/archives/2010s/hc30/

[4] »The Lottery Ticket Hypothesis«: Frankle & Carbin, 2019, https://arxiv.org/pdf/1803.03635.pdf

[5] AI’s Energy Problem (and what we have done about it) – Part 2, https://forums.xilinx.com/t5/AI-and-Machine-Learning-Blog/AI-s-Energy-Problem-and-what-we-have-done-about-it-Part-2/ba-p/1037428

[6] ZCU104, https://www.xilinx.com/products/boards-and-kits/zcu104.html

[7] Vitis AI auf Github, https://github.com/Xilinx/Vitis-AI/blob/master/DPU-TRD/prj/Vitis/README.md

Der Autor

Quenton Hall

ist KI-Systemarchitekt für Industrial, Vision, Healthcare and Sciences bei Xilinx.