Gehäuse für Leistungshalbleiter

TO-Leadless - Leistungsgehäuse für hohe Ströme

Fortsetzung des Artikels von Teil 2

Lebensdauer und Zyklenfestigkeit

Gerade in Motor-Anwendungen ist das Thema „Lebensdauer“ sehr wichtig. Bei der Entwicklung von elektronischen Bauelementen werden deshalb eine Reihe von Tests durchgeführt, um die Zuverlässigkeit zu überprüfen. Temperaturen spielen dabei die größte Rolle. Jedoch sind es im Allgemeinen nicht die absoluten Temperaturwerte, die den größten Bauteilstress verursachen, sondern Temperaturwechsel. Dies ist dadurch erklärbar, dass ein typischer Leistungshalbleiter aus verschiedenen Materialien zusammengesetzt ist, die natürlich auch unterschiedliche thermische Ausdehnungskoeffizienten haben. Als weitere Komponenten kommen noch die Lötung und die Platine hinzu.

Um Aussagen über die Lebensdauer zu bekommen, werden die Bauteile nun den unterschiedlichsten Tests unterzogen. Damit diese Tests in akzeptabler Zeit zu Ergebnissen führen und trotzdem eine Aussage über die gesamte geplante Lebensdauer (z.B. 15 Jahre) geben, werden Beschleunigungsfaktoren verwendet, z.B. Temperaturwechsel in einem Klimaschrank. Hierbei werden die zu beurteilenden Bauteile einem Temperaturwechsel von –40 bis +125 °C ausgesetzt, der MOSFET wird also durch die Umgebung aufgewärmt und abgekühlt.

Die wichtigsten Untersuchungen

Besonders hervorzuheben sind der Intermittent Operating Lifetime Test und die Automatic Optical Inspection.

Intermittent Operating Lifetime (IOL)

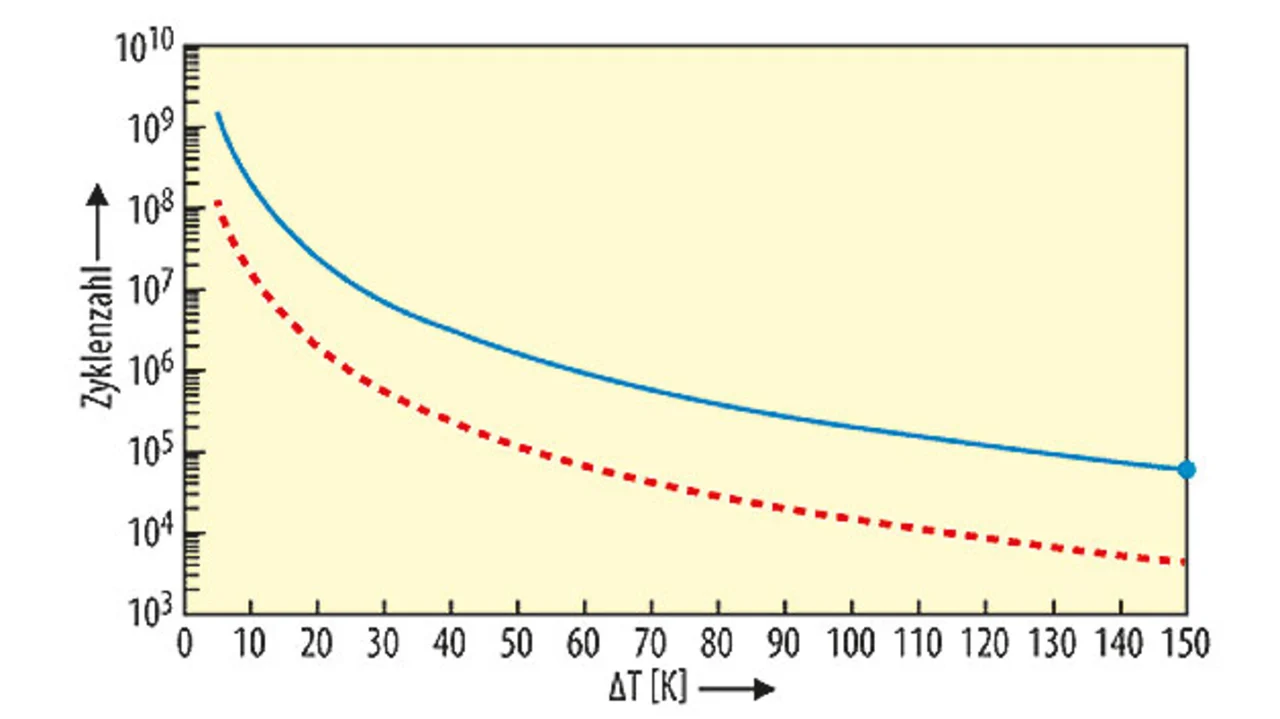

Beim sogenannten Intermittent Operating Lifetime Test, auch „Power Cycling“ genannt, wird entsprechend der Norm AEC Q101 das Bauteil über die eigene Verlustleistung in kurzer Zeit intern aufgeheizt und dann durch einfache Konvektion wieder abgekühlt. Typischerweise werden dazu recht hohe elektrische Ströme durch den Leistungshalbleiter geschickt, was den Chip in wenigen Sekunden um 100 K erwärmt. Hat laut Norm der zu testende Baustein 15.000 Zyklen ohne Zerstörung oder Drift der elektrischen Parameter überstanden, so gilt der Test als bestanden. Man erhält zwar nur einen Messpunkt (Bild 3, Messpunkt im Diagramm bei x = 100 K, y = 15.000 Zyklen), doch lässt sich eine Aussage über die Anzahl der mindestmöglichen Zyklen auch bei anderen Temperaturhüben errechnen. Daraus ergibt sich dann die Zyklenfestigkeitskurve über einen weiten Temperaturhubbereich.

Leicht ist zu erkennen, dass bereits eine kleine Erhöhung des Temperaturhubes um z.B. 20 K zu einer sehr starken Reduzierung der möglichen Zyklenzahl und somit zu einer kürzeren Lebensdauer führt.

Diese 15.000 Zyklen mit einem Temperaturhub von 100 K sind für viele Anwendungen ausreichend, doch gerade in der Antriebstechnik mit häufig wechselnden Lasten ist diese Anzahl zum Teil schon nach wenig mehr als einem oder zwei Jahren erreicht. Deshalb ist es bei Gehäusen, die eine hohe Zuverlässigkeit bieten sollen, sehr wichtig, auf eine wesentlich höhere Zyklenzahl zu testen, auch wenn die Norm dies nicht vorsieht.

Obwohl der Baustein in wenigen Sekunden aufgeheizt wird, dauert ein Messzyklus wegen der langen Abkühlungsphase länger als drei Minuten. Für die von der Norm geforderten 15.000 Zyklen benötigt man also bereits fast einen ganzen Monat. Wie oben gezeigt, ist diese Zyklenzahl in der fertigen Anwendung aber schon nach recht kurzer Zeit erreicht. Man benötigt also eine Aussage mit wesentlich mehr Temperaturhüben. Idealerweise sollte ein Leistungs-MOSFET die Forderung der Norm um ein Vielfaches übertreffen. So ein Test würde ohne weitere Beschleunigungsfaktoren mit der erwarteten Anzahl von Zyklen zu einer unakzeptablen Prüfdauer führen; für diesen speziellen Test wurde deshalb der Temperaturstress noch einmal deutlich erhöht.

Jobangebote+ passend zum Thema

Anstelle von 100 K Temperaturerhöhung wurde der Leistungs-MOSFET im TO-Leadless-Gehäuse nun um 150 K aufgeheizt. Aus der errechneten Kurve in Bild 3 wäre eine erreichte Zyklenzahl von weniger als 5000 (anstelle der 15.000 bei ∆T = 100 K) schon ein akzeptabler Wert. Wie erwartet überstand das TO-Leadless-Gehäuse aber eine wesentlich höhere Anzahl von Temperaturhüben. Selbst nach 60.000 Zyklen war keine erkennbare Drift der elektrischen Parameter erkennbar (Bild 4). Dies ist an sich schon ein sehr gutes Ergebnis. Umgerechnet auf den von der Norm geforderten Temperaturhub von ∆T = 100 K ergibt sich nun eine zu erwartende Zyklenfestigkeit von 200.000, also mehr als das 13fache der Forderung aus der Norm.

Automatic Optical Inspection der Lötverbindung

Die Zuverlässigkeit eines Leistungshalbleiters hängt natürlich nicht nur vom Bauteil selbst ab, sondern auch von der Lötung auf der Platine. Bekanntermaßen können beim Lötvorgang viele Einflüsse das Ergebnis verschlechtern und eine unzuverlässige Verbindung zur Platine ist die Folge. Elektrisch macht sich dies vielleicht am Anfang nicht bemerkbar, doch kann die Baugruppe auch wegen einer nicht perfekten Lötverbindung bereits nach kurzer Zeit ausfallen.

Eine Beurteilung der Lötqualität ist deshalb sehr wichtig. Dies ist bei Leistungshalbleitern wie dem D²PAK sehr einfach; es wird nur die beim Bestücker im Allgemeinen vorhandene Automatic Optical Inspection (AOI) benötigt. Dies ist ein sehr preisgünstiger Test zur Beurteilung der Lötqualität. Anders sieht es meist bei Bauteilen ohne (externe) Anschlussdrähte aus. Grund dafür ist, dass die Lötanschlüsse entweder komplett unter dem Bauteil sind wie einem BGA oder dass nur die blanken Kupfer-Schnittflächen nach dem Vereinzeln zu sehen sind. Dann bleibt keine andere Möglichkeit als die recht teure und nicht immer verfügbare Röntgenkontrolle zur Beurteilung der Lötung.

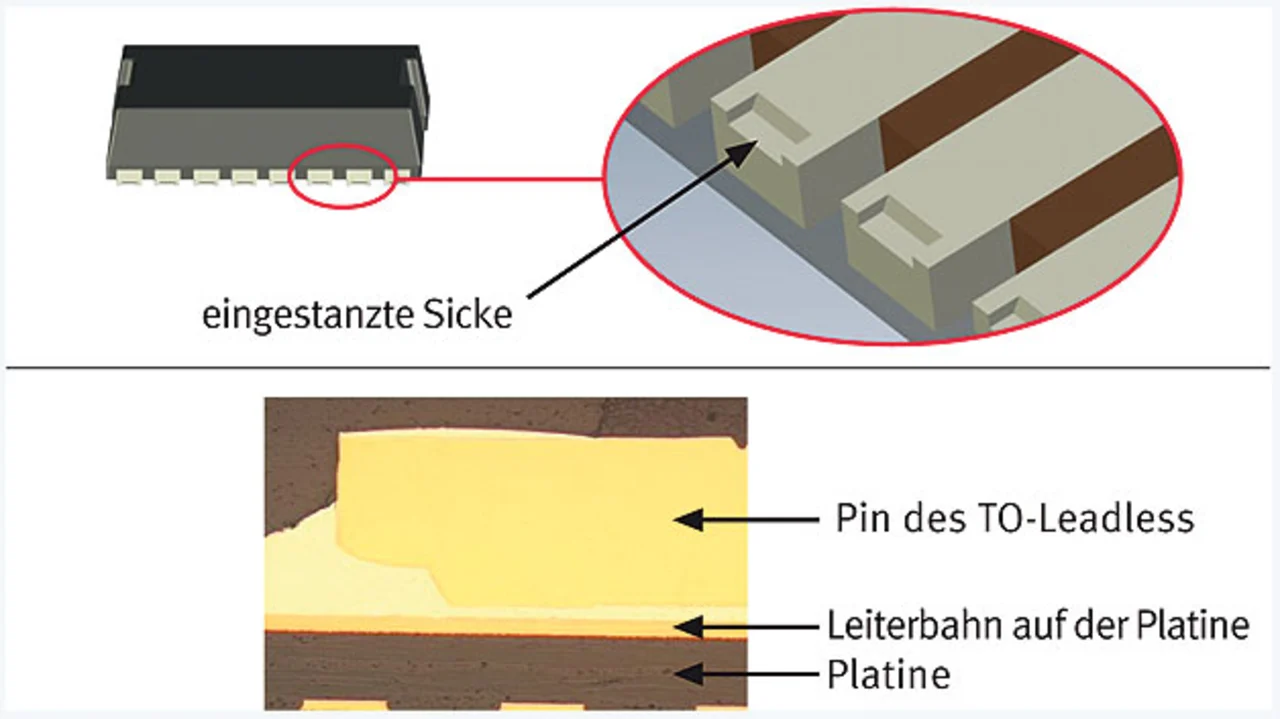

Obwohl es sich beim TO-Leadless um ein Gehäuse ohne weit herausragende Anschlüsse handelt, ist die Lötqualität durch den ganz normalen AOI beurteilbar. Realisiert wurde dies durch ein elegantes Detail: Dort, wo im letzten Arbeitsschritt das Bauteil aus dem Träger-Leadframe herausgeschnitten wird, wird vor der Oberflächenbehandlung (Verzinnen, „Plating“) eine kleine Sicke eingestanzt. Wird nun der Baustein vereinzelt, dann entstehen zwar auch an der Anschlussvorderseite die blanken Kupferflächen, doch bildet sich aufgrund der vorher verzinnten Sicke bei einem erfolgreichen Lötvorgang ein ganz normaler Lötmeniskus aus und dieser ist sehr zuverlässig beurteilbar.

Bild 5 zeigt schematisch die Ansicht auf die Gate- und Source-Anschlüsse. In der dreidimensionalen und gedrehten Ansicht ist die blanke (Kupfer-) Schnittfläche sehr gut zu sehen und ebenfalls die verzinnte Sicke. Das Lötergebnis ist auf dem stark vergrößerten Schnittbild rechts (oben) zu erkennen. Hell ist das Lot, Dunkel der Source-Anschlusspin mit der eingeprägten Sicke. Am linken Bildrand sieht man den Beginn des auch außen sichtbaren Lötmeniskus.

Thermisches Management erleichtert

Durch die Entwicklung des TO-Leadless-Gehäuses konnten die Anforderungen für Anwendungen mit hohen Strömen sowie die maximalen Ansprüche an die Zuverlässigkeit umgesetzt werden. Der niedrige Gehäusewiderstand verringert die Verluste erheblich und erleichtert das thermische Management. Zusätzlich verringert die Möglichkeit zur optischen Kontrolle die Kosten und erlaubt eine zuverlässige Beurteilung der Lötverbindung. Das Ergebnis ist ein Leistungsgehäuse, das auf kleinem Raum eine hohe Stromdichte erlaubt, ohne dass die Zuverlässigkeit der Baugruppe beeinträchtigt wird.

Der Autor

| Ralf Walter |

|---|

| hat in Aachen Elektrotechnik studiert und entwickelte viele Jahre lang Leistungselektroniken. Bei Infineon ist er als Applikations-Ingenieur tätig. |

- TO-Leadless - Leistungsgehäuse für hohe Ströme

- Kriterien bei der Gehäusewahl

- Lebensdauer und Zyklenfestigkeit