Siliziumkarbid

SiC-MOSFETs parallelisieren

Fortsetzung des Artikels von Teil 1

Experimentelle Verifikation

Vor dem Test galt es zunächst, das Messverfahren des Kanalstroms zu bestimmen. Da sich dieser Strom nicht direkt messen lässt, ist er durch den Source-Strom iS oder den Drain-Strom iD anzunähern (siehe Bild 1). Üblicherweise wird der Source-Strom genommen, da er auf Masse bezogen und deshalb leichter zu messen ist. Allerdings fließt ein erheblicher Teil des Ungleichgewichts der Kanalströme durch die recht kleine Treiber-Source-Impedanz Rk, denn die gesuchte Differenz der Kanalströme ist die Summe von ΔiS und Δik. Daher wurden in diesem Fall die Drain-Ströme gemessen. Die Differenz der Kanalströme lässt sich unter Berücksichtigung vernachlässigbarer Verschiebungsströme durch die parasitären Kapazitäten CDS und CGD genau detektieren. Die Split-Core-Stromsonde TCP0030A von Tektronix mit einem Messbereich bis 30 A und Bandbreite von 120 MHz wurde im Experiment verwendet.

Jobangebote+ passend zum Thema

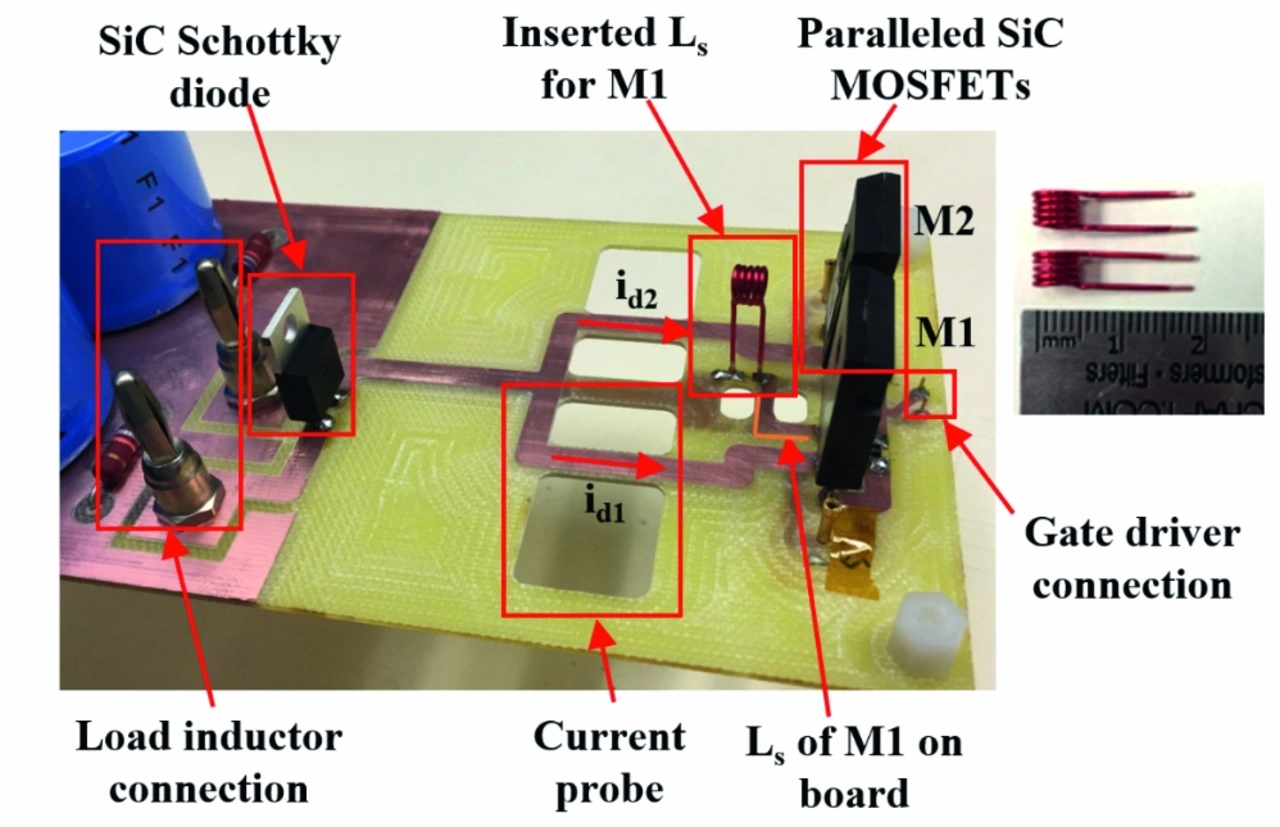

Bild 4 zeigt die Hardware für den Doppelpulstester zur experimentellen Verifikation des Ausgleichseffekts von LS und Rk. Zwei diskrete SiC-MOSFETs vom Typ C2M0160120D (1200 V/19 A) von Wolfspeed mit unterschiedlichen Schwellenspannungen (Uth1 = 2,34 V, Uth2 = 2,78 V; gemessen) wurden in einem symmetrischen Layout parallel geschaltet. Die High-Side bestand aus einer SiC-Schottky-Diode vom Typ C4D20120A (1200 V/26 A) ebenfalls von Wolfspeed. Die Gate-Treiberplatine CRD-001 wurde über den Stecker auf der Platine angeschlossen.

Ein kleines Lk (1,89 nH basierend auf einer Q3D-Simulation von Ansys) aus dem Leiterplatten-Layout begrenzte den anfänglichen Balancing-Effekt. Die Treiber-Source-Impedanz wurde von Rk dominiert. Die Induktivität der »heißen Schleife« war relativ groß – etwa 120 nH von Leiterbahnen und ESLs der Zwischenkreiskondensatoren –, weil dort die Stromsonden platziert werden mussten. Die Drain-Induktivität betrug circa 26 nH. Daher war das Einschwingen während des Einschaltvorgangs schwerwiegend [9,11]. Diese parasitären Effekte wurden absichtlich nicht reduziert, um die Leistungsfähigkeit der Designrichtlinie trotz schlechten Layouts zu überprüfen.

Die gleiche Platine wurde verwendet, um einen fairen Vergleich von Basisentwurf und finalem Entwurf zu gewährleisten. Die einzige Unterschiede waren die Source-Impedanzen LS und Rk. Öffnungen auf den entsprechenden Leiterbahnen wurden vorbereitet, um dort zusätzliche Spulen oder Widerstände einzusetzen. Für den Basisentwurf wurden für Rk 0-Ω-Widerstände aufgelötet, um die Öffnungen kurzzuschließen.

Zur Überprüfung des passiven Ausgleichseffektes wurden kleine Luftspulen und SMD-Widerstände mit verschiedenen Werten eingefügt. Zwei Luftspulen mit der gleichen Induktivität erhöhten die Power-Source-Induktivität LS (Bild 4). Eine wurde auf der Oberseite der Platine platziert, die andere auf der Unterseite und durch die Platine blockiert. Die Treiber-Source-Widerstände Rk wurden durch SMD-Widerstände variiert, die sich ebenfalls auf der Unterseite der Platine befanden.

Der Doppelpulstest selbst besteht aus zwei kurzen Impulsen. Die Schalttransienten werden bei den ersten fallenden und steigenden Flankten bei Raumtemperatur erfasst (mit vernachlässigbarer Änderung der Sperrschichttemperaturen der Bauteile). Tabelle 1 stellt die jeweils eingesetzten Werte von LS – aus der Q3D-Simulation erhalten – und RS gegenüber.

| Parameter | Basisentwurf | finaler Entwurf |

|---|---|---|

| LS / nH | 11,5 | 47,2 |

| Rk / Ω | 0 | 5,6 |

Tabelle 1: Werte für LS und Rk, die für die Tests in Bild 5 verwendet wurden.

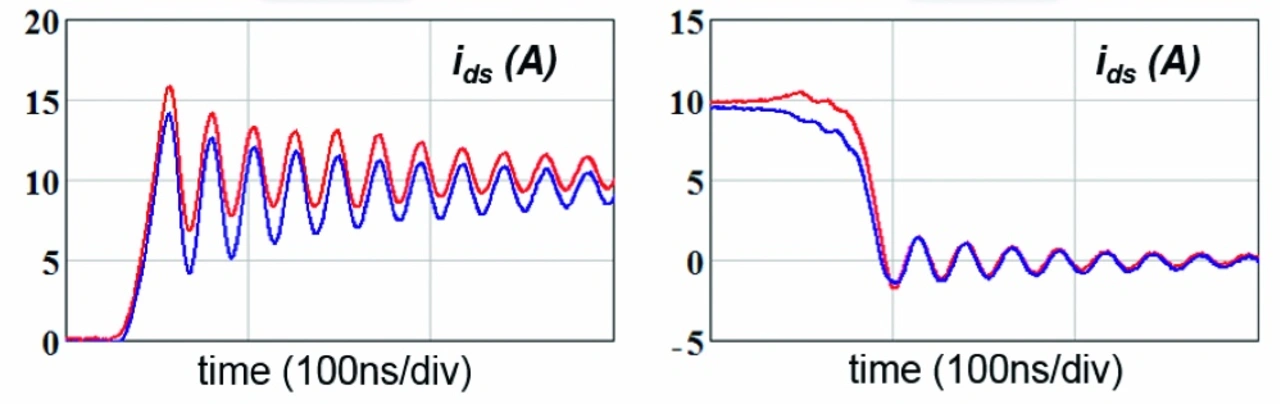

Die experimentellen Ergebnisse des Basisentwurfs zeigt Bild 5a. Das Ungleichgewicht bei der Stromaufteilung ist offensichtlich. Die Stromanstiegszeit tr beträgt 35 ns. Dann wurden LS und Rk so dimensioniert, dass die Stromaufteilung besser ist. Dadurch ließ sich auf der Grundlage obiger Designrichtlinie die Differenz der Spitzenströme unter 5 % des halben Eingangsstroms Iin (0,5 A) begrenzen:

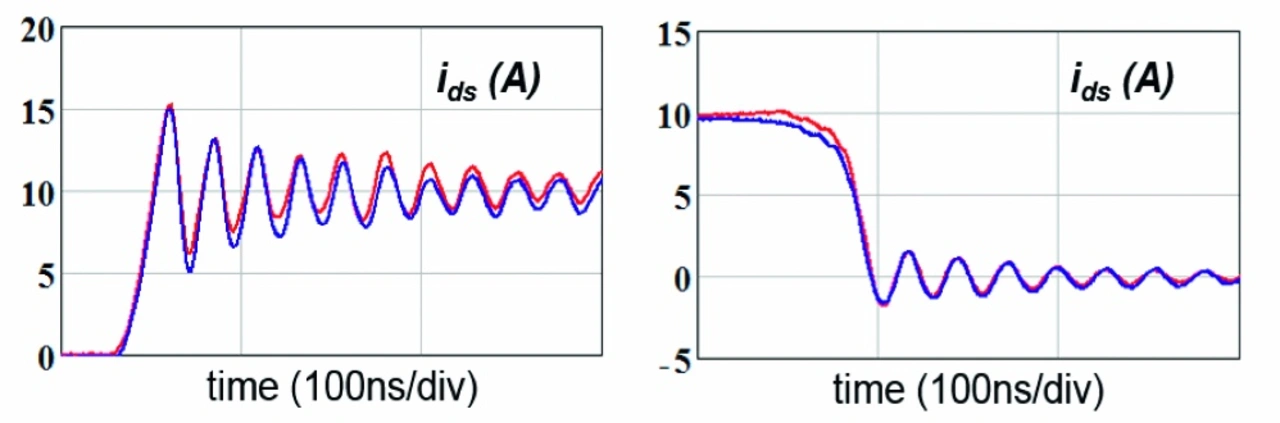

Bild 5b zeigt die Versuchsergebnisse mit angepassten Werten für LS und Rk. Die gewünschte Stromaufteilung wird innerhalb eines Schaltzyklus erreicht, auch wenn nur ein einzelner Gate-Treiber verwendet wird. Selbst bei der Abschaltflanke teilt sich der Strom gleichmäßiger auf, verglichen mit dem in Bild 5a dargestellten Basisentwurf. Andere Kombinationen von Rk und LS, welche die Designrichtlinie erfüllen, sollten auch den Strom effektiv aufteilen können (siehe Bild 3a).

Tabelle 2 fasst den Vergleich zwischen Basisentwurf und finaler Lösung zusammen. Die gemessene Differenz der Spitzenströme sinkt von 1,5 A auf 0,1 A (unter 5 Prozent des stationären Stroms), ohne die Gesamtschaltverluste zu erhöhen. Die Designrichtlinie ist damit verifiziert. Das Überschwingen verschlechtert sich durch das erhöhte LS unter den Testbedingungen nicht. Der Prototyp in Bild 4 zeigt relativ große Störeffekte, weil die Stromsonden unterzubringen waren. In der praktischen Umsetzung benötigt die Lösung aus Bild 1 jedoch keinen Sensor. Die parasitäre Induktivität entlang der Kommutierungsschleife des Stroms kann nach Eliminieren der Stromsonde und/oder der Hinzunahme eines Entkopplungskondensators klein gehalten werden.

| Parameter | Basisentwurf | finaler Entwurf |

|---|---|---|

| LS / nH | 11,5 | 47,2 |

| Rk / Ω | 0 | 5,6 |

Tabelle 2: Vergleich zwischen Basisentwurf (Bild 5a) und finalem Entwurf (Bild 5b) bei einem stationärem Strom von 10 A.

Diese erarbeitete Lösung eignet sich auch für das Parallelschalten von mehr als zwei MOSFETs, da sie die Asymmetrie der Schwellenspannungen nicht berücksichtigen muss und nur einen Gate-Treiber verwendet. Verfahren, um Rk und LS zu reduzieren – etwa durch magnetische Kopplung –, sind Gegenstand zukünftiger Untersuchungen.

Referenzen

[1] J. Richmond, M. Das, S. Leslie, A. Agarwal, B. Hull und J. Palmour, »Roadmap for megawatt class power switch modules utilizing large area silicon carbide MOSFETs and JBS diodes«, Energy Conversion Congress and Exposition, 2009. ECCE 2009. IEEE, San Jose, CA, 2009, pp. 106-111.

[2] W. Gangyao, J. Mookken, J. Rice und M. Schupbach, »Dynamic and static behavior of packaged silicon carbide MOSFETs in paralleled applications«, APEC 2014, Twenty-Ninth Annual IEEE, Fort Worth, TX, 2014, pp. 1478-1483.

[3] Y. Xue, J. Lu, Z. Wang, L. M. Tolbert, B. J. Blalock und F. Wang, »Active current balancing for parallel-connected silicon carbide MOSFETs«, ECCE 2013 IEEE, Denver, CO, 2013, pp. 1563-1569.

[4] J. Hu, O. Alatise, J. A. O. González, R. Bonyadi, L. Ran und P. A. Mawby, »The Effect of Electrothermal Nonuniformities on Parallel Connected SiC Power Devices Under Unclamped and Clamped Inductive Switching«, in IEEE Trans. on Power Electronics, vol. 31, no. 6, pp. 4526-4535, June 2016.

[5] D. Bortis, J. Biela und J. W. Kolar, »Active Gate Control for Current Balancing of Parallel-Connected IGBT Modules in Solid-State Modulators«, in IEEE Trans. on Plasma Sci., vol. 36, no. 5, pp. 2632-2637, Oct. 2008.

[6] M. Sasaki, H. Nishio und W. T. Ng, »Dynamic gate resistance control for current balancing in parallel connected IGBTs«, APEC 2013, Twenty-Eighth Annual IEEE, Long Beach, CA, USA, 2013, pp. 244-249.

[7] R. Alvarez und S. Bernet, »A new delay time compensation principle for parallel connected IGBTs«, ECCE 2011 IEEE, Phoenix, AZ, 2011, pp. 3000-3007.

[8] Helong Li et al., »Influences of Device and Circuit Mismatches on Paralleling Silicon Carbide MOSFETs«, in IEEE Trans. on Power Electron., vol. 31, no. 1, pp. 621-634, Jan. 2016.

[9] J. Wang, H. S. h. Chung und R. T. h. Li, »Characterization and Experimental Assessment of the Effects of Parasitic Elements on the MOSFET Switching Performance«, in IEEE Transactions on Power Electronics, vol. 28, no. 1, pp. 573-590, Jan. 2013.

[10] J. Wang und H. Shu-Hung Chung, »Impact of Parasitic Elements on the Spurious Triggering Pulse in Synchronous Buck Converter«, in IEEE Transactions on Power Electronics, vol. 29, no. 12, pp. 6672-6685, Dec. 2014.

[11] Z. Chen, D. Boroyevich und R. Burgos, »Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics«, International Power Electronics Conference (IPEC) 2010, Sapporo, pp. 164-169.

- SiC-MOSFETs parallelisieren

- Experimentelle Verifikation