Treiber für GaN-Transistoren

Optimierte Performance

Fortsetzung des Artikels von Teil 2

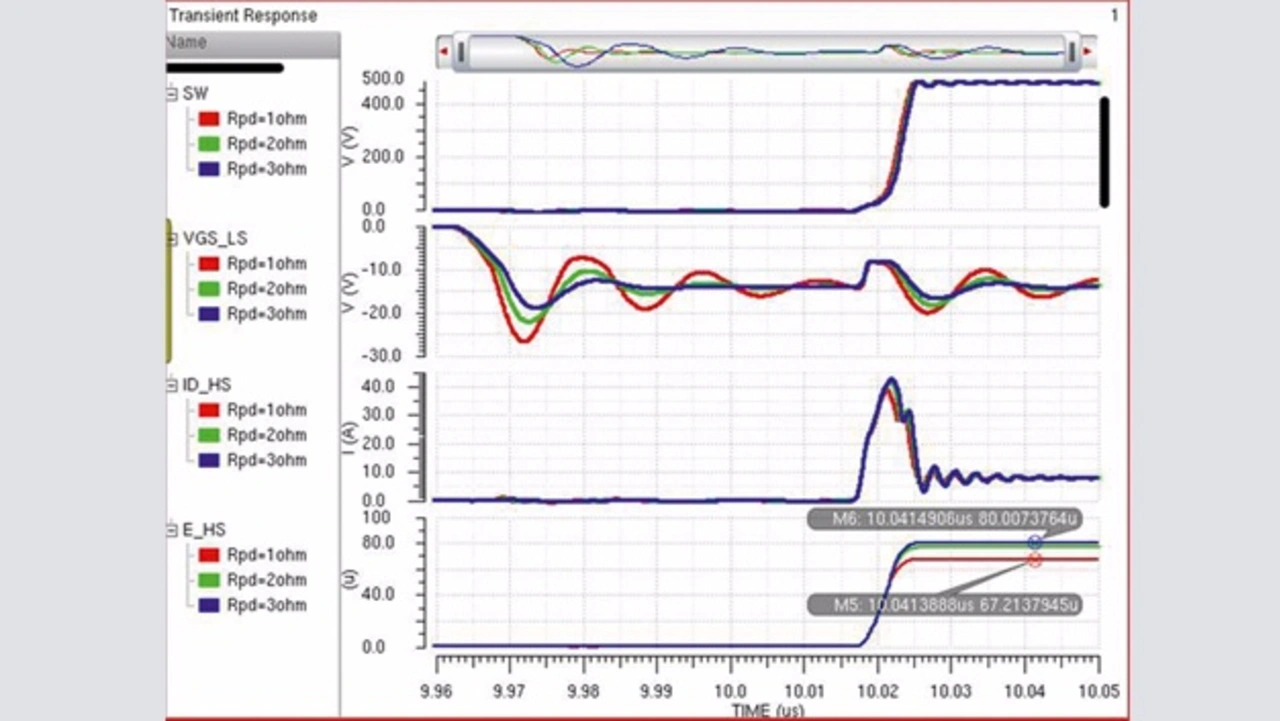

Schutzfunktionen für den GaN-HEMT

Eine Möglichkeit, die starke Belastung des Gates zu senken, besteht darin, den Wert des Pull-down-Widerstands zu vergrößern, was gemäß Gleichung (1) die Güte des LRC-Schwingkreises verringert. Bild 5 zeigt Simulationen mit einer Gate-Stromkreises-Induktivität von 10 nH und einem von 1 Ω bis 3 Ω variierten Pull-down-Widerstand. Bei einem Wert von 3 Ω wird zwar das Unterschwingen am Gate auf wenige Volt unterhalb der negativen Bias-Spannung begrenzt, aber dafür verschlechtert sich die Hold-off-Fähigkeit mit dem Resultat eines höheren Shoot-through-Stroms (erkennbar an den Kurven zum Drain-Strom). Die E_HS-Kurven lassen einen zusätzlichen Verlust von 13 µJ pro Schaltzyklus erkennen, was eine Zunahme um fast 60 % gegenüber den 53 µJ bedeutet, die bei einer Gate-Stromkreis-Induktivität von 2 nH und einem Pull-down-Widerstand von 1 Ω entstehen (Bild 4).

Legt man 100 kHz Schaltfrequenz zugrunde, so erhöht sich die Verlustleistung im High-Side-Baustein von 5,3 W auf 8 W. Ursache hierfür ist der Shoot-through-Strom, hervorgerufen durch die hohe Induktivität des Gate-Stromkreises und den hohen Pull-down-Widerstand. Diese zusätzliche Verlustleistung kann es sehr schwierig machen, die Wärmeentwicklung in den Leistungsbausteinen zu beherrschen. Zusätzlich steigt der Kostenaufwand für Gehäuse und Entwärmung.

Es ist möglich, eine negativere Spannung an das Gate zu legen, jedoch erhöht dies die Belastung des Gates und die Totzeitverluste. Bei einer hohen Gate-Stromkreis-Induktivität ist es deshalb sehr schwierig, die richtige Balance zwischen Gate-Belastung und Hold-off-Fähigkeit zu halten. Man kann entweder die Belastung des Gates erhöhen oder Shoot-through-Ströme der Halbbrücke in Kauf nehmen, was die Cross-Conduction-Verluste und die Oszillationen in der Leistungsschleife ansteigen lässt und Probleme hinsichtlich des sicheren Arbeitsbereichs hervorrufen kann (SOA, Safe Operating Area). Eine integrierte Kombination aus GaN-FET und Treiber zeichnet sich durch eine geringe Gate-Stromkreis-Induktivität aus und minimiert dadurch sowohl die Gate-Belastung als auch das Shoot-through-Risiko.

Schutzfunktionen für den GaN-FET

Befinden sich Treiber und GaN-Transistor auf ein und demselben Leadframe, so unterscheiden sich ihre Temperaturen nur wenig, da der Leadframe Wärme hervorragend leitet. In den Treiber können ein Temperatursensor und ein Überhitzungsschutz eingebaut werden, um den GaN-FET abzuschalten, sobald die gemessene Temperatur einen bestimmten Grenzwert überschreitet.

Ein Überstromschutz lässt sich mit einem Serien-MOSFET oder einem parallelgeschalteten Mess-GaN-FET realisieren. Beide setzen voraus, dass die Verbindungen zwischen dem GaN-Baustein und seinem Treiber von geringer Induktivität sind. Da GaN-Transistoren in der Regel sehr schnell und mit einem hohen di/dt geschaltet werden, können zusätzliche Induktivitäten in diesen Verbindungen zu Oszillationen führen. Außerdem erfordern sie eine lange Austastzeit (Blanking Time), um fehlerhaftes Ansprechen des Überstromschutzes zu verhindern. Die Integration des Treibers gewährleistet, dass die Verbindungen zwischen der Messschaltung und dem GaN-FET von minimaler Induktivität sind, sodass der Überstromschutz möglichst schnell reagieren und den Baustein vor Belastungen durch zu hohe Ströme schützen kann.

Jobangebote+ passend zum Thema

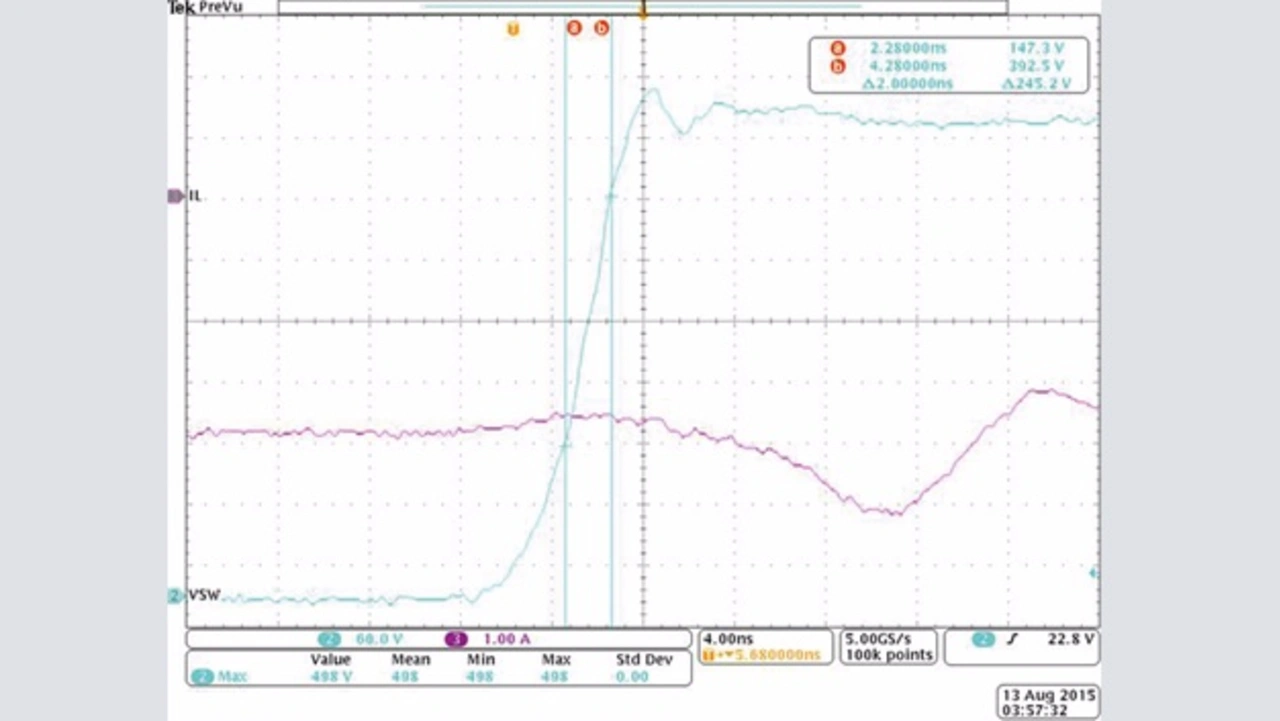

Bild 6 zeigt das Oszillogramm, das beim Schalten einer Halbbrücke aus zwei GaN-Bausteinen in einem 8 mm x 8 mm großen QFN-Gehäuse mit integriertem Treiber aufgezeichnet wurde. Kanal 2 zeigt den Schaltknoten, wenn der high-seitige Baustein mit einer Anstiegsgeschwindigkeit von 120 V/ns und einer Busspannung von 480 V hart geschaltet wird. Durch das optimierte Gehäuse mit integriertem Treiber und das Leiterplatten-Layout wird das Überschwingen auf weniger als 50 V begrenzt. Die Kurve wurde mit einem 1-GHz-Oszilloskop und entsprechenden Tastköpfen aufgezeichnet.

Zusammenfassung

Die Integration von GaN-Transistor und Treiber in einem gemeinsamen Gehäuse eliminiert Common-Source-Induktivitäten und erlaubt so höhere Anstiegsgeschwindigkeiten. Darüber hinaus verringert sich die Induktivität des Gate-Stromkreises, was die Gate-Belastung beim Abschalten verringert und die Hold-off-Fähigkeit des Bausteins verbessert. Nicht zuletzt erlaubt diese Integration, effektive Übertemperatur- und Überstrom-Schutzfunktionen für GaN-FETs einzubauen.

| Weiterführende Links: |

|---|

Michael Seeman und Dave Freeman: »Advancing power supply solutions through the promise of GaN«, Texas Instruments White Paper, Februar 2015; www.ti.com/lit/sszy017 Sandeep R. Bahl: »A comprehensive methodology to qualify the reliability of GaN products«, Texas Instruments White Paper, März 2015, www.ti.com/lit/SLYY070 Narendra Mehta: »GaN FET module performance advantage over silicon«, Texas Instruments White Paper, März 2015, www.ti.com/lit/slyy071 Zhong Ye: »GaN FET-Based CCM Totem-Pole Bridgeless PFC«, Texas Instruments Power Supply Design Seminar, 2014; www.ti.com/lit/pdf/slup327 Zusätzliche Informationen über GaN: www.ti.com/gan Kostenloses Softwaretool TINA-TI: www.ti.com/tina-ti |

- Optimierte Performance

- Einfluss der Common-Source-Induktivität

- Schutzfunktionen für den GaN-HEMT