Treiber für GaN-Transistoren

Optimierte Performance

Fortsetzung des Artikels von Teil 1

Einfluss der Common-Source-Induktivität

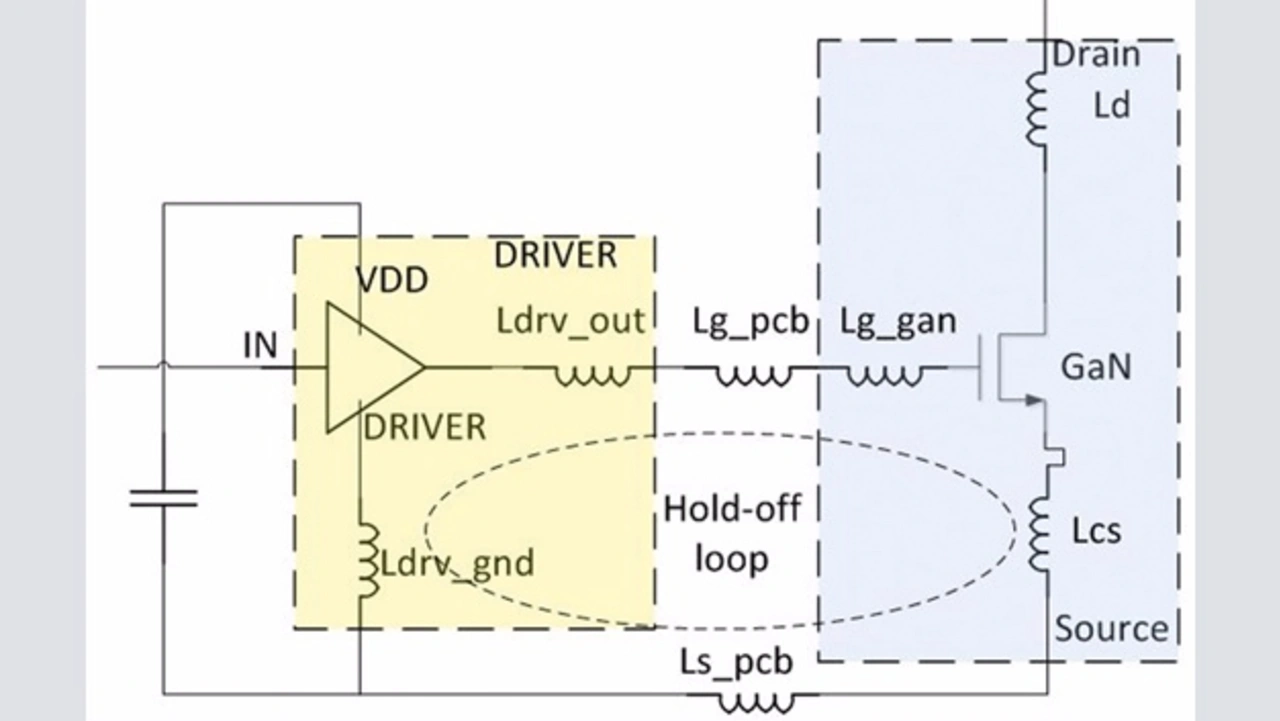

Zu den entscheidendsten parasitären Elementen bei hohen Schaltgeschwindigkeiten gehört die Common-Source-Induktivität (LCS in Bild 1aa), welche die Anstiegsgeschwindigkeit des Drain-Stroms begrenzt. In einem konventionellen Gehäuse der Bauart TO-220 wird die Source des GaN-Bausteins über Bonddrähte an einen einzelnen Anschluss herausgeführt, über den sowohl der Drain- und Gate-Strom fließen. Die Common-Source-Induktivität moduliert somit die Gate-Source-Spannung, wenn sich der Drain-Strom ändert. Diese parasitäre Induktivität setzt sich aus der Induktivität des Bonddrahts und des herausgeführten Anschlusses zusammen und kann mehr als 10 nH betragen, wodurch sie die Anstiegsgeschwindigkeit limitiert und die Schaltverluste ansteigen lässt.

Jobangebote+ passend zum Thema

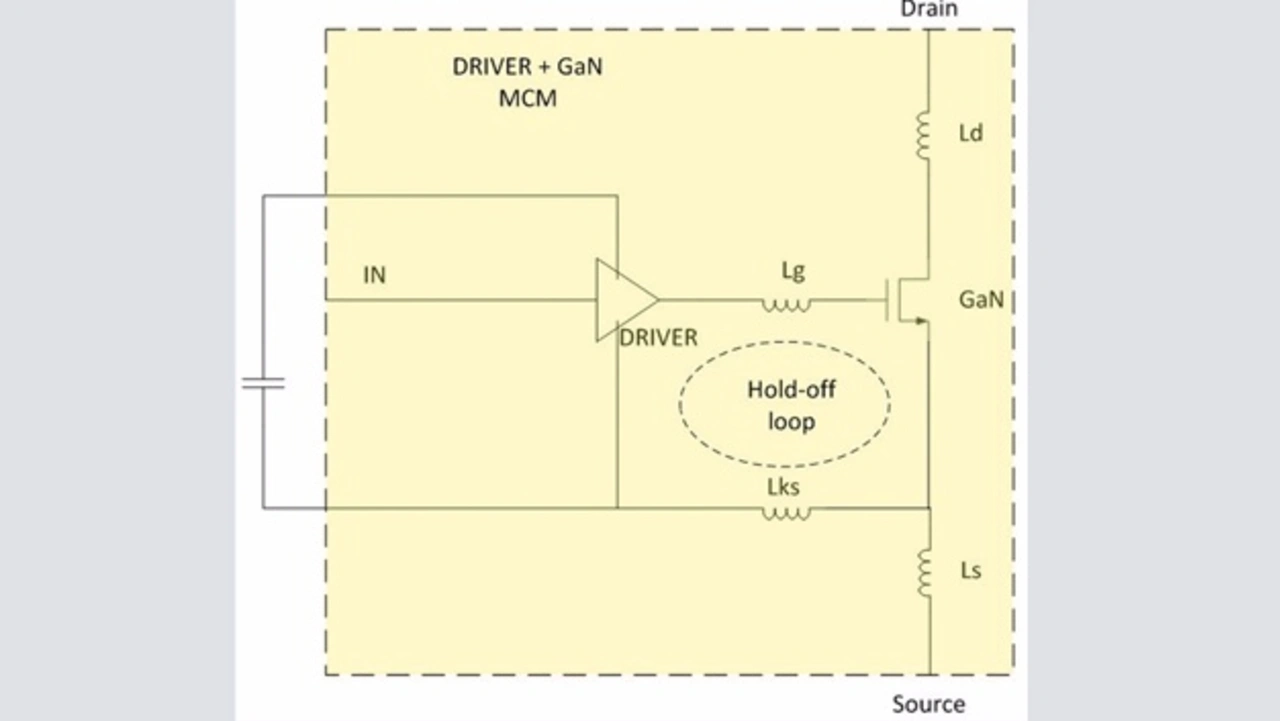

Bei dem in Bild 1bb gezeigten integrierten Gehäuse ist die Masse des Treibers per Bonddraht direkt mit dem Source-Pad des GaN-Chips verbunden. Diese Kelvin-Verbindung minimiert die Common-Source-Induktivität auf dem gemeinsamen Strompfad des Leistungs- und des Gate-Kreises, wodurch dieser Baustein ein wesentlich höheres di/dt erreichen kann. Selbstverständlich kann ein Kelvin-Source-Anschluss auch zu einem diskreten Gehäuse hinzugefügt werden. Dieses wird dadurch jedoch zu einem vom Standard abweichenden Gehäuse und außerdem muss man auf der Leiterplatte eine Leiterbahn vom Kelvin-Source-Anschluss zurück zum Treibergehäuse verlegen, was wiederum die Induktivität des Gate-Stromkreises erhöht.

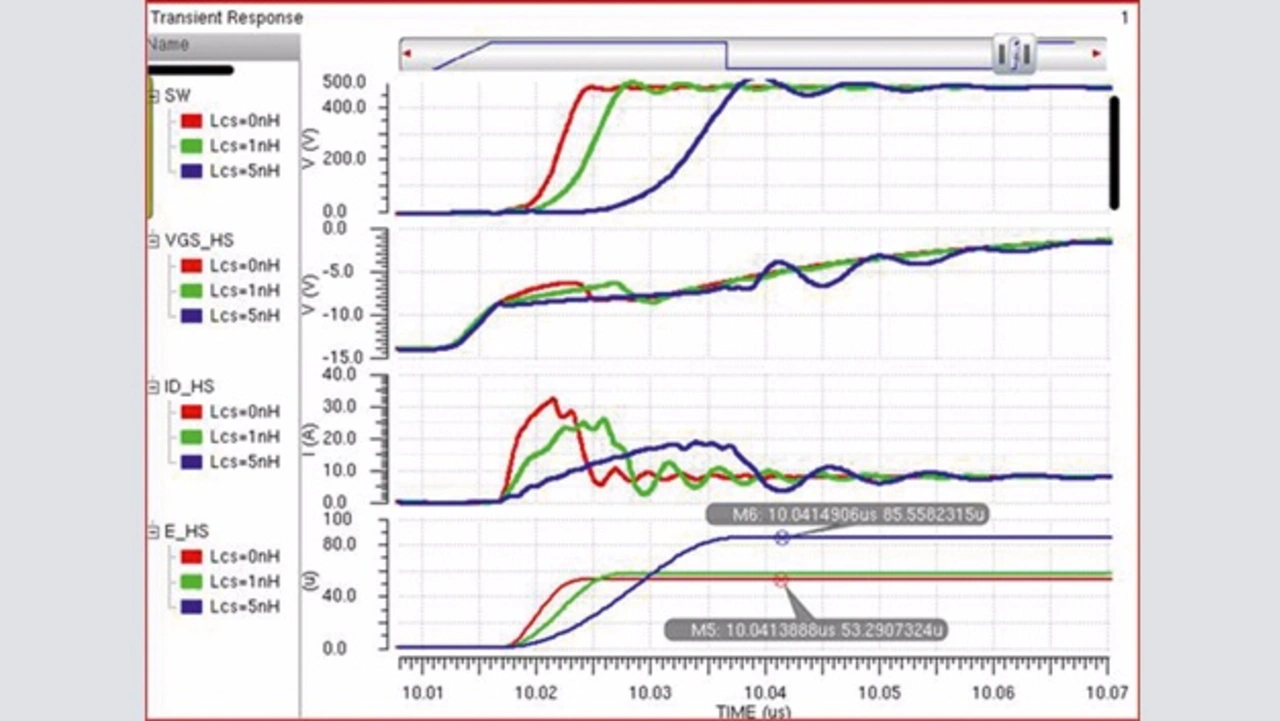

Bild 3 zeigt die aufgezeichneten Kurven für das harte Einschalten des High-Side-Schalters. Bei einer Common-Source-Induktivität von 5 nH (blaue Kurven) halbiert sich die Anstiegsgeschwindigkeit infolge der Source-Gegenkopplung. Eine niedrigere Anstiegsgeschwindigkeit aber führt zu längeren Übergangszeiten und höheren Cross-Conduction-Verlusten, wie an den Energiebedarfskurven (Bild 3, unten) deutlich wird. Bei einer Common-Source-Induktivität von 5 nH steigt der Energieverlust von 53 µJ um 60 % auf 85 µJ. Legt man eine Schaltfrequenz von 100 kHz zugrunde, entspricht dies einer Zunahme der Verlustleistung von 5,3 W auf 8,5 W.

Induktivität des Gate-Stromkreises

Die Induktivität des Gate-Stromkreises umfasst sowohl die Gate-Induktivität als auch die Induktivität der Treibermasse. Unter der Gate-Induktivität versteht man die Induktivität zwischen dem Treiberausgang und dem Gate des GaN-Bausteins. Bei separaten Gehäusen umfasst die Gate-Induktivität den Bonddraht des Treiberausgangs (Ldrv_out), den Bonddraht des GaN-Gates (Lg_gan) und die Leiterbahn (Lg_pcb), wie in Bild 1aa gezeigt.

Abhängig von den Abmessungen des Gehäuses kann die Gate-Induktivität zwischen einigen Nanohenry bei einem kompakten oberflächenmontierbaren Gehäuse liegen (beispielsweise QFN-Gehäuse) und mehr als 10 nH bei einem bedrahteten Leistungsgehäuse (beispielsweise Bauart TO-220). Ist der Treiber zusammen mit dem GaN-FET auf demselben Leadframe integriert (Bild 1b), ist das GaN-Gate direkt an den Treiberausgang gebondet, wodurch sich die Gate-Induktivität auf weniger als 1 nH verringern kann. Das gemeinsame Gehäuse kann darüber hinaus die Induktivität der Treibermasse entscheidend reduzieren (von Ldrv_gnd + Ls_pcb in Bild 1aa auf Lks in Bild 1bb).

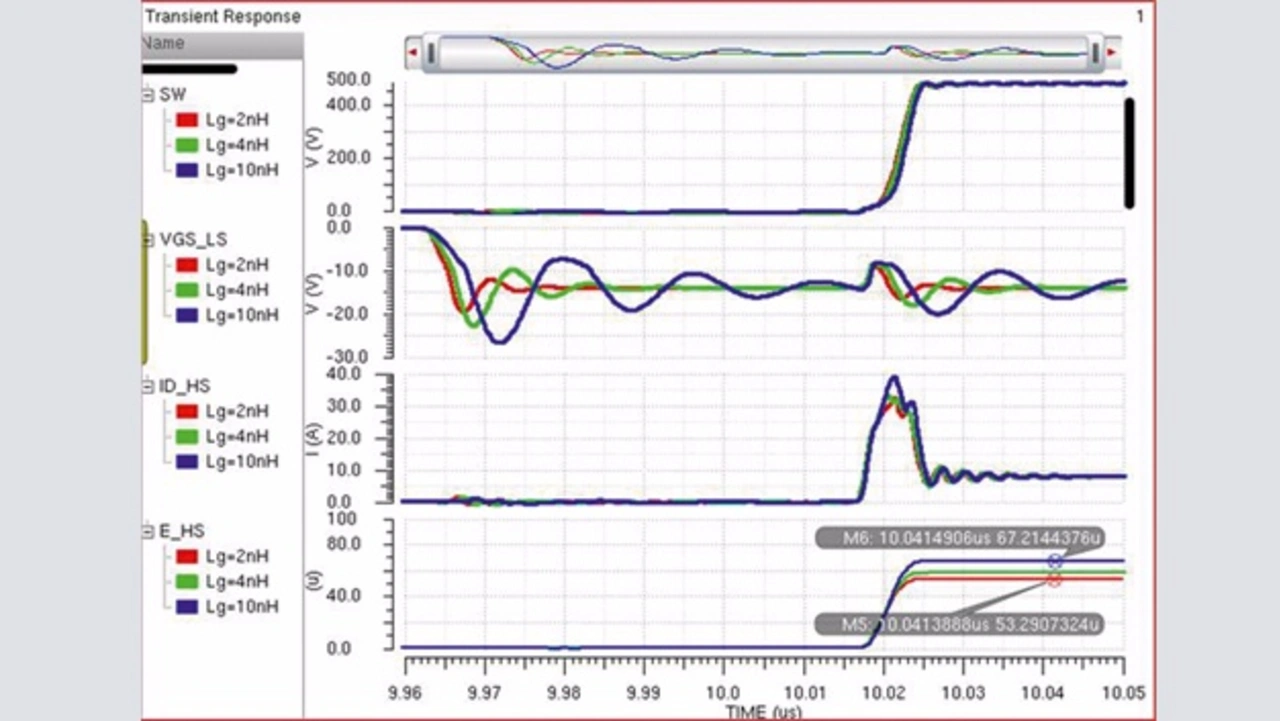

Die Induktivität des Gate-Stromkreises zu verringern wirkt sich stark auf die Schalt-Performance aus, und dies speziell beim Abschalten, wenn das Potenzial am GaN-Gate durch einen Widerstand herabgezogen wird. Der Wert dieses Widerstands muss so gering sein, dass der Baustein nicht wieder eingeschaltet wird, wenn sein Drain-Anschluss während des Schaltens auf ein hohes Potenzial gezogen wird. Zusammen mit der Gate-Source-Kapazität des GaN-Transistors und der Induktivität des Gatestromkreises bildet dieser Widerstand einen LRC-Schwingkreis, dessen Gütefaktor Q mit Gleichung (1) ausgedrückt wird:

(1)

Vergrößert sich die Induktivität des Gate-Stromkreises, nimmt dieser Gütefaktor zu und der Stromkreis neigt stärker zum Schwingen. Simulieren lässt sich dieser Effekt mit einem Pull-down-Widerstand von 1 Ω zum Abschalten des low-seitigen GaN-FET (siehe Bild 4 bei 9,97 µs). Dabei wird die Induktivität des Gate-Stromkreises zwischen 2 nH und 10 nH variiert. Bei 10 nH schwingt die low-seitige Gate-Source-Spannung UGS stark ins Negative über, sodass das Gate des GaN-Transistors stark belastet wird. Bekanntermaßen führt eine solche Überlastung bei FETs jeglicher Art zu Zuverlässigkeitsproblemen.

Die Induktivität des Gate-Stromkreises wirkt außerdem erheblich auf die Fähigkeit ein, den ausgeschalteten low-seitigen GaN-FET nicht durch induzierte Ströme wieder einzuschalten (Hold off). Wenn das Gate des low-seitigen Transistors auf der Abschaltspannung gehalten wird und der high-seitige Baustein einschaltet, lässt die Drain-Gate-Kapazität des low-seitigen Bausteins einen hohen Strom in das Gate des low-seitigen FETs fließen. Dieser Strom bewirkt, dass infolge der Induktivität des Gate-Stromkreises das Potenzial am Gate ansteigt. Bild 4 veranschaulicht dieses Phänomen bei etwa 10,02 µs. Wenn die Induktivität zunimmt, steigt die UGS des low-seitigen Bausteins immer weiter an, wodurch sich der Shoot-through-Strom erhöht (erkennbar ist dies an den Kurven zum high-seitigen Drain-Strom). Dieser Shoot-through-Effekt wiederum bewirkt, dass der Cross-Conduction-Energieverlust (E_HS) von 53 µJ auf 67 µJ ansteigt.

- Optimierte Performance

- Einfluss der Common-Source-Induktivität

- Schutzfunktionen für den GaN-HEMT