Treiber für GaN-Transistoren

Optimierte Performance

GaN-Transistoren schalten deutlich schneller als Silizium-MOSFETs. Sie verheißen geringere Schaltverluste, allerdings können bestimmte Gehäusebauarten die Performance bei hohen Anstiegsgeschwindigkeiten einschränken. Die parasitären Induktivitäten müssen minimiert werden.

von Yong Xie, IC Design Engineer, und Paul Brohlin, Design and System Manager, beide GaN and Next Team, High-Voltage Power Solutions von Texas Instruments.

Transistoren auf der Basis von Galliumnitrid (GaN) sind in ihrer Schaltleistung den Silizium-MOSFETs überlegen, da sie bei gleichem Einschaltwiderstand eine niedrigere Sperrschichtkapazität aufweisen und keine Body-Diode haben, was die daraus resultierenden Sperrverzögerungsverluste eliminiert. Wegen dieser Eigenschaften können GaN-FETs mit höheren Frequenzen schalten, was unter Beibehaltung angemessener Schaltverluste eine höhere Leistungsdichte und ein besseres Einschwingverhalten bewirkt.

Jobangebote+ passend zum Thema

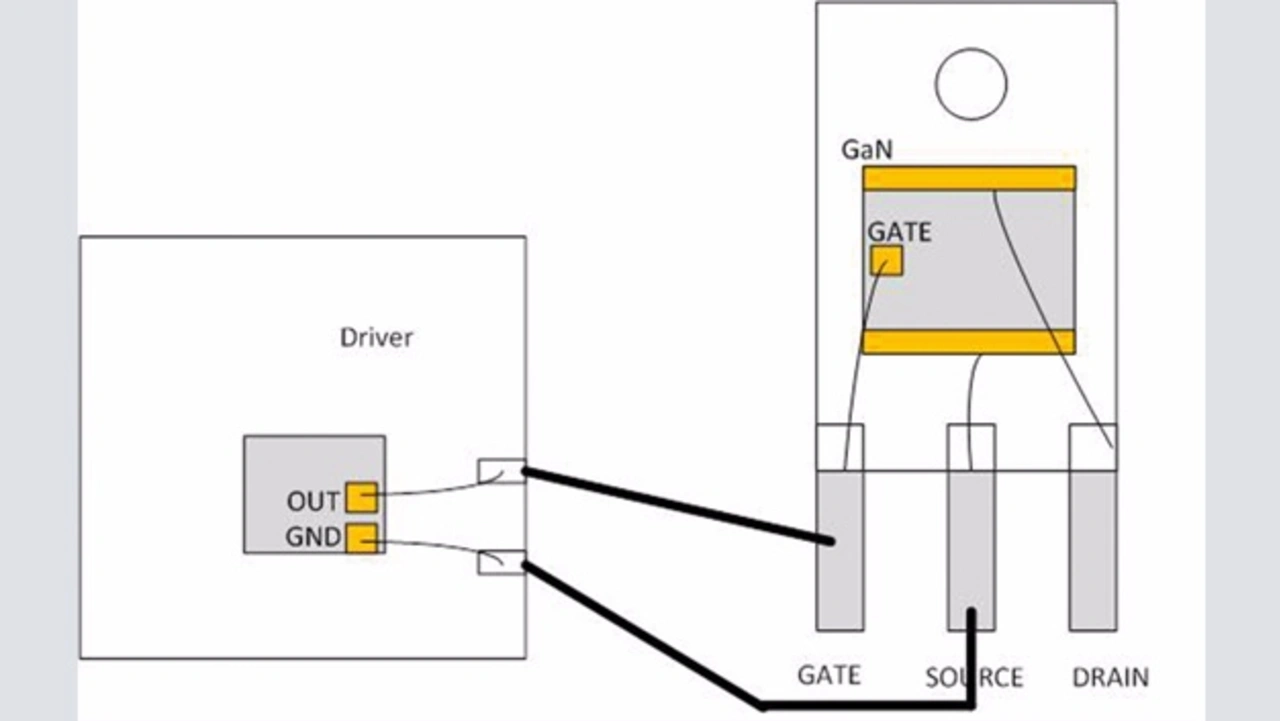

Traditionell sind GaN-Transistoren diskrete Bauelemente und werden von einem separaten Treiber-IC angesteuert, da beide Bausteine auf verschiedenen Prozesstechnologien beruhen und möglicherweise auch noch von verschiedenen Anbietern bezogen werden. Jedes Gehäuse aber hat Bonddrähte und/oder Anschlüsse mit entsprechenden parasitären Induktivitäten (Bild 1a). Treten beim Schalten hohe Anstiegsgeschwindigkeiten (du/dt) mit einigen zehn bis hundert Volt pro Nanosekunde auf, können diese parasitären Induktivitäten zu Schaltverlusten, Oszillationen und Zuverlässigkeitsproblemen führen.

Parasitäre Induktivitäten

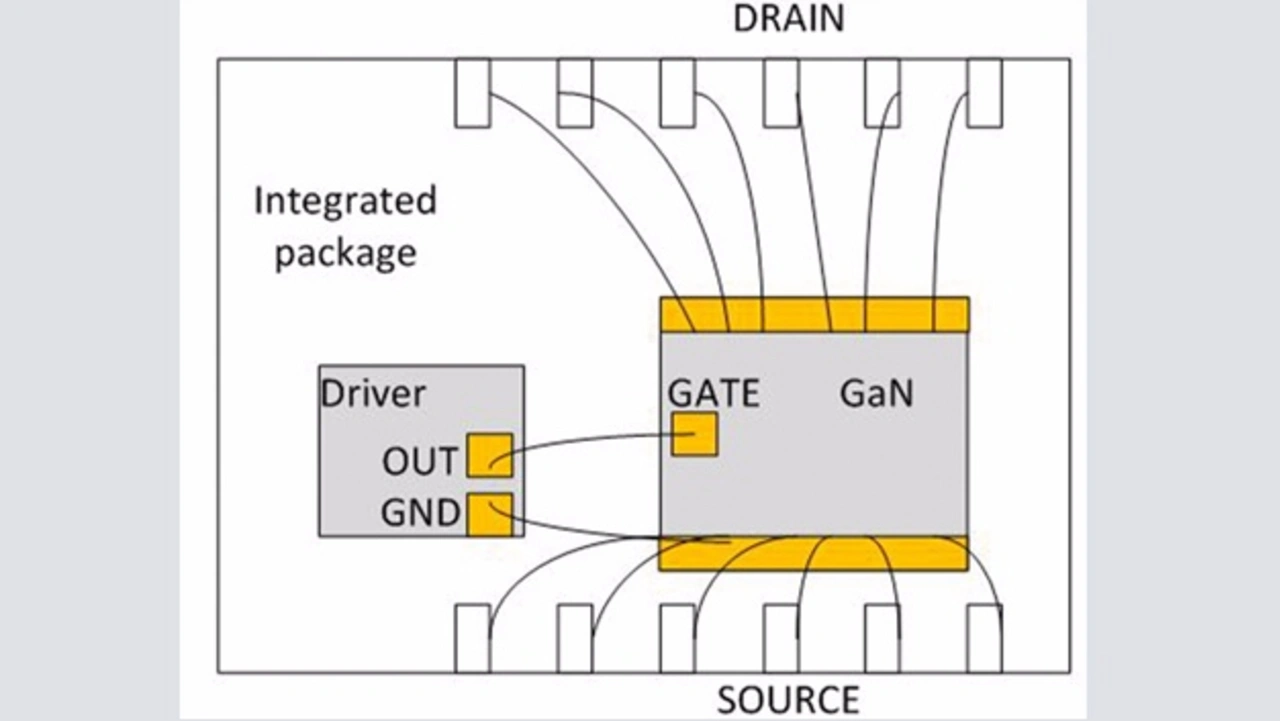

Durch Integrieren des GaN-Transistors mit seinem Treiber (Bild 1b) auf demselben Leadframe in nur einem Gehäuse entfällt die Common-Source-Induktivität, und die Induktivität zwischen Treiberausgang und GaN-Gate reduziert sich beträchtlich – ebenso wie die Induktivität der Masseverbindung des Treibers.

Im Folgenden geht es um die Probleme und Einschränkungen, die durch die genannten gehäusebedingten Streuinduktivitäten entstehen. Die Optimierung dieser parasitären Induktivitäten durch die Integration von GaN-FET und Treiber in dasselbe Gehäuse entschärft die Probleme und ermöglicht exzellente Schalteigenschaften bei einem du/dt von mehr als 100 V/ns.

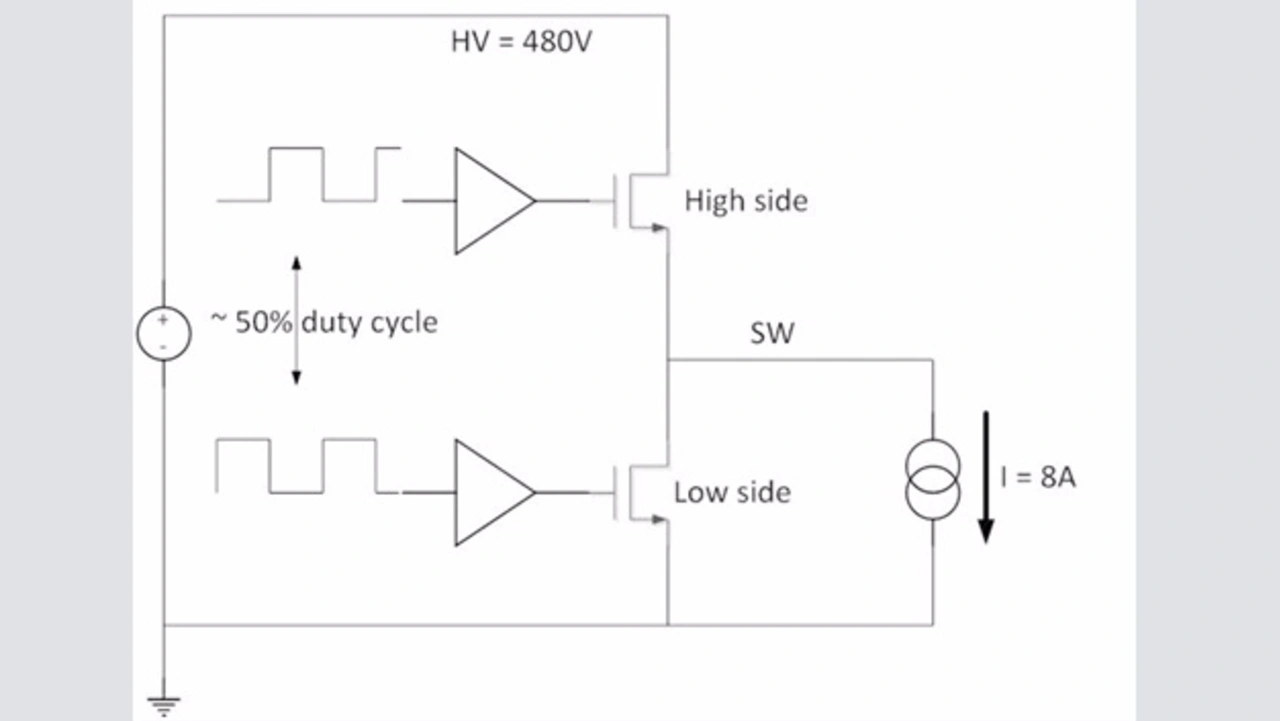

Um die Auswirkungen der parasitären Induktivitäten zu simulieren, wurde eine mit GaN-Transistoren vom Verarmungstyp (selbstleitend, normally on) bestückte Halbbrücke in der Direct-Drive-Konfiguration verwendet (Bild 2). Die Halbbrücke wurde als Tiefsetzsteller eingerichtet, mit einer Busspannung von 480 V, 50 % Tastverhältnis, 50 ns Totzeit (die Ausgangsspannung UOUT betrug 240 V) und einem Spulenstrom von 8 A. Das GaN-Gate wird abwechselnd direkt mit dem Ein- und Ausschaltpegel angesteuert. Die resistive Ansteuerung legt die Anstiegsgeschwindigkeit des GaN-Bausteins beim Einschalten fest, und eine Stromquelle emuliert eine induktive Last am Schaltknoten (SW) eines im nichtlückenden Betrieb arbeitenden Tiefsetzstellers.

- Optimierte Performance

- Einfluss der Common-Source-Induktivität

- Schutzfunktionen für den GaN-HEMT