Energieeffizientes KI-System

AI goes Ultra-Low-Power – Teil 2

Nachdem im 1. Teil [5] das Gesamtkonzept eines Ultra-Low-Power-Beschleunigers für die EKG- oder allgemeine Zeitreihenanalyse vorgestellt wurde, werden nun einzelne Aspekte des Chipentwurfs genauer beleuchtet.

Das Preprocessing (vergleiche Bild 2 im 1. Teil dieses Aufsatzes [5]) besteht hauptsächlich aus einem Bandpassfilter mit anschließendem Downsampling. Obwohl dieser Teil der Signalverarbeitung simpel im Vergleich zum Neuronalen Netzwerk (NN) erscheint, musste dieser Schaltungsteil dennoch stark optimiert werden; diese Teilschaltung läuft nämlich mit einer höheren Abtastfrequenz als der Rest und verwendet die große Wortbreite der digitalisierten Abtastwerte. Deshalb verwendete das Lo3-ML-Team an dieser Stelle verschachtelte, multiplikationsfreie CIC-Filter (Cascaded Integrator Comb, kaskadierte Integrator-Differentiator-Filter).

Neuronales Netzwerk mit speziellen Schichten

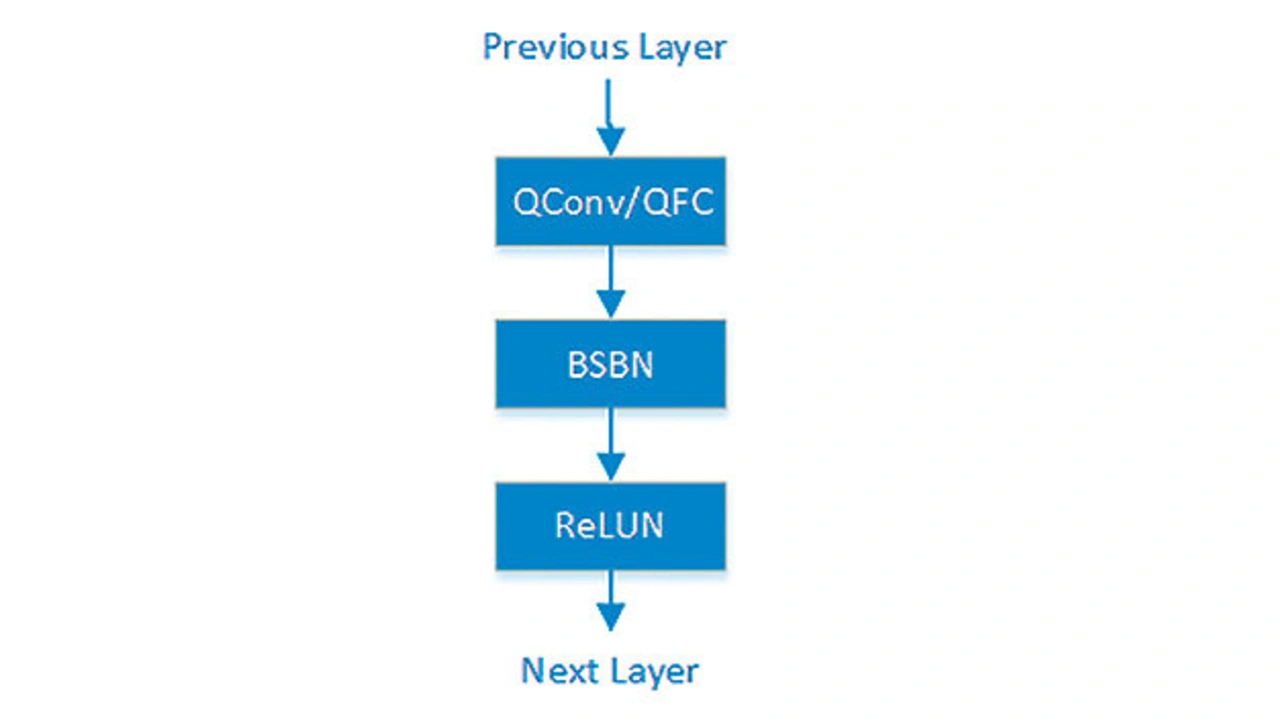

Der verwendete ML-Algorithmus hat einen maßgeblichen Einfluss auf die Energieaufnahme. Neben der Anzahl von Operationen bestimmt er auch die geforderte Quantisierung. Für maximale Energieeffizienz bei vorgegebener Klassifikations-genauigkeit kombinierte das Team mehrere Methoden aus der aktuellen Forschung, um Aktivierungen und Gewichte möglichst grob quantisieren zu können. Dafür wurden spezielle Schichttypen eingeführt: Convolutional »Lo3Conv«- und Fully-Connected »Lo3FC«-Layer mit dem in Bild 5 gezeigten Aufbau.

Jobangebote+ passend zum Thema

Zuerst erfolgt eine quantisierte Faltung bzw. FC-Berechnung (QConv/QFC). Ihr folgt eine Binary-Shift Batch Normalization (BSBN); dies ist eine Batch Normalization (BN) y=Sx+B, bei der der Bias B ein vorzeichenbehafteter 6-bit-Festkommawert ist und die Skalierung S eine Zweierpotenz im Bereich (inklusive) 1/64 … 4, d. h. mit neun möglichen Werten. Dadurch muss die Schaltung nur sehr energieeffiziente, binäre Shift-Operationen ohne »echte« Multiplikationen durchführen.

Da Bias und Skalierung konfigurierbar sind und vom Training bestimmt werden, bietet eine BSBN die nötige Flexibilität für zukünftige Anwendungen und sichert weiterhin eine hohe Energieeffizienz, verglichen zur Standard-BN. Die letzte Operation in Lo3Conv-/Lo3FC-Layern ist ReLUN – eine Rectified Linear Unit (ReLU) mit Saturation im Wert N: ReLU(x,N)=min(max(0,x),N).

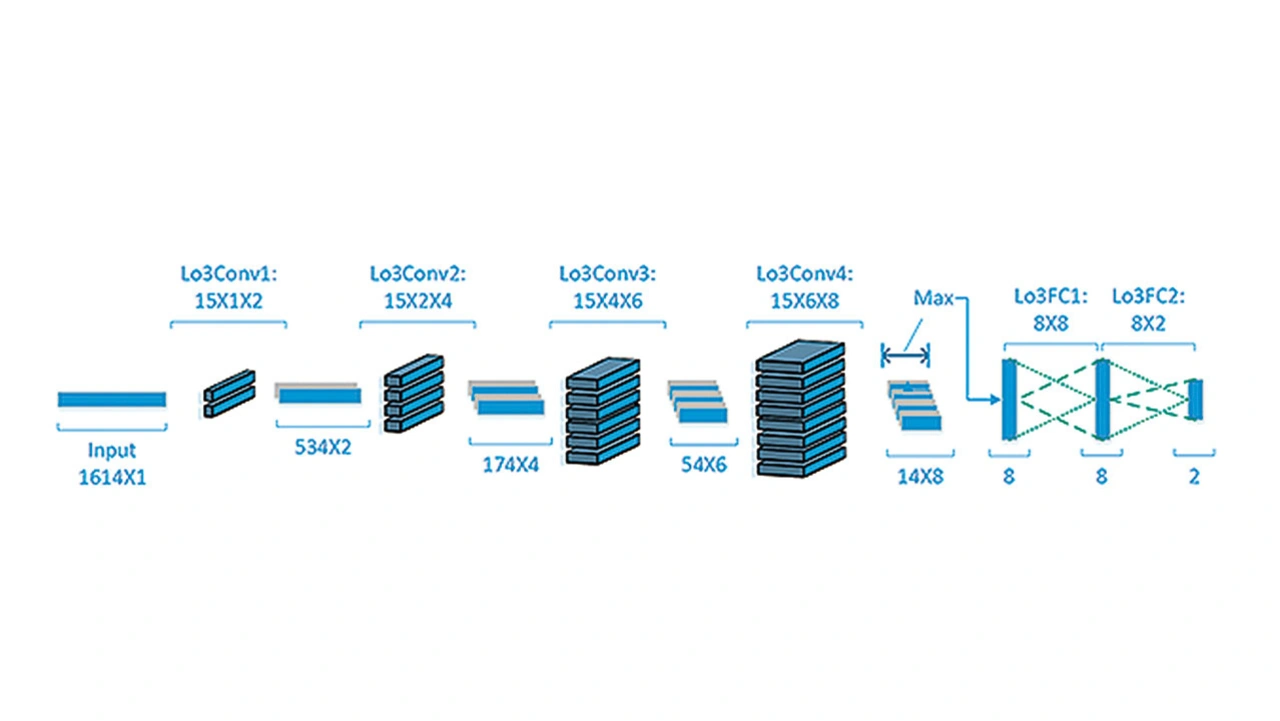

Wie Bild 6 zeigt, besteht das NN aus vier Lo3Conv-Layern, einem Max-Pooling- und schließlich zwei Lo3FC-Layern. Das ganze NN ist völlig frei von »echten« Multiplikationen, weil ausschließlich ternäre Gewichte und die beschriebene BSBN eingesetzt werden.

Wegen der Entscheidung für eine ternäre, d.h. äußerst grobe Quantisierung der Gewichte, können diese keine größeren Wertebereiche darstellen, was normalerweise das NN stark degradiert. Die BSBN wurde zur Lösung dieses Pro- blems eingeführt, damit jeder Ausgangskanal jeder Schicht individuell skaliert werden kann. Zur Bestimmung der Skalierungsfaktoren gibt es mehrere Möglichkeiten [6], um die Parameter B und S in der Fehlerrückführung (Backpropagation) zu optimieren. Obwohl die BSBN nur energiearme Shift-Operationen nutzt und ihr nur 5 % der Parameter und 3 % der Operationen angehören, braucht sie relativ viel Speicher und Energie bei der Berechnung, da hier im Gegensatz zu den Faltungs- und FC-Schichten nicht nur ternäre Parameter verwendet werden.

Der beschriebene Entwurfsablauf bezieht die Quantisierung aller Operationen und der für sie nötigen Energie bereits während der NN-Spezifikation ein. Für jeden betrachteten Kandidaten für das NN wird eine schnelle und grobe Energieabschätzung durchgeführt, indem einfach die für die quantisierten Operationen benötigte Energie mit der Zahl dieser Operationen im Kandidaten-NN multipliziert wird. Dies erlaubt sehr kurze Durchlaufzeiten im Entwicklungsprozess und entsprechend schnelle Zyklen während der NN-Entwurfsraum-Exploration.

Eine solch grobe (ternäre) Quantisierung erfordert ein Quantization-Aware-Training. Dafür hat das Lo3-ML-Team den Trainingsalgorithmus speziell angepasst, indem es Standard-TensorFlow (TF) um die eigenen Elemente QConv, QFC Layer und BSBN erweitert hat. Ohne diese Herangehensweise, nur mit Post-Training-Quantisierung, wäre die Genauigkeit des NNs extrem verschlechtert worden.

Durch die skizzierte Vorgehensweise wird zwar die Quantisierung bereits während des Trainings berücksichtigt, aber die Simulation des NNs in TensorFlow ist nicht zu 100 % identisch zur (quantisierten) Schaltung, weil alle TF-internen Berechnungen – Multiplikationen und Teilsummen – mit TF-Kernels erfolgen, die float32 und float64-Werte nutzen. Daher wurde die Inferenz als spezielle BT-Simulation (Bit True) in Python implementiert. Alle BT-Operationen entsprechen in ihrem Verhalten zu 100 % den Hardwareoperationen mit Festkommawerten, inkl. wahlweise Saturation oder Wrap-Around bei Overflows. Dies erlaubt:

- die Verifikation der HW-Implementierung, da in jedem Punkt die Zwischenergebnisse verglichen werden können und

- eine sehr frühzeitige und sehr schnelle Messung der exakten finalen Genauigkeit, die auch der Hardwarebeschleuniger so ausgeben würde. Auch dies führt zu kurzen Durchlaufzeiten und entsprechend schnellen Zyklen in der Entwurfsraum-Exploration des quantisierten NNs und erlaubt eine automatische Rastersuche über die NN-Hyperparameter.

Energieaufnahme der Schaltung bewerten und optimieren

Die Architektur des Rechenkerns für das NN, die im Zuge dieses Projekts entwickelt wurde, soll eine hinreichende Flexibilität aufweisen, damit dasselbe Konzept für unterschiedliche Applikationen angewendet werden kann. Entsprechend lässt sich dieser Beschleuniger auch für verschiedene ähnliche Problemstellungen unter Einsatz geänderter Parameter und Gewichte nutzen. Gleichzeitig soll die Umsetzung nur minimale Energie für die eigentliche Berechnung benötigen. Zudem wird die korrespondierende Schaltung besonders auf den Einsatz von ternären nicht-volatilen RRAM-Zellen hin optimiert. Ausgehend von der Grundidee datenflussgetriebener Parallelrechner wurde ein neuartiges, hochoptimiertes Schaltungskonzept entwickelt, welches besonders den Aufwand in der Steuerlogik reduziert sowie unnötige Operationen vermeidet.

Für eine möglichst geringe dynamische Verlustleistung der arithmetischen Operationen fließen bei der Entwicklung des NNs verschiedene Optimierungen ein, z.B. die Quantisierung aller Operanden auf eine geringe Bitbreite oder die Optimierung der Filterlängen zur Reduktion der notwendigen MAC-Operationen (Multiply Accumulate). Um diese Optimierungen durchführen zu können, wurde ein analytisches Energiemodell entwickelt sowie eine (Back-) Annotation von geschätzten Energiewerten der im NN durchzuführenden arithmetischen Opera-tionen in Abhängigkeit der Datenbreite der Parameter vorgenommen.

Damit konnte schon frühzeitig, während der NN-Spezifikation, eine energetische Bewertung verschiedener NN-Modelle durchgeführt werden, ohne diese komplett in Hardware umsetzen und simulieren zu müssen. Diese Optimierungen wirken sich stark positiv auf die gesamte Verlustleistung aus und reduzieren die Gesamtenergieaufnahme um einen erheblichen Teil. Schon mit geringen Optimierungen an den Schichten des NNs kann so bis zu 50 % der Energie eingespart werden.

- AI goes Ultra-Low-Power – Teil 2

- Datenübertragung ohne komplizierte Steuerung