Energieeffizientes KI-System

AI goes Ultra-Low-Power – Teil 2

Fortsetzung des Artikels von Teil 1

Datenübertragung ohne komplizierte Steuerung

Die Architektur ist so konzipiert, dass jede Schicht des NNs durch ein entsprechendes Schaltungsmodul realisiert wird. Der Datenfluss zwischen den Schichten erfordert zudem weder eine Pufferung noch eine aufwendige Steuerung. Er stimmt zudem jeweils am Ausgang eines Moduls mit dem am Eingang des nächsten Moduls überein, um bei der Verknüpfung dieser Module Steueraufwand einzusparen. Hierdurch wird ferner eine flexible Verbindung zwischen Komponenten geschaffen, um andere Netzwerkstrukturen schnell realisieren zu können.

Jobangebote+ passend zum Thema

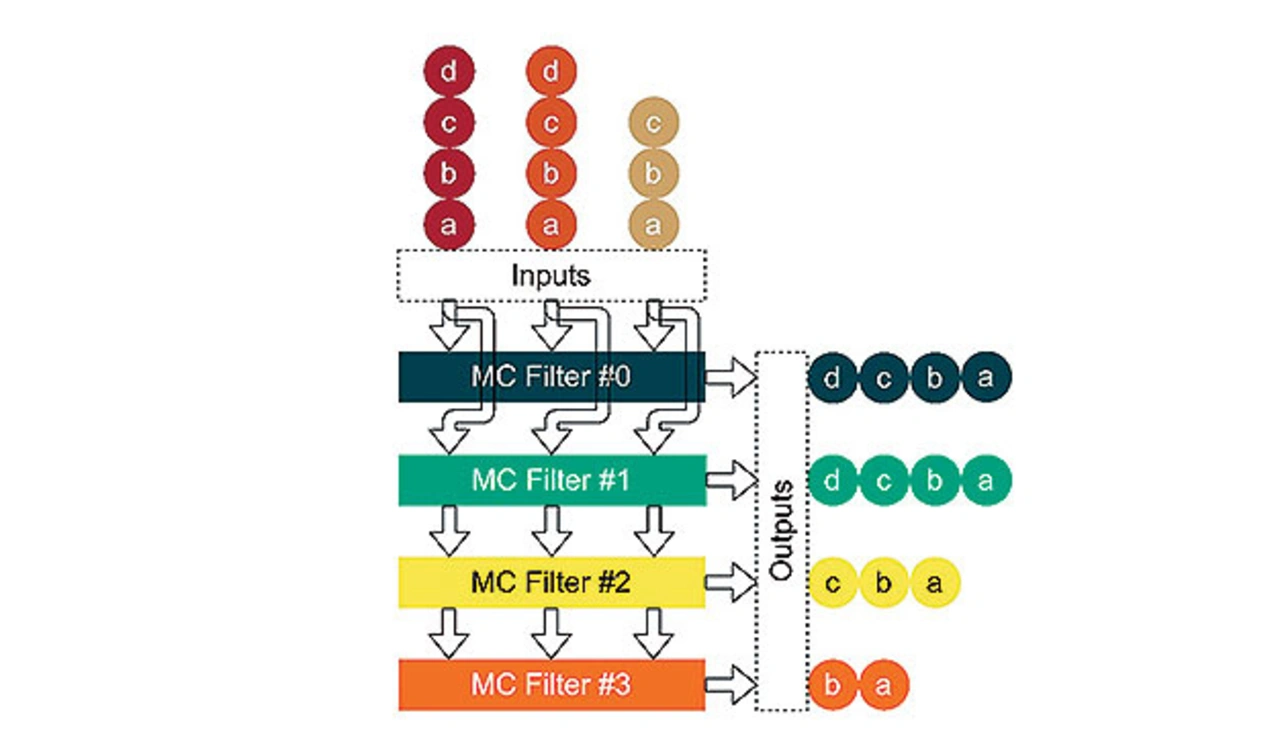

Bild 7 zeigt eine schematische Darstellung der Architektur. Die verschiedenen Kanäle einer NN-Schicht werden dabei parallel berechnet, haben jedoch unterschiedliche Verzögerungen, um eine Verarbeitung ohne Pufferung im nächsten Modul zu erleichtern. Die Schaltung ist damit außerdem genau auf die Datenrate der einzelnen Schichten abgestimmt. Durch die Verwendung von Strides, also Datenreduktion, in den Filtern der Convolutional- und FC-Schichten, ist die Datenrate am Eingang jeder Schicht anders als am Ausgang. Diese nimmt damit in den hinteren Schichten des NNs im Vergleich zu den vorderen Schichten immer stärker ab. Die Register im Datenpfad werden daher mittels Clock-Gating und dem Einsatz von Valid-Signalen gesteuert. Die so entstandene Logik zur Steuerung des Datenflusses ist klein und sehr effizient implementierbar.

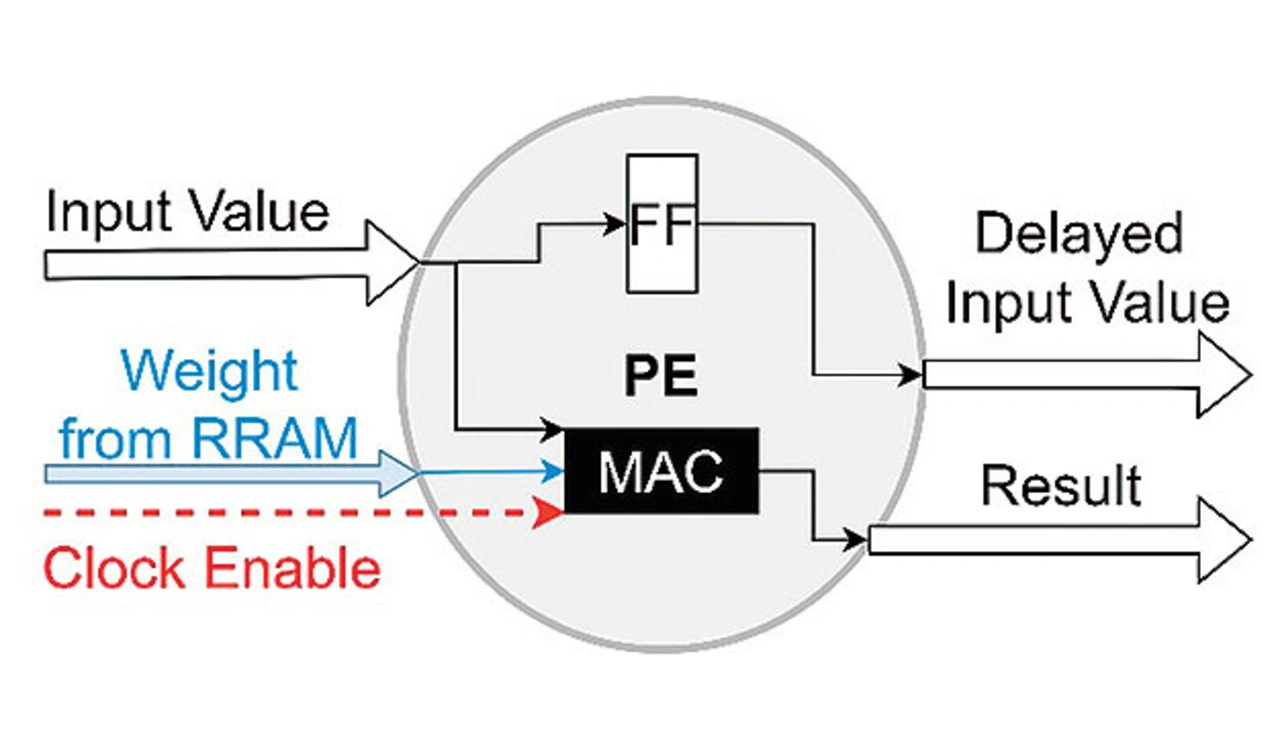

Die HW-Einheiten zur Realisierung arithmetischer Operationen bei der Umsetzung der rechenintensiven Schichten des NN werden als Processing Elemente (PE) bezeichnet und sind in Bild 8 schematisch dargestellt. Die lokal erforderlichen Gewichte sind in den zuvor genannten nicht-volatilen Parameterspeicher abgelegt und den jeweiligen PE zugeordnet. Ein PE führt eine Multiplikation eines Eingangswertes mit einem Gewichtswert durch und gibt den Eingangswert zusätzlich an das nächste PE weiter. Zur Steuerung des Datenflusses haben alle PEs Clock-Enable-Eingänge, um mithilfe eines einfachen Datenflusszählers die Berechnung nicht benötigter Teilergebnisse zu vermeiden.

Optimum bei drei Zuständen

Eine maßgebliche Innovation des hier skizzierten Entwurfs ist die Anpassung des NNs und der Schaltung an die verfügbaren Logikzustände des eingesetzten RRAM. Um eine aus Energieeffizienz- sicht optimale Anzahl an Zuständen zu erhalten, wurden dazu Voruntersuchungen durchgeführt. Neben der Abschätzung der Energie, die für eine Lese- und Schreibansteuerung der RRAM-Zellen notwendig ist, wurde auch die oben beschriebene Energie-Annotation für verschiedene neuronale Netze durchgeführt.

Das Resultat der Untersuchung zeigt ein Optimum bei drei Zuständen in den RRAM-Zellen, wofür eine effiziente und platzsparende, analoge Ausleseschaltung und ein bezüglich der Energie effizienteres NN umsetzbar sind. Beispielsweise fällt die Energie für ein NN mit binären Gewichtszuständen 1,6-mal höher aus als die eines NNs mit ternären Gewichten. Um mit wenig Aufwand eine Entwurfsraum-Exploration durchführen zu können, wurde ein eigenes Hardwaregenerierungs-Tool entwickelt. Dieses setzt aus den selbst entworfenen Hardwarekomponenten den Beschleunigerkern zusammen und parametrisiert automatisch alle Komponenten.

RRAM-Zellen mit analoger Peripherie

Das integrierte RRAM [7, 8] ist in Speicherblöcke mit je 32 Zellen eingeteilt. Jede dieser Speicherzellen kann drei verschiedene Werte annehmen: Einen »High Resistive State« (HRS) und jeweils zwei »Low Resistive States« (LRS1 und LRS2). Um ein paralleles Auslesen zu erlauben, ist jeder Speicherblock mit der benötigten, peripheren Analogschaltung ausgestattet.

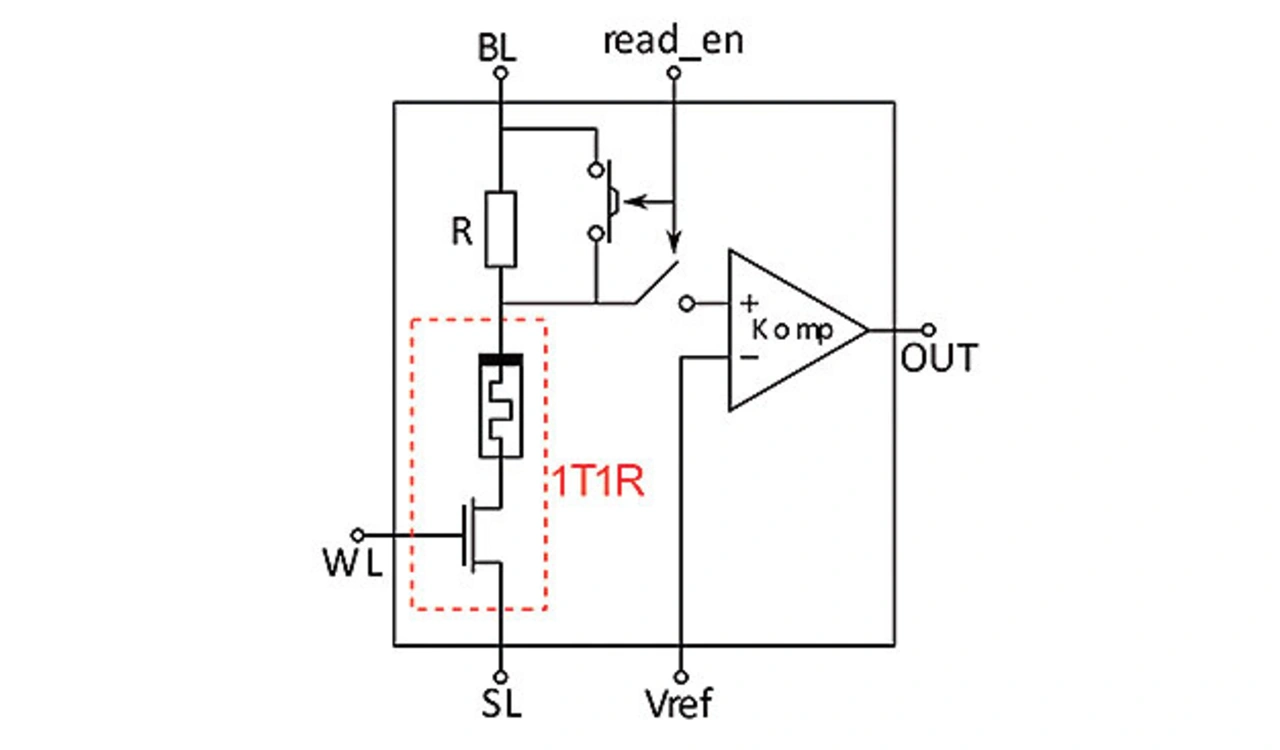

Diese umfasst je einen Operationsverstärker (OPV) und einen Referenzenblock zur Erzeugung der benötigten Spannungspegel. Zusätzlich ist jede 1T1R-Zelle (Transistor + RRAM) in eine Speicherzelle mit peripherer Beschaltung nach Bild 9 eingebettet. Die Ansteuerung der RRAM-Zellen erfolgt über Spannungspulse, die entweder an den Bitline-Anschluss (BL) oder an den Sourceline-Anschluss (SL) angelegt werden. Der Wordline-Anschluss (WL) der ausgewählten Zellen wird in dieser Phase auf eine definierte Spannung gelegt. Generell sind für jede Operation unterschiedliche Spannungspulse sowie WL-Spannungen notwendig.

Die Methode zum Auslesen des Widerstandswertes einer 1T1R-Zelle basiert auf der Auswertung der Spannung am Knoten eines Spannungsteilers, bestehend aus dem Vergleichswiderstand R sowie dem Widerstand der Speicherzelle (Bild 9). Nach dem Aktivieren der WL wird ein Spannungspuls von 0,5 V am BL-Anschluss angelegt, während der SL-Anschluss auf Massepotenzial gelegt ist. Die Spannung am Knoten zwischen dem Vergleichswiderstand R und der 1T1R-Zelle hängt somit vom Zellenwiderstand ab. Diese Spannung wird vom Komparator mit einer Referenzspannung URef verglichen.

Der Reset-Prozess, bei dem die Speicherzelle zunächst in den HRS gesetzt wird, setzt voraus, dass der Programmierstrom durch die 1T1R-Zelle in die entgegengesetzte Richtung, also vom SL-Anschluss zum BL-Anschluss, fließt. Daher muss während des Resets der Spannungspuls am SL-Anschluss angelegt werden, während der BL-Anschluss auf Massepotenzial liegt. Das Programmieren von LRS1 und LRS2 (Set) ausgehend von HRS unterscheidet sich bezüglich der Signalverläufe nicht vom Lesevorgang: Der Spannungspuls wird an die BL angelegt, während die SL mit Masse verbunden ist. Die WL-Spannung dient hier zur Begrenzung des Schreibstromes.

Arbeitsteilung und Ruhepausen sparen Energie

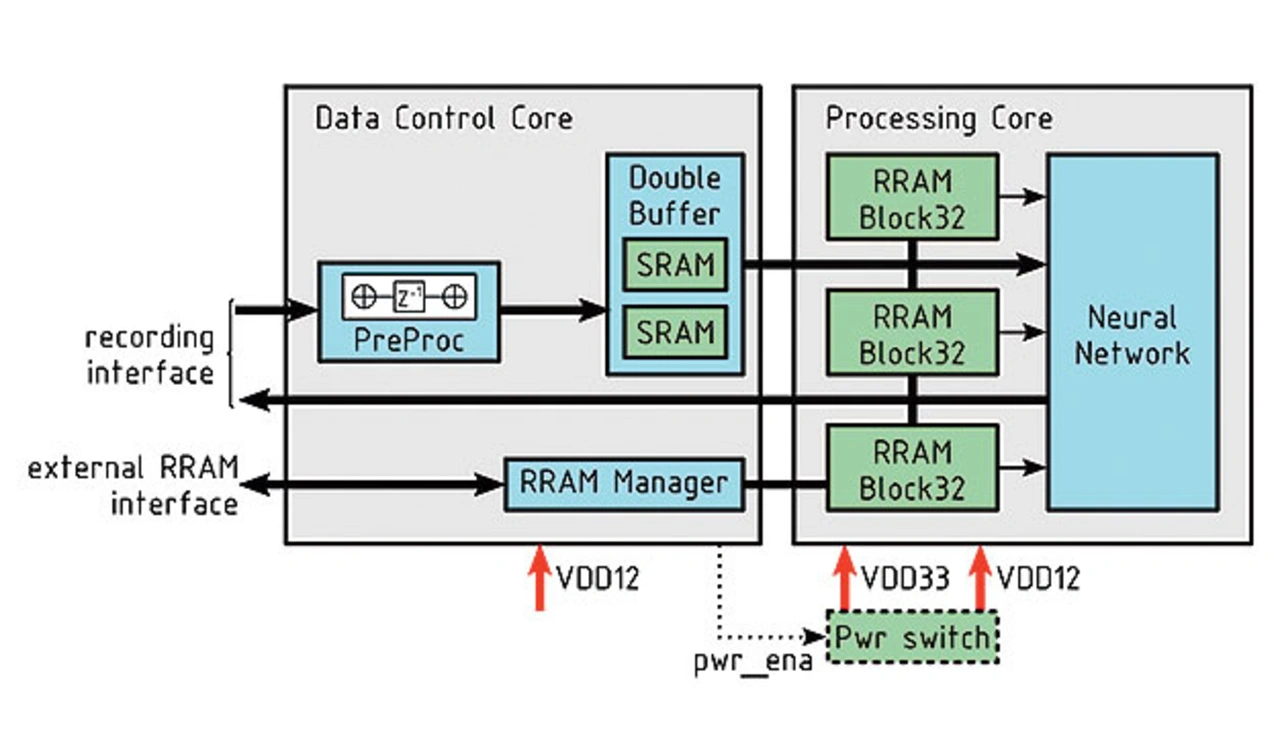

Abschließend wurden die implementierten Komponenten in ein Gesamtsystem zusammengefasst und dieses dazu in zwei separate ASIC-Blöcke aufgeteilt: Einen Data Control Core zur Kommunikation mit der Außenwelt für Dateneingabe (»Recording Interface«) und Konfiguration der RRAMs (»External RRAM Interface«) sowie zur Vorverarbeitung und Zwischenspeicherung von Daten, und einen Processing Core zur Ausführung der eigentlichen Berechnungen des NNs (Bild 10).

Sämtliche digitalen Komponenten sind in VHDL implementiert und werden unter Verwendung der zugrundeliegenden Halbleiterfertigungstechnik durch Synthese- und Place&Route-Werkzeuge in Netzlisten bzw. in entsprechende Layouts überführt, wobei beide Blöcke separat und unabhängig voneinander betrachtet werden. Zur Adaption der RRAM-Technik an diesen Entwurfsablauf werden jeweils 32 RRAM-Zellen mit der zugehörigen analogen und digitalen Beschaltung zu einem Makro- block »RRAMBlock32« zusammengefasst. Von diesem können beliebig viele Instanzen in einer Schiebekette miteinander verbunden werden, was eine Ansteuerung von außerhalb zur ein- oder mehrmaligen Programmierung der Gewichtswerte erlaubt.

Anders als der Data Control Core, der die gesamte Zeit über aktiv ist und die vom Sensor mit geringer Abtastrate aufgenommenen Daten permanent mit einem Abtastwert pro Takt entgegennimmt und aufbereitet, ist die Versorgungsspannung des Processing Cores die meiste Zeit über abgeschaltet.

Auf feingranulares Power-Gating wurde dabei auch aufgrund mangelnder Unterstützung der Bibliotheken der zugrundeliegenden Halbleiterfertigungstechnik verzichtet – stattdessen werden sämtliche Versorgungsspannungen durch Schalttransistoren (»Pwr Switch« in Bild 9) abgeschaltet, die neben dem Processing Core platziert sind. Sobald seitens des Data Control Core genügend EKG-Daten bereitstehen, d.h. ein 12,7-s-Fenster vollständig eingelesen wurde, wird die Versorgungsspannung des Processing Cores aktiviert und unmittelbar das parallele Lesen der Gewichte aus den RRAMs veranlasst. Nach Abschluss der neuronalen Verarbeitung wird die Versorgungsspannung des Processing Cores zur Vermeidung unnötiger statischer Verluste sofort wieder deaktiviert.

Die Abschätzung der zur Verarbeitung der EKG-Aufnahmen erforderlichen Energie erfolgt durch eine Simulation auf Netzlistenebene anhand der tatsächlichen, zeitlichen Verläufe aller vorhandenen Signale. Die Aufzeichnungen verschiedener Simulationsläufe werden dafür, unter Hinzunahme der für den jeweiligen Halbleiterfertigungsprozess spezifischen Leistungsbeschreibung der Standardzellenbibliothek, mithilfe des Werkzeugs Synopsys PrimePower analysiert.

Sowohl für die Abtastrate des Sensors als auch für die Vorverarbeitung im Data Control Core wird eine Frequenz von 512 Hz angenommen. Zur Minimierung des Energiebedarfs im Taktbaum wird hingegen eine Verarbeitungsfrequenz von 70 kHz für den Processing Core gewählt. Bedingt durch das Frequenzverhältnis sowie das Downsampling durch die Vorverarbeitung erfordert die Verarbeitung eines 12,7 s umfassenden Fensters lediglich ca. 25 ms. Die neuronale Verarbeitung ist also lediglich in ca. 0,2 % der Zeit aktiv, in der verbleibenden Zeit ist die Versorgungsspannung abgeschaltet, wodurch auch keine statische Verlustleistung anfällt.

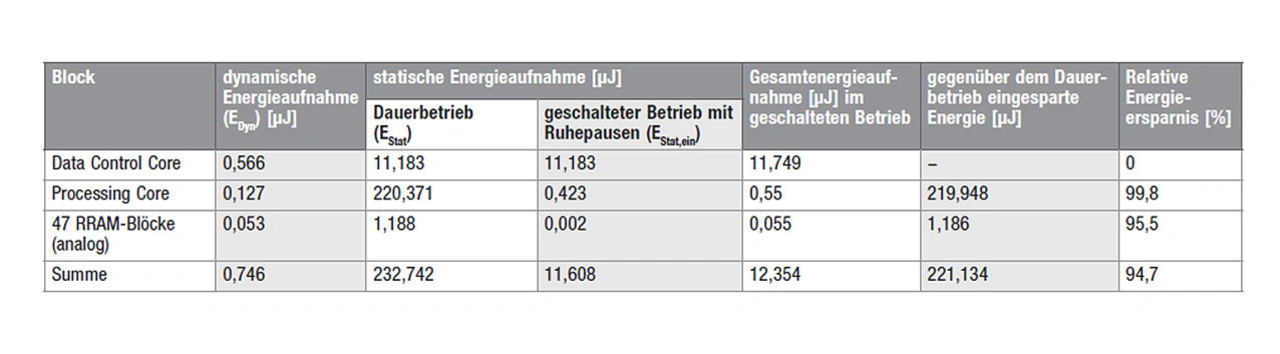

In der Tabelle sind Simulationsergebnisse dargestellt, wobei der Anteil der statischen Verluste dominiert. Durch die Abschaltung der Versorgungsspannung des Processing Cores und die korrespondierende Einsparung der statischen Verluste können deshalb im Vergleich zu einem »Always-on«-Ansatz ca. 94,7 % der Energie eingespart werden.

Erfolg durch Systemansatz und ganzheitliche Optimierung

Wenn der gesamte Entwurfsprozess – Algorithmus plus Tools, plus ASIC-Entwicklung, plus ASIC-Implementierung – gemeinsam optimiert wird, so kann tatsächlich einiges an KI-Signalverarbeitung in Geräten und Sensoren eingebaut werden, die sparsam mit Energie haushalten müssen. Eine gewisse Flexibilität sollte dabei jedoch vorhanden sein – allein schon, um spätere Updates zu ermöglichen – selbst wenn dies immer auch auf Kosten der Energieeffizienz geht. Gerade bei Zeitreihensignalen tröpfeln die Abtastwerte viel langsamer ein, als sie verarbeitet werden können. Hier lohnt sich der Einsatz von eingebetteten, nicht-flüchtigen Speichern, die das überwiegende Schlafenlegen des KI-Beschleunigers ermöglichen – hier 99,8 % der Zeit. Im gezeigten Fall spart dies ca. 95 % der Energie verglichen mit demselben Beschleuniger im »Always-on«-Modus.

Wer nun denkt, dass diese moderate Rechenlast genauso gut durch eine CPU, die dann allerdings nicht schlafen würde, abzuarbeiten wäre, der irrt jedoch: Durch den Wegfall der allermeisten Steuerlogik sowie die kleinen Wortbreiten und den Einsatz von für die Anwendung ausreichenden, ternären Gewichten, ist der beschriebene KI-Beschleuniger ein Vielfaches energieeffizienter als eine Standard-CPU. Das zeigt, dass spezielle KI-Beschleuniger in Zukunft häufig in ASICs integriert werden dürften, die damit gänzlich neue Anwendungen ermöglichen werden.

Die Autoren danken dem ganzen Lo3-ML-Team, besonders Daniel Reiser, Maen Mallah und Stefan Pechmann sowie Prof. Dr. Dietmar Fey, für die hervorragende Zusammenarbeit und ihre Beiträge zu diesem Aufsatz, dem Bundesministerium für Bildung und Forschung für die Förderung (Kennzeichen 16ES1143 und 16ES1142K), dem Projektträger VDI/VDE, dem DFKI Kaiserslautern und dem IHP Frankfurt/Oder für ihre Unterstützung während des Projektes.

Literatur:

[5] Breiling, M.; Reichel, P. und Reichenbach, M.: Energieeffizientes KI-System – Teil 1: AI Goes Ultra-Low-Power. elektronik.de, www.elektroniknet.de/halbleiter/design/ai-goes-ultra-low-power-teil-1.190213.html.

[6] Guo, Y.: A survey on methods and theories of quantized neural networks. arXiv, 1808.04752, 13. August 2018, https://arxiv.org/abs/1808.04752.

[7] Grossi, A.; et al.: Impact of the precursor chemistry and process conditions on the cell-to-cell variability in 1T-1R based HfO2 RRAM devices. Scientific Reports, 24. Juli 2018, www.nature.com/articles/s41598-018-29548-7.

[8] Reuben, J.; Fey, D. und Wenger, C.: A Modeling Methodology for Resistive RAM Based on Stanford-PKU Model With Extended Multilevel Capability. IEEE Transactions on Nanotechnology, 2019, S. 647–656, DOI: 10.1109/TNANO.2019.2922838.

Die Autoren

Dr. Peter Reichel

studierte in Dresden Informationssystemtechnik und promovierte in technischer Informatik. Er ist seit 2011 am Fraunhofer-Institut für Integrierte Schaltungen IIS, Institutsteil Entwicklung Adaptiver Systeme EAS in Dresden, tätig und arbeitet als wissenschaftlicher Mitarbeiter im Bereich intelligenter Sensorik.

peter.reichel@eas.iis.fraunhofer.de

Dr. Marco Breiling

studierte Elektrotechnik in Karlsruhe, Trondheim, Paris und Southampton und promovierte in Erlangen. Er ist seit 2001 am Fraunhofer- Institut für Integrierte Schaltungen IIS in Erlangen tätig. Dort arbeitet er als Chief Scientist an den neuromorphen Hardwareentwicklungen.

marco.breiling@iis.fraunhofer.de

Dr. Marc Reichenbach

studierte Informatik in Jena und promovierte in Erlangen. Seit 2010 ist er an der Friedrich-Alexander-Universität (FAU) am Lehrstuhl Rechnerarchitektur tätig. Als Post-Doktorand forscht er dort an neuen energieeffizienten Rechnerarchitekturen u.a. für Anwendungen aus dem Bereich der künstlichen Intelligenz.

marc.reichenbach@fau.de

- AI goes Ultra-Low-Power – Teil 2

- Datenübertragung ohne komplizierte Steuerung