Im Rauschen eingebettete Signale

Schwache Signale mit Lock-in-Verstärkern hochgenau messen

Fortsetzung des Artikels von Teil 5

Mit FPGA und Front-End

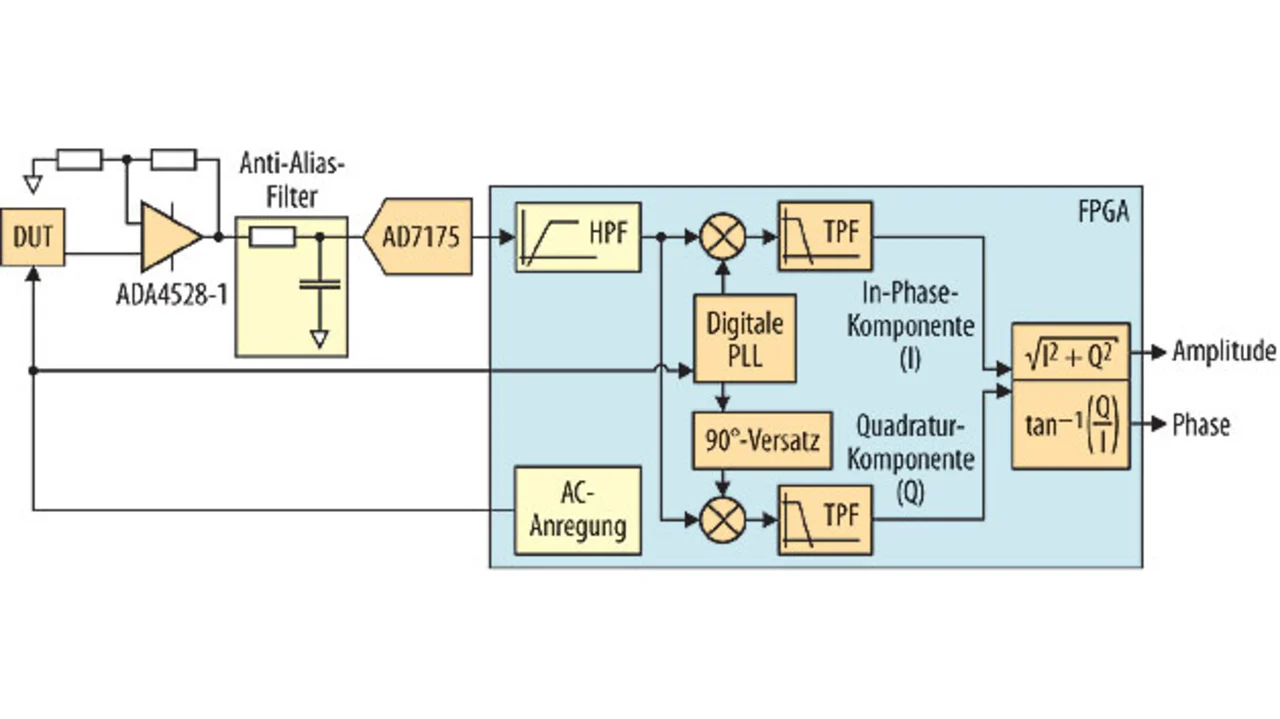

Obwohl das Messsystem also auch mit einer diskreten PLL und Multiplizierern aufgebaut werden könnte, ergeben sich durch den Einsatz eines FPGA zur Implementierung der Lock-in-Verstärkerfunktionen mehrere Vorzüge. Bild 11 zeigt einen Lock-in-Verstärker bestehend aus einem FPGA und einem Front-End, das auf dem driftfreien Verstärker ADA4528-1 und einem 24-bit-Sigma-Delta-ADC des Typs AD7175 basiert. Eine derartige Anwendung benötigt keine sehr hohe Bandbreite. Somit kann man die äquivalente Rauschbandbreite des Lock-in-Verstärkers auf 50 Hz festlegen. Das DUT (Device Under Test) ist wiederum ein extern anregbarer Sensor.

Der ADA4528-1 ist in diesem Beispiel für eine Rauschverstärkung von 20 konfiguriert, um den gesamten Arbeitsbereich des A/D-Wandlers zu nutzen. Obwohl DC-Fehler die Messung nicht beeinträchtigen, ist es dennoch wichtig, Offset-Drift und 1/f-Rauschen zu minimieren. Denn diese beiden Merkmale schmälern den verfügbaren Dynamikbereich, insbesondere wenn der Verstärker für hohe Verstärkungen konfiguriert ist.

Der Eingangs-Offset-Fehler des ADA4528-1, der im ungünstigsten Fall 2,5 µV beträgt, stellt nur 10 ppm des Full-Scale-Eingangsbereichs des AD7175 (mit einer 2,5-V-Referenz). Der digitale Hochpassfilter nach dem A/D-Wandler entfernt jeglichen DC Offset und das Rauschen bei sehr niedrigen Frequenzen. Zur Berechnung des Ausgangsrauschens muss die Spannungsrauschdichte des AD7175 bekannt sein. Im Datenblatt ist das ADC-Rauschen mit 5,9 µVeff spezifiziert. Dieser Wert gilt für eine Ausgangsdatenrate von 50 kS/s unter Verwendung des Sinc5+Sinc1-Filters mit aktiviertem Eingangspuffer. Die äquivalente Rauschbandbreite beträgt mit diesen Einstellungen 21,7 kHz.

Daraus ergibt sich ein Grundrauschen von 40 nV/√Hz. Das Breitband-Eingangsrauschen des ADA4528 liegt bei 5,9 nV/√Hz und erscheint am Ausgang als 118 nV/√Hz, was in einer kombinierten Rauschdichte von 125 nV/√Hz resultiert. Da das Digitalfilter eine äquivalente Rauschbandbreite von lediglich 50 Hz aufweist, beträgt das Ausgangsrauschen 881 nVeff. Bei einem Eingangsbereich von ±2,5 V ergibt sich damit ein System mit einem Dynamikbereich von 126 dB.

Der Dynamikbereich lässt sich zu Lasten der Bandbreite verbessern, indem man den Frequenzverlauf des Tiefpassfilters justiert. Zum Beispiel ergibt die Einstellung der Filter auf eine äquivalente Rauschbandbreite von 1 Hz einen Dynamikbereich von 143 dB. Stellt man die Bandbreite auf 250 Hz ein, ergibt sich ein Dynamikbereich von 119 dB.

Jobangebote+ passend zum Thema

Die digitale PLL erzeugt ein Sinussignal synchronisiert auf das Anregungssignal (dies kann ein externes oder ein intern im FPGA generiertes Signal sein und muss nicht zwangsläufig sinusförmig sein). Alle Harmonischen im sinusförmigen Referenzsignal werden ebenfalls mit dem Eingangssignal multipliziert. So werden Rauschen und andere unerwünschte Signale, die in den Harmonischen enthalten sind, demoduliert – genauso als würde man zwei Rechtecksignale multiplizieren (Bild 5).

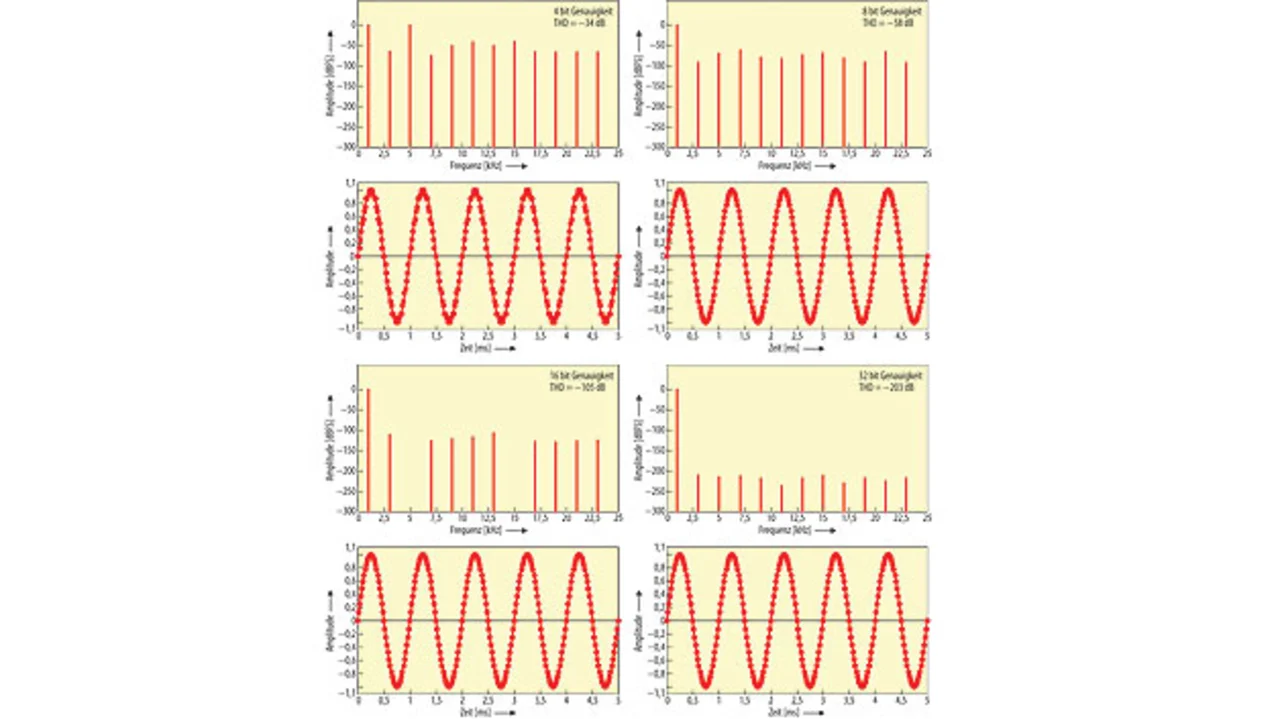

Ein Vorteil beim digitalen Erzeugen des sinusförmigen Referenzsignals besteht darin, dass es relativ einfach ist, ein Signal mit sehr geringer Verzerrung zu generieren. Dazu muss lediglich die Genauigkeit eingestellt werden. Bild 12 zeigt vier digital erzeugte Sinussignale mit 4, 8, 16 und 32 bit Genauigkeit. Wie man sieht, ergibt sich bei einer Genauigkeit von 4 bit ein Ergebnis, das sich nicht stark von dem Fall in Bild 5 unterscheidet. Doch das Ergebnis verbessert sich deutlich mit höheren Genauigkeiten. Bei einer Genauigkeit von 16 bit wäre es ziemlich aufwendig, ein analoges Signal mit einer solch geringen THD (Total Harmonic Distortion) zu erzeugen.

Bei 32 bit, wo die THD über –200 dB beträgt, ist es unmöglich, die Eigenschaften mit einer Analogschaltung zu erreichen. Außerdem sind die Signale, da sie digital erzeugt sind, perfekt wiederholbar. Sobald die Daten in Digitaldaten umgewandelt sind und in das FPGA gelangen, gibt es kein zusätzliches Rauschen und keine zusätzliche Drift, die man berücksichtigen müsste.

Nach den Multiplizierern entfernen die Tiefpassfilter alle hochfrequenten Komponenten und geben die In-Phase- und Quadratur-Komponenten des Signals aus. Nimmt man weiterhin an, dass die äquivalente Rauschbandbreite der Filter nur 50 Hz beträgt, gibt es keinen Grund, Daten mit der ursprünglichen Abtastrate von 250 kS/s zu liefern. Die Tiefpassfilter können eine Dezimierungsstufe enthalten, um die Ausgangsdatenrate zu reduzieren. Der letzte Schritt im Prozess ist, die Höhe und Phase des Eingangssignals von den In-Phasen- und Quadratur-Komponenten zu berechnen.

| Luis Orozco |

|---|

ist System-Applikationsingenieur im Segment Industrial und Instrumentation von Analog Devices. Sein Fokus liegt auf der Präzisionsmesstechnik, der chemischen Analyse und dem Umwelt-Monitoring. Orozco arbeitet seit Februar 2011 für Analog Devices. |

luiz.orozco@analog.com

- Schwache Signale mit Lock-in-Verstärkern hochgenau messen

- Prinzip eines Lock-in-Verstärkers

- Einfache Lock-in-Implementierungen

- Eine integrierte Alternative

- Mehrere Multipliziererstufen

- Mit FPGA und Front-End