Dank sicherer Zen-Mikroarchitektur

Mehr Support für Serverprozessoren

Fortsetzung des Artikels von Teil 1

»Epyc-7002«-Familie mit »Zen 2«

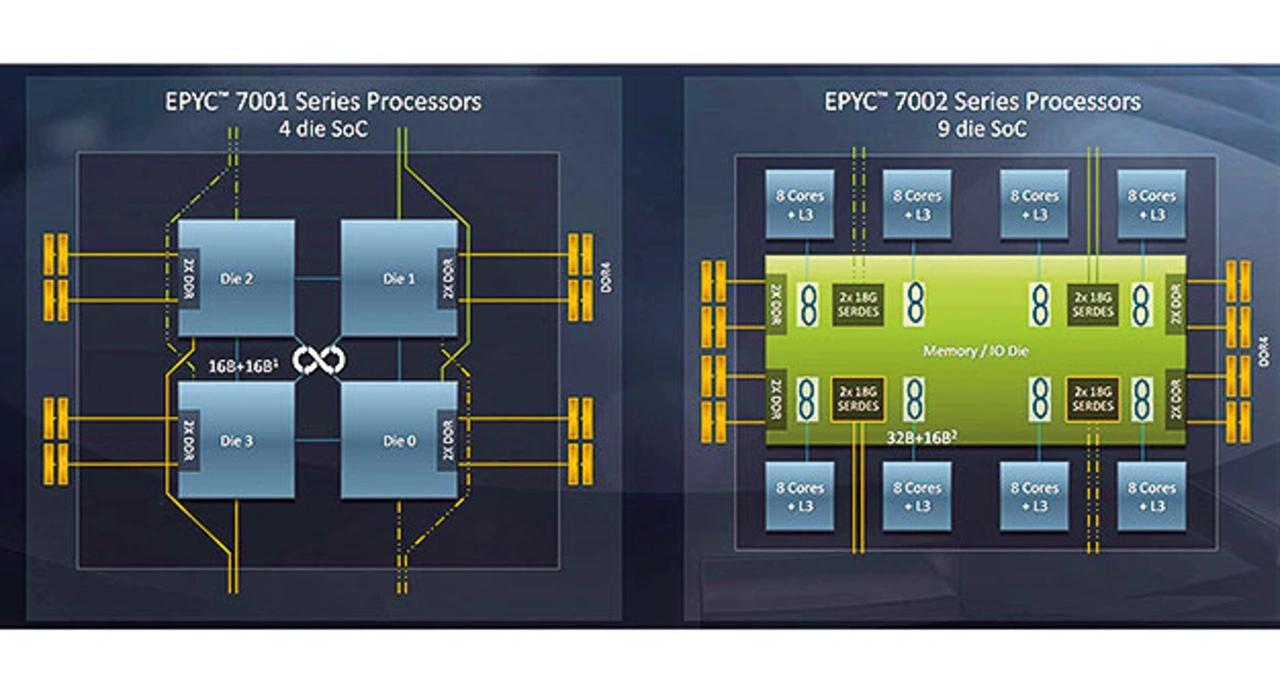

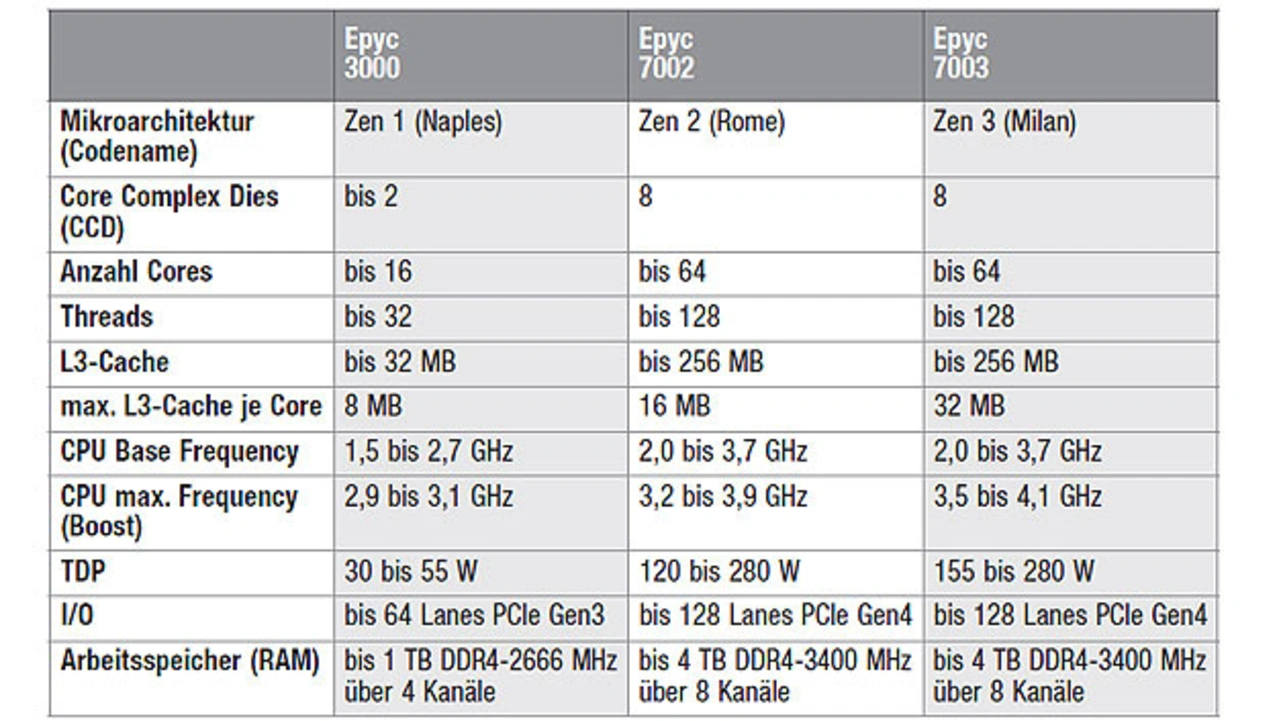

Basierend auf der zweiten Generation der Zen-Mikroarchitektur implementieren die Epyc-7002-Prozessoren (Codename »Rome«) einen zentralen I/O-Die. Er vereinfacht die Off-Chip-Kommunikation der Core Complex Dies im Vergleich zur ersten Epyc-Generation deutlich.

Jobangebote+ passend zum Thema

Weil AMD die CCDs der CPUs im 7-nm-Prozess fertigt, bieten sie bis zu 64 Cores. Anstelle der vier CCDs im Zen-1-Design erhöht der Hersteller die Anzahl der Multi-Core-Blöcke in Rome auf acht. Außerdem hebt sich hiermit der prozessorinterne Level-3-Cache um das Vierfache von 64 MB bei Zen 1 auf bis zu 256 MB an und verteilt sich effektiver auf die Cores. Die bis zu vier Kerne innerhalb eines Core Complexes (CCX) teilen sich somit 16 MB L3-Cache anstelle 8 MB je CCX beim Vorgänger (Bild 3).

Die wiederum 128 PCIe-Lanes auf dem I/O-Die sind ab sofort über PCIe der vierten Generation angebunden und die acht Speicherkanäle unterstützen bis zu 4 TB DDR4-RAM mit einer Taktrate von bis zu 3.200 MHz. Hiermit ergeben sich erhebliche Leistungssteigerungen von der ersten zur zweiten Epyc-Embedded-Generation und eine deutlich erweiterte Skalierbarkeit bezüglich speicherintensiver Workloads.

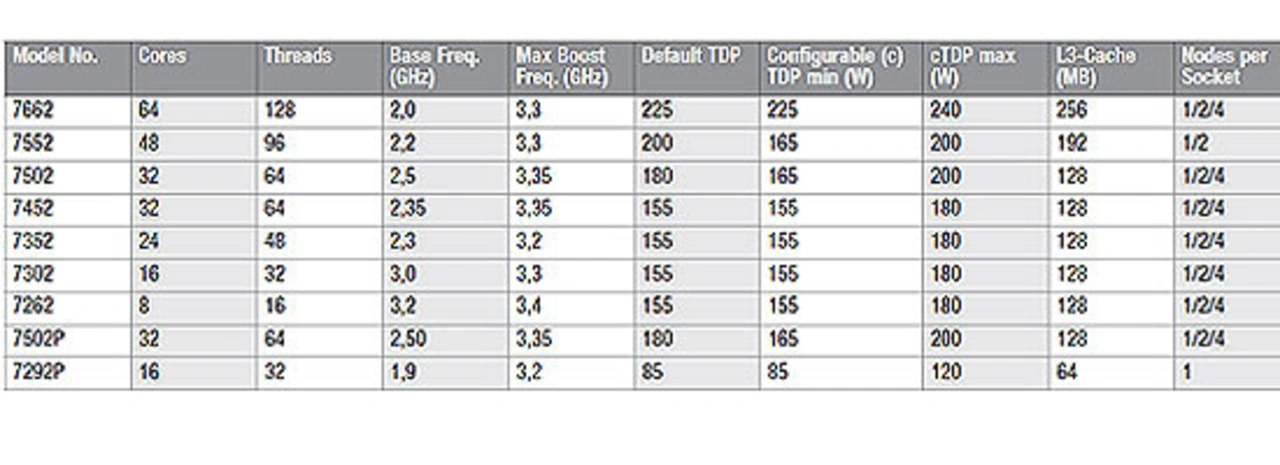

Entwickler können zwischen 19 Modellspezifikationen wählen, die sich in der Anzahl der Kerne (8, 12, 16, 24, 32 oder 64) und der Taktfrequenz unterscheiden. 14 der 19 Modellvarianten können Nutzer zudem als Zweisockel-Lösung mit bis zu 128 Cores betreiben. Die TDP der Epyc-7002er-Familie reicht von 85 bis 280 W. Neun Prozessorvarianten bietet der Prozessorhersteller mit einer Langzeitverfügbarkeit von fünf Jahren an. Sie bieten somit langzeitverfügbaren Edge-Server-Designs dieselbe Performance wie sie ansonsten lediglich in klassischen Rechenzentren mit ihren schnellen Upgrade-Zyklen zu finden sind (Tabelle 1).

Ebenso hat das Unternehmen bei der Sicherheit zugelegt: So können die Epyc-7002-Prozessoren das Register – welches der Hypervisor einer VM zuweist – über ein zusätzlich aktiviertes Modul verschlüsseln. Es verhindert, dass die Informationen der CPU-Register anderen Softwarekomponenten, beispielsweise dem Hypervisor, bekannt werden. Sollte der Hypervisor selbst kompromittiert sein, kann er nicht auf Speicherinhalte der VM zugreifen, da er einen zwischengeschalteten »Guest Hypervisor Communication Block« (GHCB) nutzt. Er liefert auf Anfragen lediglich verschlüsselte Inhalte. Das bietet zusätzliche Sicherheit für den Einsatz von Embedded-Systemen am Edge.

Epyc Embedded der dritten Generation (Zen 3)

Neu sind die Epyc-7003-CPUs (Codename »Milan«). Sie führen die Zen-3-Mikroarchitektur ein, die ebenfalls die besonders energieeffiziente 7-nm-Technik nutzt und das grundlegende Design mit CCX, CCD und Multi-Chip-Modul beibehält. Zen 3 Cores besitzen eine um 19 Prozent höhere Anzahl an Instructions per Cycle (IPC) als Zen 2 und können somit mehr Befehle pro Takt ausführen. Das ist zum einen auf die höhere Anzahl von acht, statt bisher vier CPU-Cores je Core Complex zurückzuführen.

Hiermit verdoppelt sich ebenfalls die von allen Cores im CCX gemeinsam nutzbare L3-Cache-Größe von bisher 16 MB (Zen 2) auf 32 MB. Zum anderen hat AMD die Fabric Clock der Infinity Fabric auf bis zu 1.600 MHz beschleunigt. Hiermit ist ebenfalls der schnellere DDR4-Speicher mit 3.200 MHz synchron anzubinden, was zu einer nochmals geringeren Latenz führt. Außerdem hat der CPU-Hersteller die Sicherheitsfeatures um die Funktion »Secure Nested Paging« erweitert. Mit ihr ist es den Prozessoren möglich, mehr als 500 virtuelle Maschinen pro Server kryptographisch zu isolieren und abzusichern, zumal ab sofort die entsprechende Rechenleistung bereitsteht. Somit trägt AMD konsequent den steigenden Sicherheitsanforderungen Rechnung, wie sie in Randbereichen von Netzwerken und in integrierten Applikationen zunehmend gefordert sind.

- Mehr Support für Serverprozessoren

- »Epyc-7002«-Familie mit »Zen 2«