Leistungswandler-Applikationen

Die häufigsten Fehler in Controller-Designs

Fortsetzung des Artikels von Teil 1

RC-Snubberschaltungen optimieren

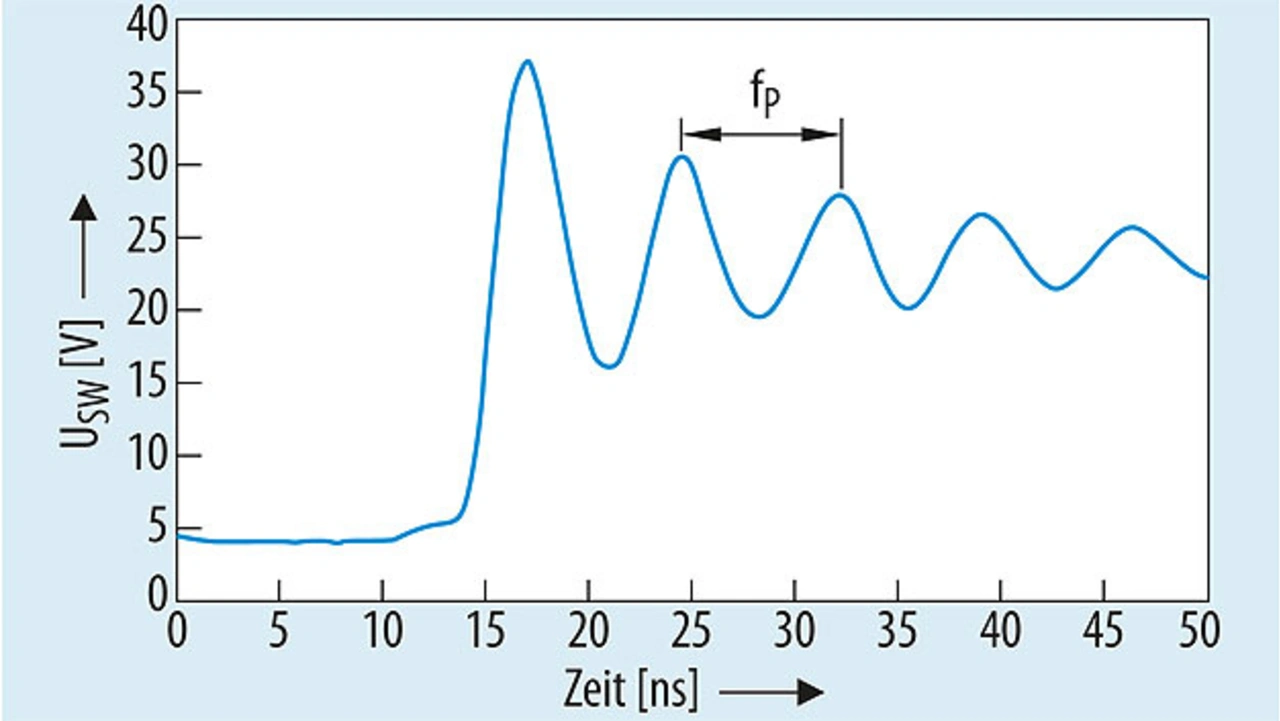

Die Bestimmung der Widerstands- und Kapazitätswerte beginnt mit dem Messen der Schwingungsfrequenz (fP) der ursprünglichen, ungedämpften Schaltung (Bild 6). Rsnub lässt sich nun folgendermaßen ermitteln:

Dabei steht CP für die parasitäre Kapazität des Synchron-FET (COSS) und Csnub beträgt die Hälfte bis das Dreifache von CP. Eine weitere praktikable Möglichkeit zum Bestimmen von Rsnub besteht darin, mit den Werten der Kondensatoren zu experimentieren, die zum Synchron-FET-parallelgeschaltet sind. Wenn die Frequenz die Hälfte des ursprünglichen Werts beträgt, hat der Parallelkondensator Csnub den dreifachen Wert der parasitären Kapazität der ursprünglichen Schaltung. Die Verlustleistung im Snubber-Widerstand lässt sich so berechnen:

Usnub ist dabei die maximale Eingangsspannung eines Abwärtswandlers.

Auf die Verlustleistung Psnub sollte sorgfältig geachtet und die Gehäusegröße von Rsnub dementsprechend gewählt werden. Wenn beispielsweise UIN=15 V, Csnub=1 nF, Rsnub=2,7 Ω und fSW=500 kHz, ergibt sich für Psnub ein Wert von 0,052 W. Dann wäre also für Rsnub das Gehäuseformat 0603 oder 0805 angemessen.

Fehler 4

Cdu/dt-induziertes Einschalten des Gates

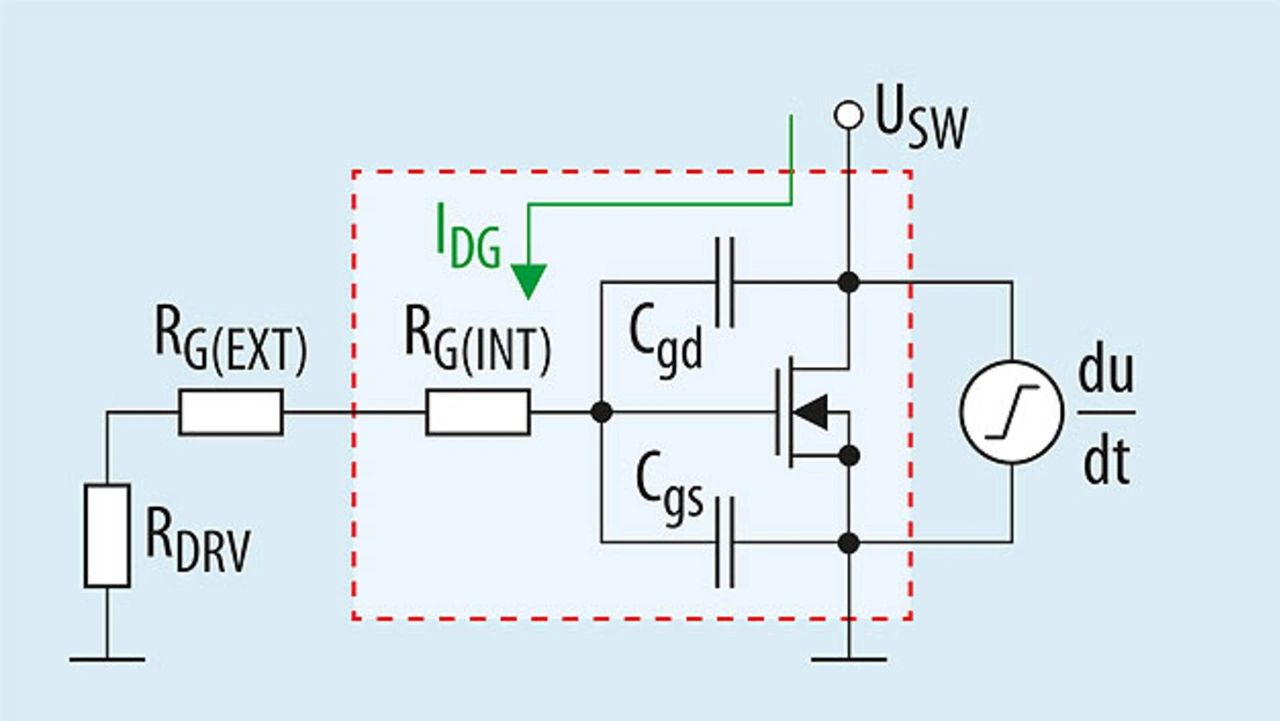

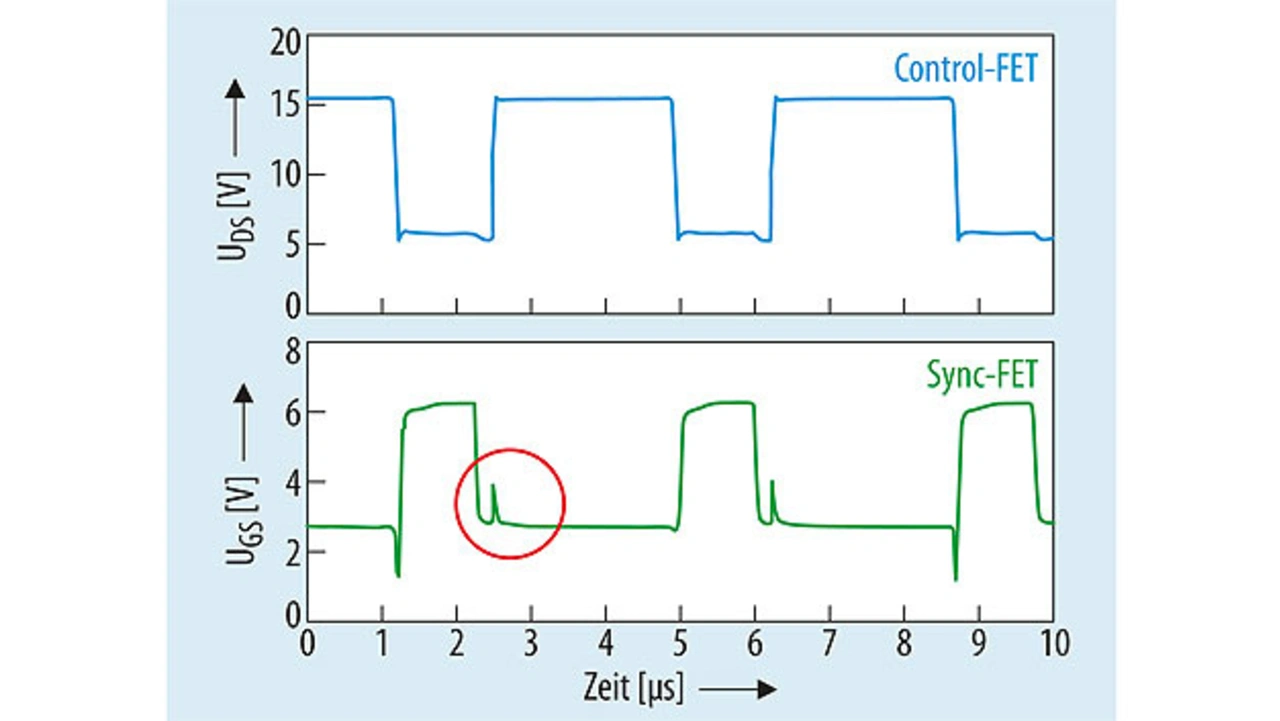

Am Synchron-FET kann es zu einem ungewollten Einschalten kommen. Dies stellt was eine potenzielle Gefahr für den MOSFET selbst dar und kann die Zuverlässigkeit des gesamten Wandlers beeinträchtigen. Beim Einschalten des Regler-FET entsteht eine steile Spannungsflanke am Synchron-FET (Bild 7). Infolge der Miller-Kapazität des FET fließt ein kapazitiver Strom (IDG= Cgd∙du/dt), der an den Gate-Anschluss des System-FET gekoppelt wird (Bild 8).

Wenn der Gesamtwiderstand aus dem intrinsischen Widerstand, dem externen Widerstand und dem Treiberwiderstand deutlich kleiner ist als die äquivalente Impedanz zwischen Gate und Source des MOSFET, fließt der gekoppelte kapazitive Strom über den eben erwähnten resistiven Weg.

Der kapazitive Strom verursacht ein unerwünschtes Prellen an den Gate- und Source-Anschlüssen des MOSFET. Ist die so induzierte Spannung größer als die minimale Schwellenspannung, kann der Synchron-FET teilweise einschalten. Dadurch entsteht ein niederohmiger Pfad zwischen Eingang und Masse.

Dies wiederum führt zu einer unerwünschten Verlustleistung in jedem Schaltzyklus, was den Wirkungsgrad des Wandlers verschlechtert und zu Lasten des Wärmemanagements sowie der Zuverlässigkeit geht. In Designs, die ein hohes Wandlungsverhältnis aufweisen und in denen der Synchron-FET wesentlich größer ist als der Regler-FET (und somit einen niedrigeren RDS(on) besitzt), ist das durch Cdu/dt induzierte Einschalten des Gates unbedingt zu berücksichtigen. Grundsätzlich sollte bei den Synchron-FETs möglichst auf Gate-Widerstände verzichtet werden.

Weitere häufige Fehler

Neben den vier detailliert beschriebenen Fehlern, gibt es noch eine Reihe weiterer häufig vorkommender Fehler, die nur kurz erwähnt werden sollen.

Unkorrekte Pin-Bedingungen

Vergewissern Sie sich anhand des Datenblatts, dass für alle Pins die vorgeschriebenen Bedingungen erfüllt sind. Auftretende Probleme haben häufig mit ungenutzten Funktionen und dem entsprechenden Zustand der Pins zu tun.

Zu hohe Übergangsfrequenz

Probleme können sich ergeben, wenn die gewählte Übergangsfrequenz mehr als ein Fünftel der Schaltfrequenz beträgt. Auch wenn die Phasenreserve gut ist, nimmt die Störempfindlichkeit des Bausteins doch zu.

Unkorrekte Kompensationswerte

Wenn die Kompensationswerte falsch gewählt sind, führt das zu einer geringen Phasen- und Verstärkungsreserve. Es ist immer sinnvoll, die Ergebnisse auf der Leiterplatte zu verifizieren, weil die Eigenschaften der Kondensatoren sich in der jeweiligen Anwendung anders auswirken können als bei einem allgemeinen Referenzdesign.

Festlegen der Kompensation mit nachträglichen Änderungen

Bei nachträglichen Änderungen kann es sich um die Verwendung anderer Ausgangskondensator-Typen, anderer Induktivitätswerte usw. handeln. Oft wird die Kompensation danach nicht neu überdacht. Bei einigen Designs werden im Rahmen von Kostensenkungs-Maßnahmen oder wegen der Bauteilverfügbarkeit nachträgliche Änderungen vorgenommen, durch die sich Fehler einschleichen können.

Temperaturabhängigkeit der Strombegrenzung

Dieses Phänomen tritt auf, wenn die Grenzströme zu nahe am Maximalstrom angesetzt werden. Es ist sinnvoll, Exemplarstreuungen der Bauelemente und temperaturbedingte Parameterschwankungen der Strombegrenzungs-Pins einzukalkulieren und Berechnungen stets auf Basis von Worst-Case-Szenarios durchzuführen.

Der Autor

Mathew Jacob

ist Applikationsingenieur bei Texas Instruments in Santa Clara. Seit er seine Arbeit bei TI im Jahr 2001 aufnahm, hat er unter anderem an Produktdefinitionen, Systemanwendungen und im Management mitgearbeitet. Jacob hat sein Studium der Elektro- und Nachrichtentechnik an der Maduraj-Universität in Indien abgeschlossen.

- Die häufigsten Fehler in Controller-Designs

- RC-Snubberschaltungen optimieren