Power-on-Package

Hochleistung ohne Verluste

Der hohe Strombedarf aktueller Highend-Prozessoren erfordert ein Umdenken bei der Stromversorgung. Denn schon ein geringer Abstand zwischen Regler und Prozessor kann zu erheblichen Leistungsverlusten führen. Abhilfe schafft das Power-on-Package-Konzept.

Die jüngsten Fortschritte im Bereich der künstlichen Intelligenz (KI) führen dazu, dass deutlich höhere Leistungen verarbeitet werden müssen. XPUs für KI-Anwendungen, also Hochleistungsprozessoren wie leistungsfähige CPUs, GPUs, komplexe FPGAs oder systemangepasste ASICs, nutzen hochentwickelte ICs mit mehreren Kernen sowie Milliarden von Transistoren und benötigen daher oft mehrere hundert Ampere zur Versorgung.

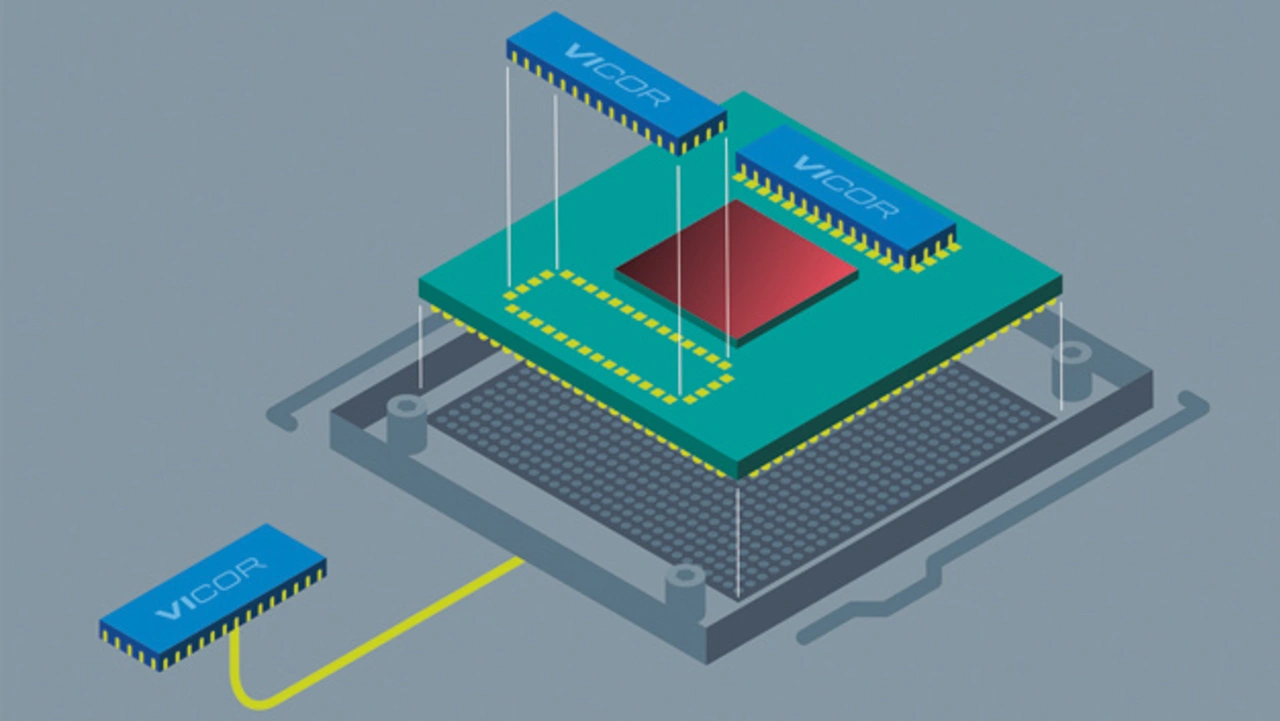

Das stellt Entwickler von Stromversorgungssystemen vor erhebliche Herausforderungen. Für die Entwicklung kompakter, leistungshungriger System-on-Chip-Lösungen gibt es nun eine neue Möglichkeit, den Leistungsteil der Anwendung zu vereinfachen: Power-on-Package (PoP) bringen die kritischen letzten Stufen eines Leistungspfades direkt auf das XPU-Substrat (Bild 1). Damit lassen sich Vorteile bei Leistungsfähigkeit und Wirkungsgrad erzielen.

Mit den Fortschritten in der Halbleitertechnik änderten sich die Anforderungen an die Versorgung von Bauteilen wie Prozessoren erheblich. Die Kern-Spannung sank von 5 V auf 3,3 V, dann auf 1,8 V und jetzt auf Spannungspegel von unter 1 V. Die Reduzierung des Platzbedarfs für bestimmte Funktionen führte dazu, dass immer mehr Logikfunktionen auf einem Chip platziert wurden.

Das führte letztendlich dazu, dass etliche Bauelemente mittlerweile thermisch limitiert sind. Die maximal vom Gehäuse abführbare Verlustleistung begrenzt die in einem Chip realisierbaren Funktionen. Mit Thermal Design Power (TDP) von oftmals weit über 100 W werden wegen der sinkenden Versorgungsspannung immer höhere Eingangsströme benötigt.

Dass Eingangsströme von über 100 A erforderlich sind, ist keine Ausnahme mehr. Die konventionelle Lösung sind Multiphase-Regler für die Versorgung von XPUs aus einem 12-V-Bus. Jedoch ist es äußerst kompliziert, hunderte von Ampere auf diese Weise bereitzustellen.

Mit sinkender Versorgungsspannung stiegen auch die Anforderungen an deren Qualität. Da die Toleranzen der Logikschaltpegel einen höheren Prozentsatz der sehr kleinen Versorgungsspannung ausmachen, muss diese sehr stabil sein und darf nur geringe Störspannungen erzeugen. Sonst besteht die Gefahr von Spannungsspitzen, die ein falsches Triggern auslösen.

Mit Strömen im Bereich von mehreren hundert Ampere führt selbst der kleinste elektrische Widerstand in den Zuleitungen zu nicht akzeptablen Spannungsverlusten. Der gleiche Effekt führt auf dem gesamten Versorgungspfad zu weiteren unerwünschten Verlusten. Zusätzlich schalten XPUs häufig komplette Kerne oder andere große Logiksegmente innerhalb von Nanosekunden ein bzw. aus und erzeugen damit große Stromänderungen, die von der Versorgung ohne ungewünschte Transienteneffekte verarbeitet werden müssen.

Nutzung von Factorized Power

Bei der PoP-Lösung wurden verschiedene, miteinander in Verbindung stehende Trends in der Stromversorgungsentwicklung verknüpft: die Trennung von Spannungsübersetzung und Regelung sowie die schrittweise Verlagerung der letzten Leistungsstufe näher zur Last. Durch kontinuierliche und gezielte Weiterentwicklung hat Vicor es geschafft, die Factorized-Power-Architektur (FPA) für die heutige PoP-Lösung zu nutzen. Damit wurde die Anwendung von FPA in Hochleistungs-Computer-Applikationen möglich.

Factorized Power ermöglicht die Verteilung der Leistung im System auf einer höheren Spannungsebene, typischerweise 48 V. Auf dem Motherboard wird diese Spannung in einer einzigen Wandlerstufe auf die von der Last benötigte Spannung herabgesetzt. Mit konventionellen Industrielösungen ist es schwierig, derart hohe Übersetzungsverhältnisse zu realisieren.

Vicor entwickelte die Sine-Amplitude-Converter-Topologie (SAC), mit der sich hohe Übersetzungsverhältnisse effizienter realisieren lassen – bei nur geringen Verlusten und niedrigen Störspannungen. In der SAC-Topologie schalten die Leistungs-MOSFETS nur beim Nulldurchgang von Spannung und Strom. Das eliminiert Schaltverluste. Die Schaltfrequenz darf hoch sein, was den Bedarf an Kapazitäten im Ausgangsfilter minimiert.

Bei einer PoP-Lösung wird ein Modul mit der Bezeichnung Modular Current Multiplier (MCM) direkt auf dem Substrat platziert, welches auch das XPU-Silizium trägt. Wie der Name schon sagt, ist das MCM einfach nur ein DC/DC-Wandler mit festem Übersetzungsverhältnis (quasi ein DC-Übertrager).

Aus einer über die Pins des XPU-Substrats bzw. -Gehäuses gelieferten und auf dem Substrat weitergeleiteten höheren Spannung mit geringerem Strom erzeugt es die vom Chip benötigten niedrigen Versorgungsspannungen und hohen Ströme. Diese Anordnung bietet klare Vorteile: Der höchste Strom tritt in der Verbindung zwischen Modular Current Multiplier und XPU auf. Ein geringer Widerstand dieser Verbindung erzeugt geringe Leitungsverluste und eine geringe Impedanz hilft bei der Reaktion des MCM auf schnelle Laständerungen.

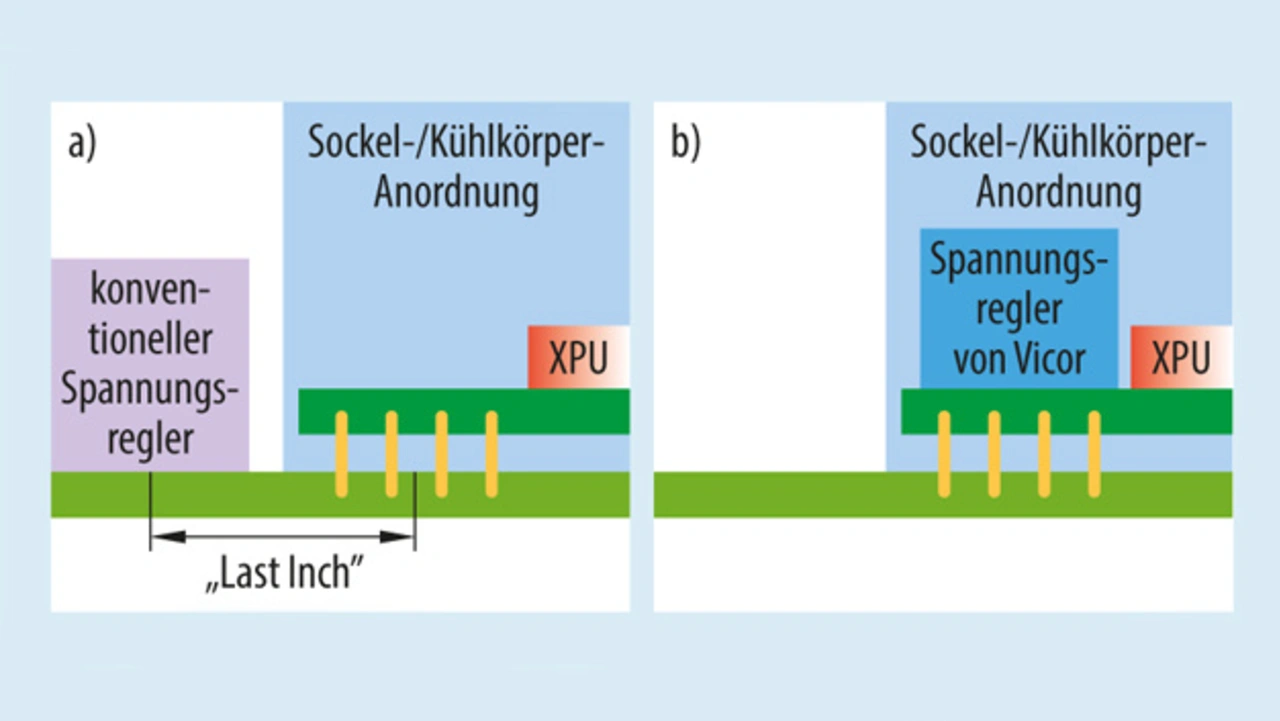

Wie in Bild 2 gezeigt, wird dieser Bereich als »Last Inch« oder die letzten Millimeter im Leistungspfad der XPU bezeichnet. Bei einer konventionellen Lösung können diesen letzten Millimeter sowie die Pins einen Widerstand von mehreren hundert Mikroohm aufweisen. Bei einer XPU mit einem Strombedarf von 200 A würde ein Leitungswiderstand von 500 µΩ einen Spannungsabfall von 100 mV bedeuten.

Dies wären mehr als 10 % der unter 1 V liegenden Versorgungsspannung. Noch schlimmer wären in diesem Beispiel die zusätzlichen Leitungsverluste von 20 W in direkter Nähe zur XPU. Um dies zu vermeiden, wird beim PoP-Ansatz das MCM auf dem Bauelement platziert und die XPU-Versorgung erfolgt vom Motherboard über die Pins auf einem hohen Spannungslevel mit entsprechend geringeren Strömen. Die Verluste auf der Leiterkarte werden dadurch reduziert. Man benötigt weniger Kupfer für die Leistungspfade auf der Leiterkarte.

Ohne den Wandler auf dem Substrat ließe sich eine ausreichend niederohmige Verbindung für die Versorgung der Kerne nur durch die Verwendung von vielen Pins erreichen. Durch die Platzierung des MCM direkt auf dem XPU-Substrat beträgt der Strom vom Motherboard zum XPU-Träger typischerweise nur 1/50 des von der XPU benötigten Stroms. Die Anzahl der für die XPU-Stromversorgung benötigten Pins reduziert sich dadurch um mehr als den Faktor 10.

Aufbau der PoP-Lösung

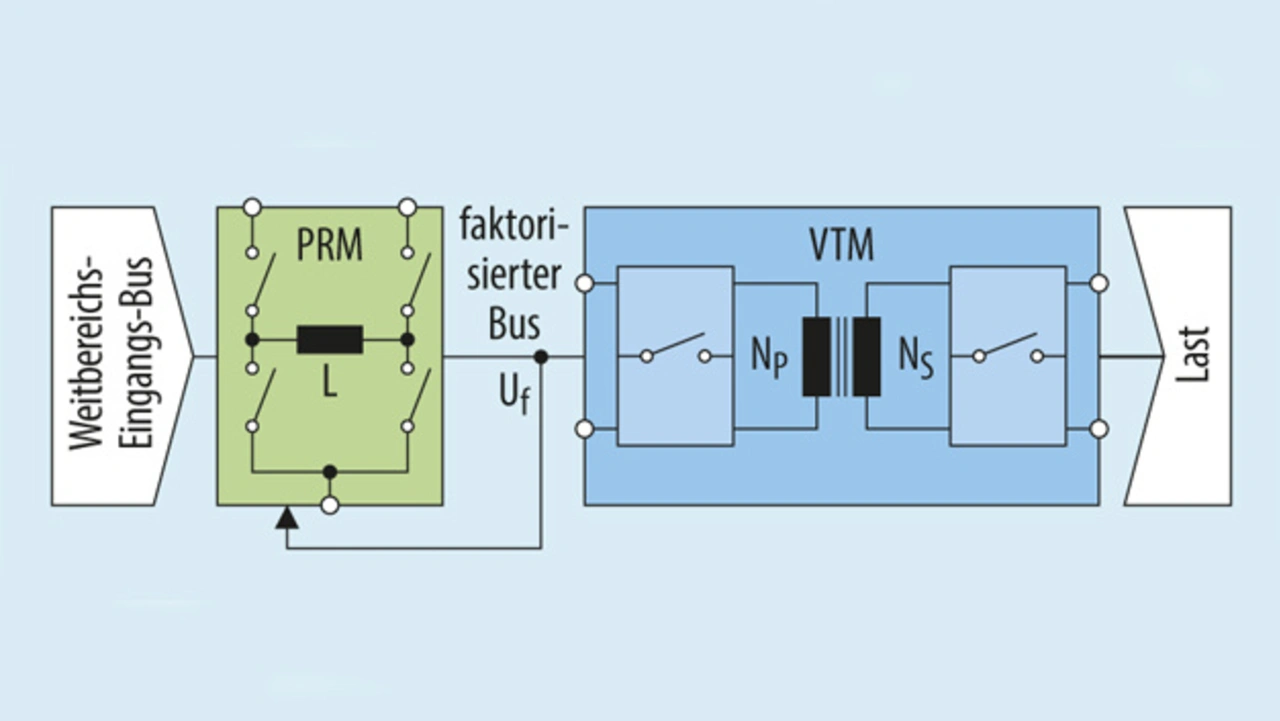

Die ursprünglich von Vicor entwickelte Factorized Power Architecture (Bild 3) integriert einen PRM-Spannungsregler und ein VTM-Strommultiplizierer-Modul. Wie in einem traditionellen FPA-Design wird bei einer PoP-Lösung eine Vorreglerstufe (Pre-Regulation Module) vor dem Strommultiplizierer platziert. In diesem Fall handelt es sich um ein MCM-Treiber-Modul oder MCD, das sich auf dem Motherboard befindet.

Die PoP-Lösung vereinigt also die PRM- und VTM-Funktionen in den MCD- und MCM-Modulen und behält dadurch die Factorized Power Architecture. Für eine noch bessere Regelgenauigkeit kann eine Regelschleife am Ausgang der letzten Stufe installiert werden, um damit das PRM zu steuern.

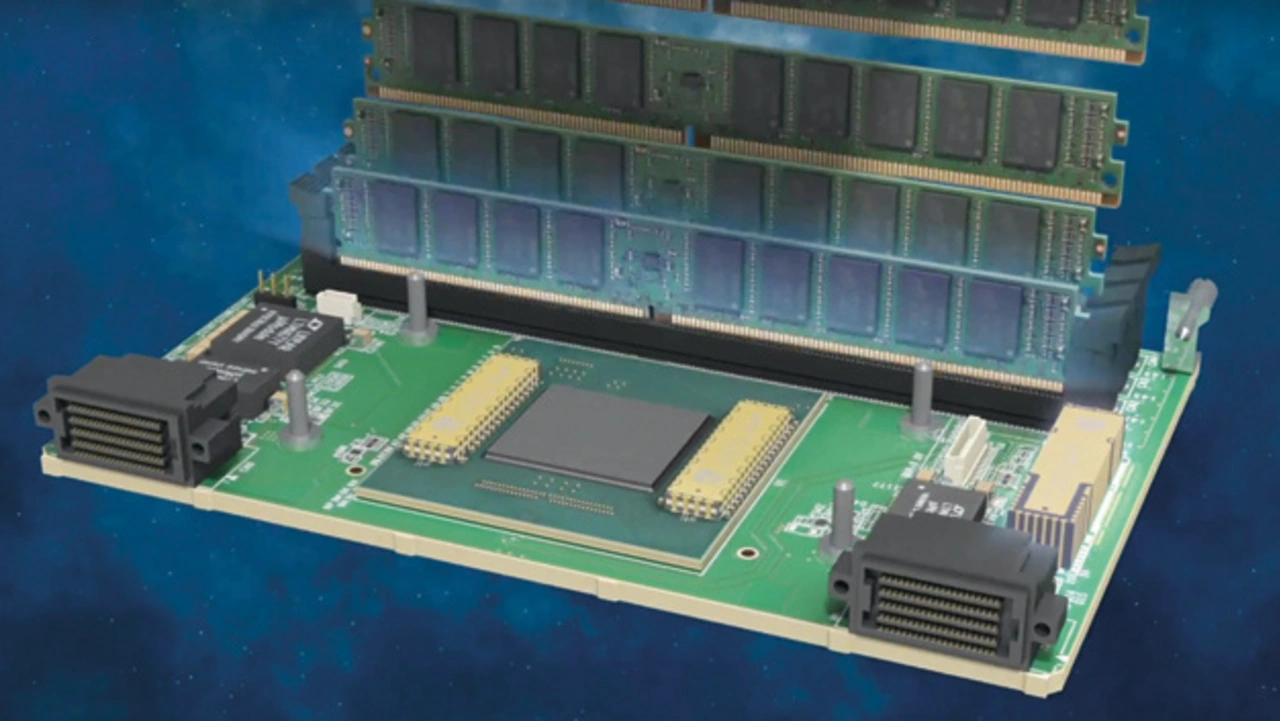

Um das MCM-Modul auf dem XPU-Substrat platzieren zu können, hat Vicor das SM-ChiP-Gehäuse entwickelt (Bild 4). Für dieses wurde die in den VI-Chip-Modulen verwendete Technik weiterentwickelt. Der SM-ChiP nutzt eine oberflächenmontierbare Konstruktion, deren Kontaktflächen einen sehr geringen Widerstand zum Substrat oder Motherboard aufweisen. Das Modul MCM3208S59Z01A6C00 hat eine Grundfläche von 32 mm x 8 mm und eine Höhe von 2,7 mm.

Zwei dieser Module liefern zweimal 160 A Dauerstrom oder zweimal 320 A Spitzenstrom. Versorgt werden diese Module von einem vorgeschalteten MCM-Treiber-Modul des Typs MCD3509S60E59D0C01 (35 mm x 9 mm x 4,9 mm) auf der Hauptplatine, das eine mittlere Leistung von 400 W und eine Spitzenleistung von 600 W liefert. Für noch höhere Ströme können Doppelmodule wie das MCM4608S59Z01B5T00 (46 mm x 8 mm x 2,7 mm) mit jeweils 300 A Dauer- bzw. 500 A Spitzenstrom genutzt werden.

Damit sind Spitzenströme bis zu 1 kA in einem System möglich. Der entsprechende MCM-Treiber MCD4609S60E59H0T00 (46 mm x 9 mm x 4,9 mm) wird auf dem Motherboard platziert und liefert eine durchschnittliche Leistung von 650 W mit Spitzen von bis zu 1000 W.

Power-on-Package in einem Petaflop-Supercomputer

Der Supercomputer Gyoukou ExaScaler/PEZY ZettaScaler-2.2 befindet sich am Forschungsinstitut JAMSTEC Yokohama in Japan. In einem Ranking der weltweit installierten Supercomputer stand er im November 2017 auf Position 5 der Top 500 bezüglich des Datendurchsatzes mit 19,1 PFlop/s, also 1015 Floating-Point-Rechenoperationen pro Sekunde). Mit 14,1 GFlops/W erreichte er außerdem Position 4 im Green 500 Ranking, das den Energiebedarf im Verhältnis zur Rechenleistung berücksichtigt.

Wie bei vielen Supercomputern ist das thermische Design ein Schlüsselfaktor bei der Systemarchitektur. In der Tauchkühlung befinden sich Prozessor-Cluster in mehreren Tanks. Darin zirkuliert eine elektrisch nicht leitende Kühlflüssigkeit, die die Wärme zu externen Wärmetauschern leitet. Jeder Tank enthält 256 Prozessoren mit 48 V Factorized Power Architecture, wobei die CPUs zusammen mit den PoP-MCMs von Vicor auf einem gemeinsamen Substrat angeordnert sind – für die direkte Strommultiplikation von 48 V auf unter 1 V.

Jeder Prozessor hat 2048 einzelne Kerne mit 1 GHz Taktfrequenz und einer Taktrate von 1 GHz und einem 3-Layer-Cache-Speicher auf dem Chip. Der Prozessor ist in einem Modul mit eigenem schnellen DDR4-Speicher untergebracht und der Leistungsbedarf beträgt 130 W. Auf einem Frame sitzen 32 Module und bilden einen Block, acht Blöcke sind in einem Tank, was eine Gesamtleistung von 33 kW bei 48 V pro Tank bedeutet. Insgesamt 26 dieser Tanks bilden das komplette System.

Die durch das Power-on-Package implementierte Factorized Power Architecture gewährleistet, dass der größtmögliche Anteil der durch den Computer verursachten Abwärme durch die Datenverarbeitung verursacht wird, während durch die komplette Stromversorgung nur geringe Verluste entstehen.

Der Autor

Robert Gendron

ist Corporate Vice President Marketing, Power Components bei Vicor. Davor übte er leitende Marketing- und Vertriebsfunktionen bei Halbleiterunternehmen wie Analog Devices, STMicroelectronics, Fairchild Semiconductor, International Rectifier und Volterra aus. Er ist Mitglied des Industrial Advisory Board des Department of Electrical and Computer Engineering an der University of New Hampshire. Gendron hat einen Bachelor of Science der Clarkson University in Elektrotechnik, einen Master of Science der Northeastern University in Elektrotechnik sowie einen Master of Business Administration der Whittemore School of Business (University of New Hampshire). Darüer hinaus ist er eingetragener Professional Enineer des Commonwealth of Massachusetts.