Systemdesign / Low-Power-Verifikation

Optimierte Leistungs- und Temperaturkompromisse

Fortsetzung des Artikels von Teil 2

Verwendung von Standardformaten

IEEE 1801/UPF ist ein IEEE-Standard, um die Leistungsvorgaben zu spezifizieren. Entweder mit einer separaten Datei über TCL-artige Befehle oder mittels Leistungsvorgaben, die direkt in die Hardware-Beschreibung über Sprachattribute und HDL-Packages geschrieben werden. Neben anderen Aspekten definiert dies die verschiedenen Versorgungsbereiche in einem Design. Die verschiedenen Tools - wie Simulation und Emulation - können IEEE 1801 nutzen, um die Anwender bei der Darstellung der Leistungsvorgaben zu unterstützen. Bei einem Design mit beispielsweise vier Versorgungsbereichen, von denen drei schaltbar sind und einer schaltbar ist aber auch Hoch- und Niedrigspannungszustände hat, muss der Anwender neun Basiszustände und 24 Betriebsarten prüfen.

Das kann mittels einer Simulation und Emulation erfolgen. Obwohl einige dieser Modi nicht logisch sind, lässt sich in Verbindung mit einigen Hundert oder sogar Tausend Funktionsprüfungen der Einfluss der Überlagerung von Low-Power-Problem und Verifikationsproblem verstehen. Es ist daher sehr wünschenswert, dass die rohe Rechenleistung der Emulation die Möglichkeiten der Simulation erweitert.

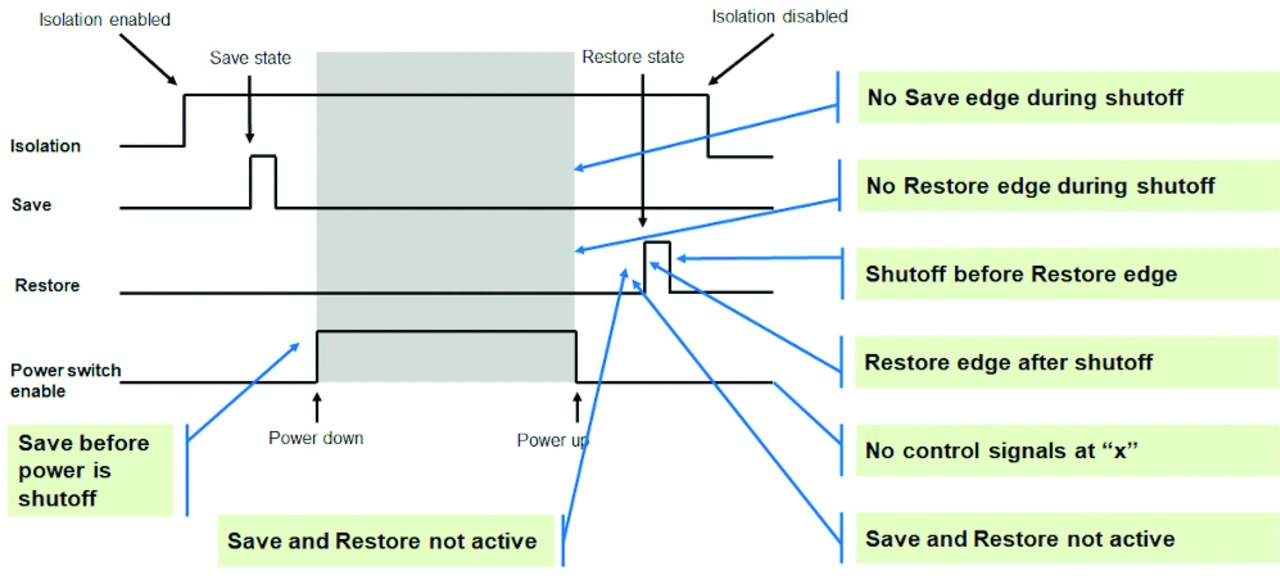

Eine typische Funktionsprüfung wird erweitert, um auch die Leistungssteuersignale zu umfassen. Für eine Verifikation der Leistungsabschaltung, zum Beispiel, beginnt die Sequenz mit Zyklen zur Isolierung, dann folgen die Statussicherung und schließlich die Leistungsabschaltung der Domäne. Bild 4 zeigt mehrere Prüfungen, die durchgeführt werden sollten.

Jobangebote+ passend zum Thema

Wenn die Emulationsunterstützung für IEEE 1801 evaluiert wird, empfiehlt es sich, die Fähigkeiten zu testen, die spezifische Implikationen für sie haben. Zum Beispiel eine Speicherverwürfelung während des Ein- und Ausschaltens, die Kontrolle über den Lesewert während des ausgeschalteten Zustands, die Statussicherung von nichtflüchtigem Speicher und das Einfrieren von Daten bei der Sicherung sind wichtig, um die Low-Power-Verifikation wiederholbar zu machen. Die Anwender sollten sich bewusst sein, dass in der Emulation ein Kapazitäts-Ooverhead von 10 bis 20 % bei einer IEEE 1801 gesteuerten Low-Power-Verifikation wegen der automatischen Einfügung von Logik für das Power-Domain-Management notwendig ist. Der Emulations-Workflow für die IEEE 1801-Leistungsverifikation in Palladium Z1 erfordert als einzige Änderung das Einbinden der IEEE 1801-Leistungsvorgabe-Datei während der Kompilation, der Rest des Flows läuft voll automatisiert.

Anwendererfahrung

Für die dynamische Leistungsanalyse wurde ein aktuelles Beispiel während der Cadence Anwenderkonferenz CDNLive im Silicon Valley von Theodore Wilson, Technical Lead for Architecture Co-Verification bei Microsemi unter dem Titel »Rapid Turns with Palladium and Joules« präsentiert [1]. Der Schlüsselparameter, der bei Microsemi versucht wurde zu optimieren, ist »Leistungsanalyse vs. Durchsatz - die Zeit von der Aktivitätsaufzeichnung zu ausführbaren Leistungsberichten«. Durch die Kombination der Palladium Z1 Emulation mit Joules- Leistungsabschätzungen konnte Microsemi die Ausführungen auf Gatter-Ebene durchführen, sobald das RTL funktionierte.

Andere Kunden, wie Texas Instruments, haben vorher über Ergebnisse von Emulations- bis zum Implementierungsfluss berichtet, die im Bereich von 96 % des erwarteten Stromumsatzes lagen. Durch die Ausführung längerer Läufe in der Emulation im Vergleich zur Simulation konnten unerwartete Leistungsbedingungen erkannt werden, weil das Design mit der realen Software für echte Anwendungsfall-Szenarios stimuliert wurde [2].

Samsung hat ebenfalls von seinen Erfahrungen hinsichtlich des Einflusses einer UPF 1801 basierten Leistungsoptimierung berichtet und dies während der CDNLive in Korea diskutiert, siehe »The Power of Big Iron« [3]. Mit nur einem geringen Overhead bei der Kompilierungszeit und Kapazität konnte Samsung die Laufzeiten der Tests um den Faktor 5 bis 32 verbessern. Dass Tests in einem Bruchteil der Zeit oder mehr Tests in derselben Zeit durchgeführt werden konnten, war schon immer ein Vorteil der Emulation. Jetzt ist auch die Low-Power-Verifikation ein bewährter Vorteil für die Anwender der Emulation. Eine leistungsorientierte Prüfung kann jetzt auch die Firmware- und Software-Verifikation umfassen, die zusammen mit der Hardware-Prüfung erfolgt. Diese Erweiterung ermöglicht mehr Fähigkeiten in der Optimierung der Leistungsarchitektur. Außerdem ermöglicht dies den Anwendern ein schnelleres Halbleiter-Bring-up im Zusammenhang einer angewandten Low-Power-Strategie.

Zusammenfassung und Ausblick

Die Low-Power-Analyse, Optimierung und Verifikation sind kritische Schritte während der Entwicklung von Elektronikbauteilen. Kleine Architekturänderungen früh in der Entwurfsphase können riesigen Einfluss auf den Stromumsatz des Endprodukts besonders im Zusammenhang mit der Hardware-/Software-Partitionierung haben. Die Verknüpfung von Aktivitätsinformationen, die auf RT-Ebene mit einer Low-Power-Charakterisierung auf Gatter- und Layout-Ebene mit .lib-Definitionen gesammelt wurden, erlaubt frühzeitige und genaue Schätzungen. Zudem lässt sich sogar der Einfluss der Software während der Ausführung von tiefen Emulationszyklen bewerten.

Künftig werden noch abstraktere Techniken vor der Verfügbarkeit von RTL zum Einsatz kommen - besonders Softwareentwickler erwarten immer größere Kompromisse zwischen Genauigkeit und Geschwindigkeit um Ergebnisse zu erhalten. Die vertikale Integration der Design-Flows in EDA (Electronic Design Automation) erfüllt diese Aufgabe!

Referenzen

[1] http://bit.ly/2J0Cspy

[2] http://bit.ly/2IXqVYk

[3] http://bit.ly/2JOXjgO

- Optimierte Leistungs- und Temperaturkompromisse

- Überbrückung von Abstraktionsebenen

- Verwendung von Standardformaten