Systemdesign / Low-Power-Verifikation

Optimierte Leistungs- und Temperaturkompromisse

Fortsetzung des Artikels von Teil 1

Überbrückung von Abstraktionsebenen

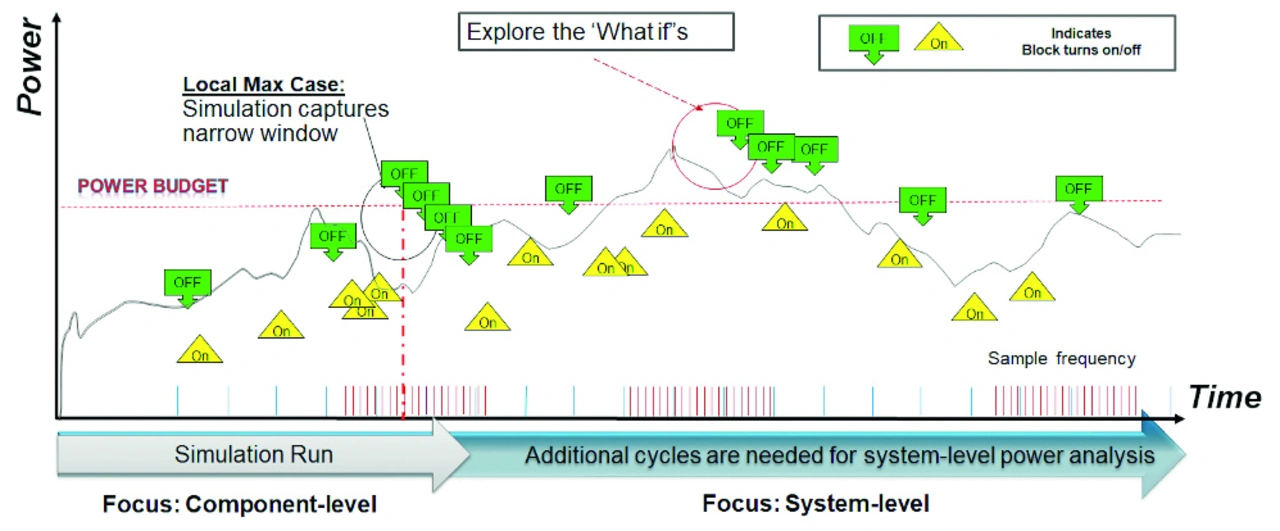

Bild 2 verdeutlicht, dass wenn nicht ausreichend Zyklen für ein Design, einschließlich der auf den Prozessoren laufenden Software, ausgeführt werden, der Anwender in einem lokalen Minimum stecken bleiben kann. Um den wirklichen Stromumsatz im ungünstigsten Fall zu finden, sind tiefe Zyklen erforderlich.

Jobangebote+ passend zum Thema

Durch eine Kombination von Emulation und einer Leistungsabschätzung auf RTL- oder Gatter-Ebene lassen sich heute Abstraktionsebenen verbinden. Mit einer Emulation, wie mit der Palladium Z1 Enterprise-Platform von Cadence, können die Anwender innerhalb einer relativ kurzen Zeit große Mengen von Aktivitätsdaten sammeln und diese mit den Implementierungs-Flows verbinden. Obwohl die Emulation eine Ausführung im MHz-Bereich erlaubt, während die Simulation im Hz-Bereich läuft, lässt sich eine Identifizierung der richtigen Hotspots am besten durch einen Beginn mit abstrakten, groben Aktivitätsinformationen erreichen. Dies sind die reinen Schaltvorgänge im Design, wobei jeder Vorgang zählt, um eine Abschätzung auf einer frühen Stufe zu erhalten.

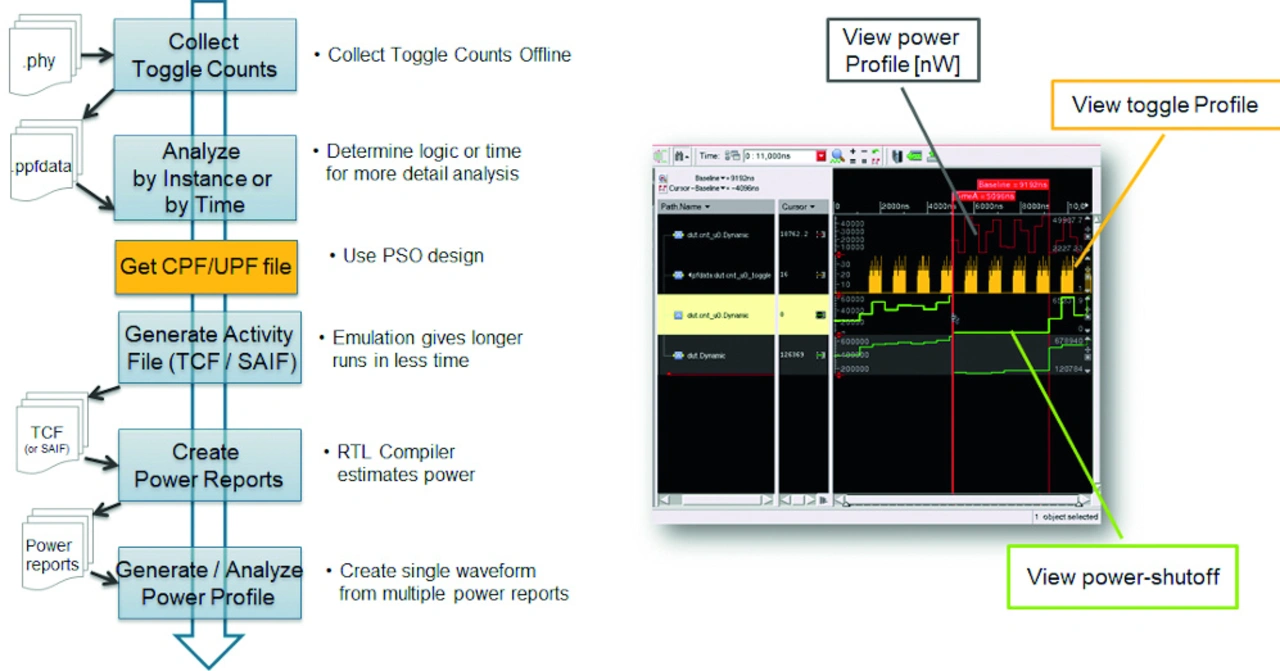

Nach der Verfeinerung des Interessenbereichs können gewichtete Schaltvorgänge genutzt werden. Dabei werden die verschiedenen Schaltungsknoten unterschiedlich gewichtet, so zählt zum Beispiel eine Write-Enable-Änderung eines Speichers mehr als eine Änderung an einem NAND-Gate-Eingang. Das ermöglicht eine höhere Genauigkeit. Schließlich kann die höchste Genauigkeit mit dem SAIF-Toggle-Count-Format mit feinkörniger Auflösung erreicht werden. Dieses Format kann dann von Leistungsberechnungs-Tools wie Joules-RTL-Power-Lösung von Cadence genutzt werden, die Low-Level-Technologie-Daten aus .lib-Definitionen berücksichtigen.

Der resultierende Flow sowie ein Beispiel einer Leistungsprofil-Debugging-Umgebung einschließlich einer Zählung der Schaltvorgänge und Visualisierung einer Leistungsabschaltung wird im Bild 3 dargestellt.

Die Design-Teams können dadurch die Leistungsoptimierung auf einen viel früheren Zeitpunkt im Design-Zyklus verschieben. Dies ist entweder durch eine Kombination von Aktivitätsdaten möglich, die aus der RTL-Ebene mit Abschätzungen des Stromumsatzes aus RTL mittels Technologie-Informationen aus .lib-Dateien abgeleitet wurden, oder durch die Verwendung von Aktivitätsinformationen, die aus der Gatterebene abgeleitet und denen entsprechende Leistungsinformationen zugeordnet werden, was direkt mit .lib-Dateien möglich ist. Das spart kostspielige Re-Designzyklen im Vergleich zu Leistungsproblemen, die erst spät erkannt und in einer späteren Stufe des Projekts korrigiert werden müssen. Dies erlaubt eine Leistungsoptimierung im Zusammenhang mit der Software, die auf den Prozessoren im Design läuft, was einen großen Einfluss auf den dynamischen Stromumsatz haben kann.

- Optimierte Leistungs- und Temperaturkompromisse

- Überbrückung von Abstraktionsebenen

- Verwendung von Standardformaten